Documente Academic

Documente Profesional

Documente Cultură

Overlap in Rectifiers Overlap in Rectifiers: Advance Power Electronics Advance Power Electronics

Încărcat de

Junaid AlviDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Overlap in Rectifiers Overlap in Rectifiers: Advance Power Electronics Advance Power Electronics

Încărcat de

Junaid AlviDrepturi de autor:

Formate disponibile

1/8/2012

Advance Power Electronics

Overlap in Rectifiers

LECTURE-8 LECTURE-

Dr. Tahir Izhar

Overlap

Introduction

The overlap is the effect of source impedance on rectifier characteristics. h t i ti The three pulse, or half wave three phase rectifier is considered here to explain the effect. It is not a practical circuit, but convenient to use it as a vehicle to explain the overlap . First the ideal behavior of this circuit is reviewed then the source impedance is included to investigate the overlap. If the load inductance is assumed to be infinite, the load current will be constant. If the source impedance is ignored, the current can commutate instantaneously form one diode to the next.

1/8/2012

Overlap

Introduction

The diode with the highest anode voltage will conduct at any instant i ti i t t in time, th th the three di d conduct f 120O each. diodes d t for h The load current is constant and contributed by each diode of 120O duration. The current in three phases starts and stops instantaneously. In practice, time is required for the currents to change due to p q g supply side source impedance. The major contributor of this impedance is leakage inductances of the transformer. The main reason for the unpopularity of the half bridge is that it draws DC current components form the mains which may lead to cause saturation in distribution transformer.

Ideal 3-Pulse Converter 3-

1/8/2012

Ideal 3-Pulse Converter 3The current through Ld is continuous, made up of the contributions from each diode of 120O duration. For the ideal case the currents can start and stop instantaneously. In practice, time is required for the current change to take place due to the supply source inductance. The major contributor to the supply inductance is the transformer leakage inductance.

Effect of Source Impedance

The circuit is modified to include the supply inductance. The phase currents iR, iY and iB can no longer start and stop instantaneously, but volt-second will be voltabsorbed in establishing and extinguishing the phase currents in Ls.

1/8/2012

Effect of Source Impedance

Effect of Source Impedance

This effect modifies the rectifier behavior in two significant ways: i t i ifi t

The mean output voltage, Vd is reduced and the harmonic components of Vo are modified. The harmonic components in supply current waveform are modified, mainly by the attenuation of the higher frequency components.

1/8/2012

Overlap Analysis

Consider commutation from DR to DY which will be initiated as VYN exceeds VRN. at time t0. This is the time when line voltage, VYR is passing through zero to become positive. To analyze the commutation events, the equivalent circuit is shown below.

Overlap Analysis

The voltage VYR drives the circulating current, iC in the direction shown. When iC reaches the value Id, iR will become zero and DR is extinguished and iY has become equal to Id and has taken over the conduction. The period when both diodes are conducting is called the overlap. It should be noted that

iR + iY = I d

diR di = Y dt dt

(1)

(2)

The equation governing the equivalent Circuit with assumed sign convention is

vYR = 2 LS

diC dt

(3)

1/8/2012

Overlap Analysis

LS diC vYR = dt 2

(4) Consequently vYR is responsible for supplying the volt-seconds which change the q y p pp y g g current in LS. Furthermore during the overlap time the output voltage, vo of the rectifier is:

vo = vYN

vYR 2

Where vYR /2 is the inductance LS drop as can be seen from the equivalent circuit during overlap.

v v vo = vYN YN RN 2 2 vYN vRN vo = vYN + 2 2 1 vo = (vRN + vYN ) 2

(5)

Overlap Analysis

Hence vo is the instantaneous average of the red and yellow phase voltages as y phase shown above and not the yellow p voltage for the ideal case when LS=0. Thus for the period up until t0, the output voltage vo has been equal to vRN. From t0 onwards vo becomes 1/2(vRN+vYN) until conduction has been transferred from red to yellow phase. After conduction transfer, vo will become vYN as before. Analytical A l i l expressions f the i for h instantaneous phase currents during overlap can be derived from equation (4) because iY=iC during this time. iY is initially zero, and rises according to iC when overlap starts.

1/8/2012

Overlap Analysis

iY = 1 vYR dt 2 LS 0

t

(6)

From equation (4) it can be seen that as t=0 at t0

iYR = 3vRN sin t

iY = 3vRN (1 cos t ) 2LS

(7) (8)

As from equation (1)

iR + iY = I d iR = I d iY iR = I d 3vRN (1 cos t ) 2LS

(9)

Equation (8) and (9) define the instantaneous currents during the overlap time

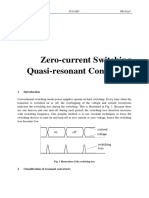

Overlap Analysis

These sinusoidal transitions replace the instantaneous switching from one diode to another that take place with zero source impedance. p g p The shape of vo is shown in the diagram. It follow VRN up to t0, then follow (vRN+vYN) during overlap and then recovered to vYN when t=T. The duration of the overlap can be derived from equation (8), because overlap finishes when iY=Id Hence

Id =

Therefore

3vRN (1 cos T ) 2LS

T=

2LS I d cos 1 1 3vRN 1

(10)

Equation (10) is not a simple expression, but nevertheless allows T to be calculated. The average output voltage, Vd is reduced because of the volt-second shown shaded in the figure.

1/8/2012

Overlap Analysis

That volt-second is absorbed voltacross the source impedance each time current commutates from one phase to another. The output voltage reduction due to overlap can be estimated form the waveform shown.

Vd = Vd VT

(11)

Where Vd is actual voltage, Vd is ideal voltage and VT is the loss of voltage due to overlap.

Overlap Analysis

The volt-seconds needed to change the current in the yellow phase inductance LS , from 0 to Id is clearly LSId. Hence

VT =

3LS I d T

(12)

Where the factor 3 is included because there are three overlap events in each period of Mains cycle, T.

T= VT =

1 2 = f

(13)

3LS Id 2

(14)

Finally, putting values in equation (4) gives

Vd =

3 3 3LS vRN Id 2 2

(15)

Equation (15) suggest an equivalent circuit as shown

1/8/2012

Overlap Analysis

The half bridge rectifier is viewed as a DC source of value

Vd =

3 3 vRN 2

(16)

With in internal source resistance of

RC =

3LS 2

(17)

It should be noted that there is not loss associated with RC. This model only applies when the overlap condition prevails.

Summary

In this lecture, the effect of source impedance on the performance of the rectifier circuit is investigated. The inductive reactance of the ac supply is normally much greater than its resistance. Due to the source inductance, time is required to change the current resulting a delay in current commutation. Three pulse half bridge circuit with source inductance is used to explain the phenomenon of overlap overlap. Once the overlap phenomenon is understood, it can be applied to other practical converter circuits.

1/8/2012

Thank you

For your attention

10

S-ar putea să vă placă și

- ManualDocument11 paginiManualLoveÎncă nu există evaluări

- Eee Lab Report 8Document9 paginiEee Lab Report 8Sayeed MohammedÎncă nu există evaluări

- Buck and Boost Converters With Transmission LinesDocument8 paginiBuck and Boost Converters With Transmission LinesVisu TamilÎncă nu există evaluări

- Abstract:: IookhzDocument6 paginiAbstract:: Iookhzvebond8Încă nu există evaluări

- Buck Converter: 1 Theory of OperationDocument11 paginiBuck Converter: 1 Theory of OperationYugendra RÎncă nu există evaluări

- RHPZ, A Two Way Control PathDocument11 paginiRHPZ, A Two Way Control PathkurabyqldÎncă nu există evaluări

- Buck ConverterDocument8 paginiBuck Converterhamza abdo mohamoudÎncă nu există evaluări

- High Voltage Lecture 8Document16 paginiHigh Voltage Lecture 8Clinton OnyangoÎncă nu există evaluări

- Electric Circuits: DC, Ac Power Systems Electrical Machines Drives SystemsDocument36 paginiElectric Circuits: DC, Ac Power Systems Electrical Machines Drives SystemsMatthew 'moka' BlandÎncă nu există evaluări

- Laporan Boost AisDocument20 paginiLaporan Boost Aisdedy SetyoÎncă nu există evaluări

- Low Voltage Fara TrafDocument8 paginiLow Voltage Fara TraftyutyuÎncă nu există evaluări

- UNIT-1: Lecture Notes Unit 1: Transient AnalysisDocument36 paginiUNIT-1: Lecture Notes Unit 1: Transient AnalysisRamalingeswar JÎncă nu există evaluări

- CHP 1: Circuit TheoryDocument42 paginiCHP 1: Circuit TheoryjojoÎncă nu există evaluări

- RL Circuit (Physics Majors) 02 02-2017Document11 paginiRL Circuit (Physics Majors) 02 02-2017Weuler CostaÎncă nu există evaluări

- Switching Losses PDFDocument4 paginiSwitching Losses PDFleonardo_arévalo_28Încă nu există evaluări

- Analysis, Design and Implementation of An Active Clamp Flyback Converter PDFDocument6 paginiAnalysis, Design and Implementation of An Active Clamp Flyback Converter PDFDeniz UzelÎncă nu există evaluări

- Lecture 02Document21 paginiLecture 02Abd El-Rahman DabbishÎncă nu există evaluări

- Analysis of Zero-Voltage Transition Fourth-Order Buck ConverterDocument6 paginiAnalysis of Zero-Voltage Transition Fourth-Order Buck ConverterFairuz ZabadiÎncă nu există evaluări

- On The Ringdown Transient of TransformersDocument6 paginiOn The Ringdown Transient of TransformersCarlos Lino Rojas AgüeroÎncă nu există evaluări

- Module-Iii Syllabus:: Transient Behavior and Initial Conditions: Behavior of Circuit Elements Under SwitchingDocument32 paginiModule-Iii Syllabus:: Transient Behavior and Initial Conditions: Behavior of Circuit Elements Under Switchinglohith sÎncă nu există evaluări

- AC-DC Converters PDFDocument9 paginiAC-DC Converters PDFrizwan100% (1)

- ZCS NoteDocument20 paginiZCS NoteMohammad AbabnehÎncă nu există evaluări

- MIT8 02SC Notes25Document42 paginiMIT8 02SC Notes25asdf12322Încă nu există evaluări

- Ee 211Document37 paginiEe 211Muhammad OsamaÎncă nu există evaluări

- Chapter2 - AC To DC ConvertersDocument36 paginiChapter2 - AC To DC ConvertersYee Yen AppleÎncă nu există evaluări

- AEI Power Module 3 NoteDocument35 paginiAEI Power Module 3 NoteNandu JagguÎncă nu există evaluări

- 1 Circuit Theory - MZMDocument47 pagini1 Circuit Theory - MZMSyahmi AkmalÎncă nu există evaluări

- Memo #M3 Voltage Scaling and Limits To Energy Eciency For CMOS-based SCRL Working Draft Revision: 1.27Document19 paginiMemo #M3 Voltage Scaling and Limits To Energy Eciency For CMOS-based SCRL Working Draft Revision: 1.27Ronak MotaÎncă nu există evaluări

- 10 InductanceDocument16 pagini10 InductanceAde Nur HidayatÎncă nu există evaluări

- Analysis, Optimized Design and Adaptive Control of A ZCS Full-Bridge Converter Without Voltage Over-Stress On The SwitchesDocument8 paginiAnalysis, Optimized Design and Adaptive Control of A ZCS Full-Bridge Converter Without Voltage Over-Stress On The SwitchesArun PrakashÎncă nu există evaluări

- Rectifying CircuitsDocument13 paginiRectifying Circuitssina981Încă nu există evaluări

- RC and RL Circuits - FRDocument23 paginiRC and RL Circuits - FRIshtiyaq RafiqiÎncă nu există evaluări

- PWM DC-DC: Two-Switch Forward Soft-Switching Power ConverterDocument2 paginiPWM DC-DC: Two-Switch Forward Soft-Switching Power ConverterSweatha SajeevÎncă nu există evaluări

- EG1108 RectifiersDocument14 paginiEG1108 RectifiersEunicePeñaflorÎncă nu există evaluări

- Notes 1 - Transmission Line TheoryDocument82 paginiNotes 1 - Transmission Line TheoryMaraMendozaÎncă nu există evaluări

- Electrical Essential Network Paper 2010Document4 paginiElectrical Essential Network Paper 2010Rameez AliÎncă nu există evaluări

- Small-Signal Analysis of Open-Loop PWM Flyback DCDC Converter For CCMDocument8 paginiSmall-Signal Analysis of Open-Loop PWM Flyback DCDC Converter For CCMAshok KumarÎncă nu există evaluări

- Em Oscill ADocument12 paginiEm Oscill Aaditya66605Încă nu există evaluări

- Soft SwitchingDocument6 paginiSoft SwitchingR.k. Rahul KumarÎncă nu există evaluări

- Public A CaoDocument23 paginiPublic A CaoShaheer DurraniÎncă nu există evaluări

- Ch07 STDDocument41 paginiCh07 STDMeenakshi SundaramÎncă nu există evaluări

- Asymmetrical Full-Bridge ConverterDocument9 paginiAsymmetrical Full-Bridge ConverterAthiesh KumarÎncă nu există evaluări

- 03 Diode Rectifier ProjectDocument11 pagini03 Diode Rectifier ProjectManju NathÎncă nu există evaluări

- Unit Iv - Multivibrator CircuitsDocument29 paginiUnit Iv - Multivibrator CircuitsAshwini SaravannavarÎncă nu există evaluări

- Effect of Output Capacitor ESR On Dynamic Performance of Voltage-Mode Hysteretic Controlled Buck ConverterDocument2 paginiEffect of Output Capacitor ESR On Dynamic Performance of Voltage-Mode Hysteretic Controlled Buck ConverterKrismadinataÎncă nu există evaluări

- PSIM MANUAL For StudentsDocument23 paginiPSIM MANUAL For StudentsSomnath Khamaru75% (4)

- Relation Between V and V in Continuous Conduction: EE462L, Power Electronics, DC-DC Buck ConverterDocument16 paginiRelation Between V and V in Continuous Conduction: EE462L, Power Electronics, DC-DC Buck Converterbill gatesÎncă nu există evaluări

- Ac LabDocument6 paginiAc LabJohnCarloTigueÎncă nu există evaluări

- Chapter 3 Diode CircuitsDocument45 paginiChapter 3 Diode CircuitsMuhammad DhiyauddinÎncă nu există evaluări

- Interleaved Boost Converter For Photovoltaic Power-GenerationDocument11 paginiInterleaved Boost Converter For Photovoltaic Power-GenerationRihab HamdiÎncă nu există evaluări

- Pee Lab ManualDocument77 paginiPee Lab ManualRajendraTuraka100% (1)

- EE 435 SCR Notes3Document32 paginiEE 435 SCR Notes3Dado GaudiÎncă nu există evaluări

- Lecture 1Document23 paginiLecture 1KESHAV JHAÎncă nu există evaluări

- Experiment 1Document7 paginiExperiment 1Clement RajÎncă nu există evaluări

- ECL NotesDocument57 paginiECL Notesvamsee007Încă nu există evaluări

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterDe la EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterÎncă nu există evaluări

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1De la EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Încă nu există evaluări

- Cognitive, Affective, and Psychomotor Domains GradingDocument4 paginiCognitive, Affective, and Psychomotor Domains GradingJunaid AlviÎncă nu există evaluări

- Serial No Name of Colony Owoner/Project Developer Rate Per Marla Sizes of Plots Date of CommencementDocument1 paginăSerial No Name of Colony Owoner/Project Developer Rate Per Marla Sizes of Plots Date of CommencementJunaid AlviÎncă nu există evaluări

- 480 Al Ramadhan PDFDocument6 pagini480 Al Ramadhan PDFJunaid AlviÎncă nu există evaluări

- Sir Kashif Chapter 2Document83 paginiSir Kashif Chapter 2Junaid AlviÎncă nu există evaluări

- Sir Kashif Chapter 1Document33 paginiSir Kashif Chapter 1Junaid AlviÎncă nu există evaluări

- Line To Ground Voltage Monitoring On Ungrounded and Impedance Grounded Power SystemsDocument16 paginiLine To Ground Voltage Monitoring On Ungrounded and Impedance Grounded Power SystemsJunaid AlviÎncă nu există evaluări

- Forge-Data LogDocument295 paginiForge-Data LogDonnieÎncă nu există evaluări

- 1532748281262Document31 pagini1532748281262FranciscoÎncă nu există evaluări

- It - Mega - Courses 1Document13 paginiIt - Mega - Courses 1Telt100% (4)

- Mathematical Induction: CS/APMA 202 Rosen Section 3.3 Aaron BloomfieldDocument43 paginiMathematical Induction: CS/APMA 202 Rosen Section 3.3 Aaron BloomfieldJovit Rejas AleriaÎncă nu există evaluări

- Sending Output of Concurrent Programs Via EmailDocument1 paginăSending Output of Concurrent Programs Via EmailAshish HarbhajankaÎncă nu există evaluări

- Power Control (RAN16.0 01)Document295 paginiPower Control (RAN16.0 01)hekriÎncă nu există evaluări

- Md. Shahid Uz Zaman Dept. of CSE, RUETDocument18 paginiMd. Shahid Uz Zaman Dept. of CSE, RUETJarir AhmedÎncă nu există evaluări

- Mdia5003 2022 T3Document10 paginiMdia5003 2022 T3Sehrish MushtaqÎncă nu există evaluări

- CSE 211: Data Structures Lecture Notes I: Ender Ozcan, Şebnem BaydereDocument11 paginiCSE 211: Data Structures Lecture Notes I: Ender Ozcan, Şebnem Baydereapi-3705606Încă nu există evaluări

- Ververica Platform Whitepaper Stream Processing For Real-Time Business, Powered by Apache Flink®Document22 paginiVerverica Platform Whitepaper Stream Processing For Real-Time Business, Powered by Apache Flink®pinoÎncă nu există evaluări

- Cable Design User GuideDocument84 paginiCable Design User GuidelumagbasÎncă nu există evaluări

- Spectra System PumpsDocument2 paginiSpectra System PumpsAna JurkeviciuteÎncă nu există evaluări

- Serial Number Word 2010Document1 paginăSerial Number Word 2010Akhmad Yusuf SulaimanÎncă nu există evaluări

- Epicor University - Advanced Business Process Management Course PDFDocument54 paginiEpicor University - Advanced Business Process Management Course PDFgvdaniel stpÎncă nu există evaluări

- Esc101: Fundamental of Computing: I Semester 2008-09Document17 paginiEsc101: Fundamental of Computing: I Semester 2008-09arjunÎncă nu există evaluări

- Transformer or Transformerless Ups (2003) (Koffler)Document3 paginiTransformer or Transformerless Ups (2003) (Koffler)mapo mfaÎncă nu există evaluări

- Xillybus Product BriefDocument2 paginiXillybus Product Briefraiatea2Încă nu există evaluări

- Digital Twins - The Key To Smart Product Development - McKinseyDocument11 paginiDigital Twins - The Key To Smart Product Development - McKinseyRogerÎncă nu există evaluări

- Training Contents - WebmethodsDocument6 paginiTraining Contents - WebmethodsShyamini Dhinesh0% (1)

- BPL Mom FileDocument2 paginiBPL Mom FileArun KumarÎncă nu există evaluări

- When Data Visualization Works - and When It Doesn'tDocument8 paginiWhen Data Visualization Works - and When It Doesn'tronald johannÎncă nu există evaluări

- 12 Best Practices For Core Banking MigrationDocument9 pagini12 Best Practices For Core Banking MigrationitouzenÎncă nu există evaluări

- Zoning Brocade Switches-Creatng ConfigurationsDocument2 paginiZoning Brocade Switches-Creatng ConfigurationsKirankumar RajaÎncă nu există evaluări

- Installation Minerva t1016rDocument20 paginiInstallation Minerva t1016rIsabelle Del Pilar75% (4)

- Pearson Edexcel Free Login - Google SearchDocument1 paginăPearson Edexcel Free Login - Google SearchmaverickwacleahÎncă nu există evaluări

- Codding Tugas Akhir DPK 1Document2 paginiCodding Tugas Akhir DPK 1Nicco ComputerÎncă nu există evaluări

- IELTS Practice Test 12 Writing AcDocument9 paginiIELTS Practice Test 12 Writing Achoward blaineÎncă nu există evaluări

- Mphasis Data 10.4.19Document5 paginiMphasis Data 10.4.19Vyshnavi ThottempudiÎncă nu există evaluări

- Batch ManagementDocument11 paginiBatch ManagementMadhusmita PradhanÎncă nu există evaluări