Documente Academic

Documente Profesional

Documente Cultură

8255

Încărcat de

Manjula BnDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

8255

Încărcat de

Manjula BnDrepturi de autor:

Formate disponibile

PROGRAMMABLE PERIPHERAL INTERFACE 8255 The 8255 is a PPI which is used for parallel data T/f.

It has three 8-bit ports 1. PORT A 2. PORT B 3. PORT C which are arranged in two groups. It can be programmed to operate in three modes: Mode 0, Mode 1, Mode 2. Each port has a unique address, and data can be read from or written to a port, by issuing either an IN or OUT instruction. Operational Modes: Mode 0: Basic Input/output In this mode, port A and port B can be configured as simple 8-bit input or output ports without handshaking. The two halves of port C, PC0 -PC3 and PC4 PC7 can be programmed separately as 4-bit input or output ports. Mode 1: Strobed Input/output: In this mode, two groups each of 12 pins are formed

Ports A and B can be programmed as 8-bit I/O ports with three lines of Port C in each group used for hand shaking. Mode 2: Strobed Bidirectional Bus I/O: This mode allows Bidirectional data T/f over a single 8-bit data bus using handshaking signal. Only Port A can be used as bidirectional port. The hand shaking signals are provided on five lines of port C (PC3 PC7). Port B can be used in Mode 0 or in Mode1. Bit Set Reset future: In addition to the above modes, individual bits of port C can be set or reset by sending out a single OUT inst. to the control register.

Data Bus Buffer: The tristate bi-directional buffer is used to inter face the 8255 to the system data bus. IN or OUT inst. executed by the CPU are to either read data form, or write data into the Buffer. Control Logic: The control logic block accepts control bus signals as well as i/ps from the address bus, and issues commands to the individual group control blocks.

Group A and Group B controls: Each of the group A and group B control Blocks receivers control words from the CPU through the data Buffer and internal data bus, accepts commands from control block, and issues appropriate commands to the ports associated with it.

8255 Programming and Operation: A high on the RESET pin causes all 24 points of three 8-bit ports to be in the input mode. The ports are then programmed for any other mode by sending out a single inst. (OUT) to the control register. Also, the mode can be specified. There are two basic modes of operation

Bit set/Reset format Control word

The control words for both mode definition and Bit Set-reset are loaded into the same control register with bit D7 for specifying whether it is mode definition word or Bit setReset word. Example for BSR Mode: If bit PC2 is to be set, then control reg. would be 0XXX0101 If bit PC7 is to be Reset, then control reg. would be 0XXX1110. 8255 PROGRAMMING Mode 0: In the control word, D7 is set to 1. D6, D5, D2: 0 [to configure all the ports in Mode 0] D4, D3, D1, D0: determine whether the corresponding ports are configured as I/P or O/P For example, If Port A, Port B: I/P ports : D4=1 D1=1 PCL: O/P: D0=0 PCU: I/P: D3=1

Mode 1: ( Strobed input/output mode ) In this mode the handshaking control the input and output action of the specified port. Port C lines PC0-PC2, provide strobe or handshake lines for port B. This group which includes port B and PC0-PC2 is called as group B for Strobed datainput/output. Port C lines PC3-PC5 provides strobe lines for port A. This group including port A and PC3-PC5 from group A. Thus port C is utilized for generating handshake signals. Two groups group A and group B are available for strobed data transfer. Each group contains one 8-bit data I/O port and one 4-bit control/data port. The 8-bit data port can be either used as input and output port. The inputs and outputs both are latched. Out of 8-bit port C, PC0PC2 are used to generate control signals for port B and PC3-PC5 are used to generate control signals for port A. the lines PC6, PC7 may be used as independent data lines. The control signals for both the groups in input and output modes are explained as follows: Input control signal definitions (mode 1 ): STB( Strobe input ) If this lines falls to logic low level, the data available at 8-bit input port is loaded into input latches. IBF ( Input buffer full ) If this signal rises to logic 1, it indicates that data has been loaded into latches, i.e. it works as an acknowledgement. IBF is set by a low on STB and is reset by the rising edge of RD input. INTR ( Interrupt request ) This active high output signal can be used to interrupt the CPU whenever an input device requests the service. INTR is set by a high STB pin and a high at IBF pin. INTE is an internal flag that can be controlled by the bit set/reset mode of either PC4(INTEA) or PC2(INTEB) as shown in fig. Output control signal definitions (mode 1) : OBF (Output buffer full) This status signal, whenever falls to low, indicates that CPU has written data to the specified output port. The OBF flip-flop will be set by arising edge of WR signal and reset by a low going edge at the ACK input. ACK ( Acknowledge input ) ACK signal acts as an acknowledgement to be given by an output device. ACK signal, whenever low, informs the CPU that the data transferred by the CPU to the output device through the port is received by the output device. INTR ( Interrupt request ) Thus an output signal that can be used to interrupt the CPU when an output device acknowledges the data received from the CPU. INTR is set when ACK, OBF and INTE are 1. It is reset by a falling edge on WR input. The INTEA and INTEB flags are controlled by the bit set-reset mode of PC6 and PC2 respectively.

Mode 2 ( Strobed bidirectional I/O ): This mode of operation of 8255 is also called as strobed bidirectional I/O. This mode of operation provides 8255 with an additional features for communicating with a peripheral device on an 8-bit data bus. Handshaking signals are provided to maintain proper data flow and synchronizationbetween the data transmitter and receiver. The interrupt generation and other functions are similar to mode 1.

Control signal definitions in mode 2:

INTR (Interrupt request) As in mode 1, this control signal is active high and is used to interrupt the microprocessor to ask for transfer of the next data byte to/from it. This signal is used for input ( read ) as well as output ( write ) operations. Control Signals for Output operations: OBF ( Output buffer full ) This signal, when falls to low level, indicates that the CPU has written data to port A. ACK ( Acknowledge ) This control input, when falls to logic low level, acknowledges that the previous data byte is received by the destination and next byte may be sent by the processor. This signal enables the internal tristate buffers to send the next data byte on port A. INTE1 ( A flag associated with OBF ) This can be controlled by bit set/reset mode with PC6.

Control signals for input operations : STB (Strobe input ) A low on this line is used to strobe in the data into the input latches of 8255. IBF ( Input buffer full ) When the data is loaded into input buffer, this signal rises to logic 1. This can be used as an acknowledge that the data has been received by the receiver. The waveforms in fig show the operation in Mode 2 for output as well as input port.

INTERFACING ANALOG TO DIGITAL DATA CONVERTERS: The ADC is treated as an input device by the microprocessor that starts an initializing signal to ADC to start the conversion process. The start of conversion signal is a pulse of a specific duration. The process of analog to dig. Conversion is a slow process and the up has to wait for the dig. Data till the conversion is over. After the conversion is over, the ADC sends end of conversion (EOC) signal to inform the up about it and the result is ready at the O/P buffer of ADC. These tasks of issuing an SOC pulse to ADC, reading EOC signal from the ADC and reading the dig. The CPU using 8255 I/O ports carries out O/P of the ADC. The time taken by the converter to calculate the equivalent digital data o/p from the moment of the SOC is called conversion delay. Successive Approximation ADC and dual slope ADC Techniques are popular.

Whatever may be the technique for conversion, a general algorithm for ADC interfacing contains the following steps. 1. Ensure the stability of analog I/P. 2. Issue start of conversion (SOC) pulse to ADC 3. Read EOC (end of conversion) signal 4. Read digital data o/p of the ADC. Pin Diagram of ADC 0808/0809:

ADD A, B, C are Address lines for selecting analog i/ps. SOC: Start of conversion EOC: End of conversion I/P0-I/P7: Analog i/ps D0-D7: 8-bit Digital o/p OE: Output latch enable pin Vref+and Vref: Reference voltage positive and negative.

Timing Diagram of ADC 0808:

Prob: Interface ADC 0808 with 8086 using 8255 ports. Use port A of 8255 for transferring digital data o/p of ADC to the CPU and port C for control signals. Assume that an analog I/P is present at I/P2 of the ADC and a clock i/p of suitable frequency is available for ADC. Draw the schematic and write required ALP. Sol: Port A: 8-bit I/P data port (for digital data from ADC) Port C Lower: SOC: o/p port Port C Upper: EOC: I/P port Port B: o/p port (for giving I/P2) Status of ADD. A B C 0 1 0 Control Word:

INTERFACING DIGITAL TO ANALOG CONVERTERS: The D to A converters convert binary no. into their analog equivalent voltages. DAC 0800 8-bit DAC:

Problem: Write an ALP to generate a triangular wave of frequency 500 Hz using the interfacing ckt shown in fig. below. The 8086 system operates at 8MHz. The amplitude of the triangular wave should be +5V. Sol:Port A: o/p Digital data to DAC. Only port A is used, so the remaining ports are configured as o/ps.

Note: The technique of interfacing 12-bit DACs is also similar. If 8-bit ports are used, two successive 8-bit OUT instructions are required to apply i/p to DAC.

STEPPER MOTOR INTER FACING: A stepper motor is a device used to obtain an accurate position control of Rotating shafts. It employs rotation in terms of steps, rather than continuous rotation as in case of AC or DC motors. To rotate the shaft, a sequence of pulses is needed to be applied to the windings. The no. of pulses required for one complete rotation of the shaft are equal to its no. of internal teeth on its Rotor. The Stator teeth and Rotor teeth Lock each other to fix a position of the shaft. With a pulse applied to the winding i/p, the rotor position rotates by an angle x. 360 x No.of Rotor teetch The internal schematic of a stepper motor has four windings. (wa,wb,wc,wd) Binary level pulses of 0.5 V are required at its winding inputs to obtain the rotation of shafts. fig

A simple scheme for rotating the shaft of a stepper motor is called wave scheme. In this scheme, voltage pulses are applied to windings in a cyclic fashion. By reversing it, the direction of rotation is reversed.

Another scheme of stepper motor applies two pulses to two successive windings at a time.

Problem: Design a stepper motor and write an ALP to rotate shaft of 4-phase stepper motor. i) in clock wise 5 rotations ii) in Anti clock wise 5 rotations The port A address is 0740H. The stepper motor has 200 rotor teeth. The port A0 drives winding wa, PA1 drives winding wb and soon. It has an internal delay of 10 msec. Sol: Data segment CWR EQU - - Port A EQU 0740 H Data Ends Code Segment Assume CS: code, DS: data Start: MOV AX, data MOV DS, AX MOV AL, 88 H; Bit pattern 10001000 to start MOV CX, 1000; 200 Rotor teeth. No. of Rotation * teeth = count Count = 200*5 = OUT Port A, AL CALL Delay ROR AL, 01

L1:

DEC CX JNZ L1 MOV AH, 88 H, MOV CX, 1000 L2= OUT Port A, AH CALL DELAY ROL AH, 01 DEC CX JNZ L2 HLT Code Ends End Start Code 1 Segment Delay PROC FAR Assume CS: code 1, DS: Data HERE: MOV CX, OFFF H LOOP HERE Delay ENDP Code 1 ends KEY BOARD INTER FACING: Pressing a key is nothing but activating a switch. There are many types of switches. Mechanical key switches Membrane key switches Capacitive key switches Hall effect key switches In most key boards, the key switches are connected in a matrix of Rows and Columns. We will use simple mechanical switches here, but the principle is same for all the switches. Process: 1. Detect a key press. 2. De bounce the key press 3. Encode the key press. A Logic 0 is read by the micro processor when the key is pressed. Key De bounce: Whenever a mechanical push-button is pressed or released once, the mechanical components of the key do not change the position smoothly, rather it generates a transient response as shown in fig. These may be interpreted as the multiple key pressures and responded accordingly.

To avoid this problem, two schemes are suggested: 1. Uses of Bistable Multi vibrator at the o/p of the key to debounce it. 2. The up has to wait for the transient period (at least for 10 ms), so that the transient response settles down and reaches a steady state The rows of the matrix are connected to four output port lines, and columns are connected to four input port lines. When no keys are pressed, the column lines are held high by the pull-up resistors connected to +5V. Pressing a key connects a row and a column. To detect if any key is pressed is to output 0s to all rows and then check columns to see if a pressed key has connected a low to a column. (Check until all the columns are high).

Once the columns are found to be all high, the program enters another loop, which waits until a low appears on one of the columns. (Indicating a key press). For this a simple 20 m.s delay is executed to de bounce task. After the de bounce time, another check is made to see if the key is still pressed. If the columns are now all high, then no key is pressed and the initial detection was caused by a Noise pulse.

If any of the columns are low now, then the assumption is made that it was a valid key press. The final task is to determine the row and column of the pressed key and convert this inf. to hex code for the pressed key. For this, a low is given to rows and now column is read. If none of the columns is low, the pressed key is not in that row, so the low is rotated to next row and repeat again. This is repeated until a low on a row produces a low on one of the columns. Therefore, the 4-bit code from i/p port (ROW) and the 4-bit code from o/p port (column) are converted to Hex code. This ENCODE portion uses a compare technique. This is done with the LOOK UP table containing 8-bit key pressed codes for 16-keys.

Program: Data Segment 1 2 3 4 Table DB 0 77H , 7 BH, 7 DH , 7 EH OB7 H 5 6 7 8 OBBH, OBDH, OBEH, OD7 H D E B OEBH, OEDH, OEEH, Data Ends Code Segment Assume, CS: code, DS: Data, SS: Stack-seg Start: MOV AX, data MOV DS, AX ;Initialize ports pot A: output (Mode 0) Port C, Port B: I/P

MOV AL, 8 BH OUT CWR, AL CALL Key Board NOP Key board PROC Near PUSH F PUSH BX PUSH CX PUSH DX

Wait open:

Wait-press:

IN AL, Port B AND AL, OF H; Mask Row bits CMP AL, OF H (All bits should be high at beg.) JNE Wait-open IN AL, Port B

Note: The concept o detecting some error condition such as no match found is called Error Trapping. Error may result when two keys were pressed at exactly same time, the decrement cyclecompare would continue through 65,536 memory locations.

1. 2. 3. 4.

EXERCISE Explain the control word format of 8255 in I/O and BSR mode. Write a program to print message-This is a printer test routine.to a printer using 8255 port initialised in mode1. Interface a typical 12-bit DAC with 8255 and write a program to generate a triangular waveform of period 10ms. The CPU runs at 5MHz clock frequency. Write ALPs to rotate a 200 teeth, 4 phase stepper motor specified below. a) five rotations clockwise and five rotations anticlockwise. b) rotate through angle 1350 in 2sec.

c) rotate the shaft at a speed of 10 rotations per minute. 5. Draw a typical stepper motor interface with 8255. 6. Using a typical 12-bit DAC generate a step waveform of duration 1 sec, maximum voltage 3 volts and determine duration of each step suitably. Multiple-choice questions 1. How many ports do 8255 have? A. 3 C. 5 B. 4 D. 6

2. How many modes do 8255 have? A. 3 C. 5 B. 4 D. 6

3. Which of the following mode of 8255 is Strobed Bi-directional I/O? A. Mode 0 C. Mode 2 B. Mode 1 D. Mode 4

4. Which of the following port can be programmed nibble wise (separately)? A. Port A C. Port C B. Port B D. Port D

5. Port A and lower nibble of Port C come under ____ Group. A. A C. C B. B D. None

6. What is the status of A1A0 during an input read or output write operation with port B? A 00 C. 10 B. 01 D. 11

7. In BSR (bit set reset) mode, individual bits of port C can be accessed. A. True B. False

8. What is the purpose of B3B2B1 bits of control word in mode 0(BSR mode)? A. For BSR mode or I/O modes C. For port C B. for port B D. for port C lower

9. What is the purpose of B6B5 bits of control word in mode 0(I/O mode)? A. For BSR mode or I/O modes C. For port C upper B. for port A D. for port C lower

10. What is the status of port bit if it is configured as an output port? A0 C. 10 B. 1 D. 11

10. Give the control word address if port C lower bit is to be configured as input Port, port A as an output port in mode 0 and port B is not used in I/O mode? A. 80H C. 87H B. 81H D. 07H

11. Which of the following circuit is utilized for debouncing a key? A. Timer B. Monostable multivibrator C. Bistable multivibrator D. All 12. What type of control signal is IBF in mode 1? A. Input C. Input/Output B. output D. None

13. Which type of ADC is faster? A. Counter type B. Comparator type C. Successive approximation type

D. All 14. The ADC is treated as an________ device by the microprocessor. A. Input C. Input/Output B. output D. None

15. The time taken by the ADC from active edge of SOC pulse till the active edge of EOC signal is called __________. A. Cross talk C. Clock skew B. propagation delay D. conversion delay

16. How many reference voltages for a DAC? A. 1 C. 2 B. 4 D. 3

17. Which of the following pin of ADC tells us the status of EOC to microprocessor? A. INTA C. RD B. INTR D. WR

18. The microprocessor reads the digital data from ADC by making RD pin to______. A. HIGH C. HIGH-Z B. LOW D. LOW-Z

19. How do we activate ADC (i.e. through___ pin)? A. INTA C. RD B. INTR D. WR

20. Trigger (0 to 1 pulse) signal is given to ____ pin of ADC. A. INTA C. RD B. INTR D. WR

21. How do we observe the output of DAC when interfaced to microprocessor? A. Through CRO B. through LCD

C. Through spectrum Analyzer

D. Both A & C

22. The DAC is treated as an________ device by the microprocessor. A. Input C. Input/Output B. output D. None

23. How many ports are needed when DAC is interfaced to microprocessor? A. 1 C. 2 B. 4 D. 3

24. Configure the control word of 8255 by using PORT A for digital output of DAC? (Dont use remaining ports) A. 99H C. 88H B. 80H D. 82H

25. How many control signals are needed for DAC interfacing? A. 1 C. 2 B. 4 D. Nil

26. Which of the following chips is used for DAC operation? A. 0804 C. 0807 B. 0805 D. 0808

27. The rotor position rotates by an angle x expressed as______ A. 3600 / No. of rotor teeth B. 1800 / No. of rotor teeth C. 3600 / No. of turns D. 1800 / No. of turns 28. A simple scheme for rotating the shaft of a stepper motor is called _________. A. Stepping scheme B. Rotation scheme

C. Wing scheme

D. Wave scheme

29. How many windings are present in internal schematic of a stepper motor? A. 1 C. 2 B. 4 D. Nil

30. What is the circuit used for a proper debounce? A. Flip flop C. Bistable multivibrator Answers: 1. A 2. A 3. C 4. C 5. D 6. B 7. A 8. D 9. B 10. B 11. C 12. A 13. C 14. A 15. C 16. C 17. B B. Amplifier D. Nil

18. B 19. D 20. D 21. D 22. B 23. A 24. B 25. D 26. D 27. A 28. D 29. B 30. C

S-ar putea să vă placă și

- Ilovepdf MergedDocument430 paginiIlovepdf MergedYuvraj ChhabraÎncă nu există evaluări

- 8255 Ppi ExamplesDocument10 pagini8255 Ppi Examplesvenky258100% (1)

- Block Diagram of 8255 WITH ExplanationDocument8 paginiBlock Diagram of 8255 WITH Explanationsenthilkumar100% (2)

- 8279 Keyboard and Display ControllerDocument33 pagini8279 Keyboard and Display Controllergutzz0079197100% (1)

- Mpi 11002Document21 paginiMpi 11002alkesh.eng0% (1)

- Keyboard I 8051Document3 paginiKeyboard I 8051sachinshymÎncă nu există evaluări

- Data Handling Analog Io Selection of PLCDocument14 paginiData Handling Analog Io Selection of PLCnkchandruÎncă nu există evaluări

- 8251 UsartDocument24 pagini8251 UsartNava KrishnanÎncă nu există evaluări

- Microcontrollers 8051 Input Output PortsDocument2 paginiMicrocontrollers 8051 Input Output PortsrajeshÎncă nu există evaluări

- TMS320F2812-Serial Communication InterfaceDocument28 paginiTMS320F2812-Serial Communication InterfacePantech ProLabs India Pvt Ltd75% (4)

- Interfacing Programs For 8085Document37 paginiInterfacing Programs For 8085archankumarturagaÎncă nu există evaluări

- Low Power Uart DeviceDocument19 paginiLow Power Uart DeviceparnabmasterÎncă nu există evaluări

- Universal Asynchronous Receiver Transmitter (UART)Document38 paginiUniversal Asynchronous Receiver Transmitter (UART)Chandresh Trivedi100% (1)

- Adc0808 and 8253Document35 paginiAdc0808 and 8253Avanish NiranjanÎncă nu există evaluări

- 8096 MicrocontrollerDocument51 pagini8096 MicrocontrollerNarasimha Murthy Yayavaram67% (3)

- 8251A USART - Programmable Communication InterfaceDocument15 pagini8251A USART - Programmable Communication InterfaceselvaÎncă nu există evaluări

- RP Jain Adc DacDocument27 paginiRP Jain Adc DacAnand SinghÎncă nu există evaluări

- PIC Timer 0 Calculation ExampleDocument3 paginiPIC Timer 0 Calculation Examplef.last100% (1)

- How To Interfacing Sensor With LPC2148 ARMDocument8 paginiHow To Interfacing Sensor With LPC2148 ARMSubir MaityÎncă nu există evaluări

- 4) PIC IO Port ProgrammingDocument18 pagini4) PIC IO Port ProgrammingArryshah Dahmia100% (2)

- CD20 Serial Control Rev4Document6 paginiCD20 Serial Control Rev480quattroÎncă nu există evaluări

- Using The MSSP Module To Interface Spi™ Serial Eeproms With Pic18 DevicesDocument12 paginiUsing The MSSP Module To Interface Spi™ Serial Eeproms With Pic18 Deviceskraneak100% (3)

- The D Flip FlopDocument7 paginiThe D Flip FlopAlinChanÎncă nu există evaluări

- Interfacing 8255Document13 paginiInterfacing 8255S SIVAKUMAR0% (1)

- Coprocessor 1Document50 paginiCoprocessor 1chandanayadav8490Încă nu există evaluări

- Adc Lab Pic18Document23 paginiAdc Lab Pic18Bolarinwa Joseph100% (1)

- Unit 4 COADocument30 paginiUnit 4 COAVighnesh SarwankarÎncă nu există evaluări

- Interfacing Analog To Digital Data ConvertersDocument16 paginiInterfacing Analog To Digital Data ConvertersPrabin123Încă nu există evaluări

- Programming The MCU 8051 PDFDocument48 paginiProgramming The MCU 8051 PDFDK White LionÎncă nu există evaluări

- Interfacing Hex Keypad To 8051.Document5 paginiInterfacing Hex Keypad To 8051.RejinÎncă nu există evaluări

- ARM Organization and Implementation: Aleksandar MilenkovicDocument37 paginiARM Organization and Implementation: Aleksandar Milenkovicarthicse100% (1)

- 8255Document32 pagini8255tameromar1971Încă nu există evaluări

- Solution For All Problems in Chapter 9Document3 paginiSolution For All Problems in Chapter 9Rahmat Hidayat100% (1)

- 8254 Programmable Interval TimerDocument4 pagini8254 Programmable Interval Timerapi-26100966100% (1)

- 8051 Interfacing With Display SevicesDocument5 pagini8051 Interfacing With Display Sevicesramjee26100% (1)

- Dspa 17ec751 M5Document34 paginiDspa 17ec751 M5digital loveÎncă nu există evaluări

- Assembler Language - 8051powerpoint PresentationDocument56 paginiAssembler Language - 8051powerpoint PresentationtauseeeeeeeeÎncă nu există evaluări

- ADC Program For LPC2138Document8 paginiADC Program For LPC2138hypernuclide100% (1)

- Working Priciple of Keypad and Its InterfacingDocument9 paginiWorking Priciple of Keypad and Its InterfacingGiani Kumar50% (2)

- Accident Detection and Alert System Based On ARM7 MicrocontrollerDocument4 paginiAccident Detection and Alert System Based On ARM7 MicrocontrollersophiyasharanÎncă nu există evaluări

- x64 AsmDocument4 paginix64 Asmasdmin100% (1)

- D 1295042413Document4 paginiD 1295042413Norbert DeakÎncă nu există evaluări

- Experiment 09 Interfacing Keypad and LCD With PIC18F452 ObjectiveDocument11 paginiExperiment 09 Interfacing Keypad and LCD With PIC18F452 Objectivehira NawazÎncă nu există evaluări

- 8051 Interview QuestionsDocument8 pagini8051 Interview QuestionsSudheer ReddyÎncă nu există evaluări

- Timer 0Document2 paginiTimer 0andres felipe100% (1)

- Ch17 Spi Protocol and Max7221 Display InterfacingDocument51 paginiCh17 Spi Protocol and Max7221 Display InterfacingSimple knowledgeÎncă nu există evaluări

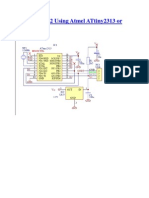

- USB To RS232 Using Atmel ATtiny2313 or ATmega8Document4 paginiUSB To RS232 Using Atmel ATtiny2313 or ATmega8Nugraha Indrawan100% (2)

- Experiment 10 Analog-to-Digital Converter (ADC) in PIC18F452 ObjectiveDocument10 paginiExperiment 10 Analog-to-Digital Converter (ADC) in PIC18F452 Objectivehira Nawaz100% (1)

- The Programmable Keyboard Display Interface - 8279Document23 paginiThe Programmable Keyboard Display Interface - 8279Pranav MpÎncă nu există evaluări

- SST89e51 Programming ManualDocument9 paginiSST89e51 Programming Manualrudra_150% (2)

- LCD 16 X 2Document9 paginiLCD 16 X 2Pradeev Balakrishnan100% (1)

- Adc0808 and 8253Document35 paginiAdc0808 and 8253Avanish NiranjanÎncă nu există evaluări

- Traffic Light ControllerDocument16 paginiTraffic Light ControllerJoshua Jebaraj JosephÎncă nu există evaluări

- PWMDocument57 paginiPWMAhmed Mortuza Saleque SaikotÎncă nu există evaluări

- Analog PLCsDocument25 paginiAnalog PLCsgogetss420100% (1)

- UARTDocument34 paginiUARTMohit Dayal67% (3)

- Adc Pic18f452Document8 paginiAdc Pic18f452Muhammad Ummair100% (1)

- CISE414 - Unit 04 AVR Atmega PortsDocument30 paginiCISE414 - Unit 04 AVR Atmega Portsمحمد حمدÎncă nu există evaluări

- Mpmcnotesunit IIIDocument34 paginiMpmcnotesunit IIIAmy OliverÎncă nu există evaluări

- Unit 3 - Peripheral InterfacingDocument56 paginiUnit 3 - Peripheral InterfacingSathiyarajÎncă nu există evaluări

- Our School Broke Up For The Winter VacationsDocument7 paginiOur School Broke Up For The Winter VacationsprinceÎncă nu există evaluări

- Lecture On Metallurgical BalancesDocument14 paginiLecture On Metallurgical BalancesVladimir LopezÎncă nu există evaluări

- Criteria For Decorative Cosmetics PDFDocument3 paginiCriteria For Decorative Cosmetics PDFsamudra540Încă nu există evaluări

- Speaking With Confidence: Chapter Objectives: Chapter OutlineDocument12 paginiSpeaking With Confidence: Chapter Objectives: Chapter OutlinehassanÎncă nu există evaluări

- BJ SurfactantsDocument2 paginiBJ SurfactantsAquiles Carrera100% (2)

- Aakash Zoology Study Package 3 SolutionsssssssDocument104 paginiAakash Zoology Study Package 3 SolutionsssssssRishika PaulÎncă nu există evaluări

- Underground-Sprayed Concrete BrochureDocument12 paginiUnderground-Sprayed Concrete BrochureEngTamerÎncă nu există evaluări

- Septage Management Guide 1Document43 paginiSeptage Management Guide 1Ria Tiglao FortugalizaÎncă nu există evaluări

- B.ing Wajib - XI IPA1-2Document3 paginiB.ing Wajib - XI IPA1-2iwan fals NurjaniÎncă nu există evaluări

- Lisca - Lingerie Catalog II Autumn Winter 2013Document76 paginiLisca - Lingerie Catalog II Autumn Winter 2013OvidiuÎncă nu există evaluări

- Pid 14 MT23 160412Document20 paginiPid 14 MT23 160412Amol ChavanÎncă nu există evaluări

- Agriculture Budget 2013-14Document33 paginiAgriculture Budget 2013-14Ajay LimbasiyaÎncă nu există evaluări

- Detailed Lesson Plan in Science Grade 10Document9 paginiDetailed Lesson Plan in Science Grade 10christian josh magtarayoÎncă nu există evaluări

- Gexcon DDT Scotts PresentationDocument33 paginiGexcon DDT Scotts PresentationMochamad SafarudinÎncă nu există evaluări

- AGPT04I-09 Guide To Pavement Technology Part 4I Earthworks MaterialsDocument47 paginiAGPT04I-09 Guide To Pavement Technology Part 4I Earthworks MaterialsLeandroÎncă nu există evaluări

- Teiaiel - Visions of The FutureDocument2 paginiTeiaiel - Visions of The FutureMarkosÎncă nu există evaluări

- Interference Measurement SOP v1.2 Sum PDFDocument26 paginiInterference Measurement SOP v1.2 Sum PDFTeofilo FloresÎncă nu există evaluări

- Wanderer Above The Sea of FogDocument5 paginiWanderer Above The Sea of FogMaria Angelika BughaoÎncă nu există evaluări

- Hydraulics - MKM - DLX - Parts - Catalogue MAR 14 PDFDocument33 paginiHydraulics - MKM - DLX - Parts - Catalogue MAR 14 PDFRS Rajib sarkerÎncă nu există evaluări

- NCERT Class 7 English Part 1 PDFDocument157 paginiNCERT Class 7 English Part 1 PDFVvs SadanÎncă nu există evaluări

- Autodesk Inventor Practice Part DrawingsDocument25 paginiAutodesk Inventor Practice Part DrawingsCiprian Fratila100% (1)

- Practice Test 1 + 2Document19 paginiPractice Test 1 + 2yếnÎncă nu există evaluări

- 2022 Specimen Paper 1 Mark Scheme 1Document4 pagini2022 Specimen Paper 1 Mark Scheme 1Herman HermanÎncă nu există evaluări

- Apexification Using Different Approaches - Case Series Report With A Brief Literature ReviewDocument12 paginiApexification Using Different Approaches - Case Series Report With A Brief Literature ReviewIJAR JOURNALÎncă nu există evaluări

- Digital DividesDocument25 paginiDigital DividesKumaraswamy ChannabasaiahÎncă nu există evaluări

- Lesson 3.1 Algebraic TermsDocument4 paginiLesson 3.1 Algebraic TermsCresencia Juliana DaluzÎncă nu există evaluări

- Daitoumaru and Panstar GenieDocument41 paginiDaitoumaru and Panstar GeniePedroÎncă nu există evaluări

- What Is Kpag?: Table of ContentsDocument2 paginiWhat Is Kpag?: Table of Contentsangelito bernalÎncă nu există evaluări

- International SubcontractingDocument2 paginiInternational SubcontractingCatherine JohnsonÎncă nu există evaluări

- Designing New Vanillin Schiff Bases and Their Antibacterial StudiesDocument4 paginiDesigning New Vanillin Schiff Bases and Their Antibacterial StudiesAvinash PurohitÎncă nu există evaluări