Documente Academic

Documente Profesional

Documente Cultură

VLSI Physical Design: From Graph Partitioning To Timing Closure

Încărcat de

kamarajvlsiTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

VLSI Physical Design: From Graph Partitioning To Timing Closure

Încărcat de

kamarajvlsiDrepturi de autor:

Formate disponibile

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

1

Chapter 1 Introduction

Original Authors:

Andrew B. Kahng, Jens Lienig, Igor L. Markov, Jin Hu

VLSI Physical Design: From Graph Partitioning to Timing Closure

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

2

Chapter 1 Introduction

1.1 Electronic Design Automation (EDA)

1.2 VLSI Design Flow

1.3 VLSI Design Styles

1.4 Layout Layers and Design Rules

1.5 Physical Design Optimizations

1.6 Algorithms and Complexity

1.7 Graph Theory Terminology

1.8 Common EDA Terminology

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

3

1.1 Electronic Design Automation (EDA)

Moores Law

In 1965, Gordon Moore (Fairchild)

stated that the number of

transistors on an IC would double

every year. 10 years later, he

revised his statement, asserting

that they double every 18 months.

Since then, this rule has been

famously known as Moores Law.

M

o

o

r

e

:

C

r

a

m

m

i

n

g

m

o

r

e

c

o

m

p

o

n

e

n

t

s

o

n

t

o

i

n

t

e

g

r

a

t

e

d

c

i

r

c

u

i

t

s

"

E

l

e

c

t

r

o

n

i

c

s

,

V

o

l

.

3

8

,

N

o

.

8

,

1

9

6

5

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

4

15.7

20.3 19.4

26.3

32.9

44.9

29.5

39.8

25.2

32.6

27.0

36.9

16.9

23.1

31.7

43.5

29.6

40.7

56.4

79.0

33.6

46.7

31.1

42.5

27.2

35.2

34.0

46.6

21.4

29.4

40.5

55.7

0.0

20.0

40.0

60.0

80.0

100.0

120.0

2009 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 2021 2022 2023 2024

ITRS 2009 Cost Chart

(in Millions of Dollars)

Total HW Engineering Costs + EDA Tool Costs Total SW Engineering Costs + ESDA Tool Costs

15.7

20.3 19.4

26.3

32.9

44.9

29.5

39.8

25.2

32.6

27.0

36.9

16.9

23.1

31.7

43.5

29.6

40.7

56.4

79.0

33.6

46.7

31.1

42.5

27.2

35.2

34.0

46.6

21.4

29.4

40.5

55.7

0.0

20.0

40.0

60.0

80.0

100.0

120.0

2009 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 2021 2022 2023 2024

ITRS 2009 Cost Chart

(in Millions of Dollars)

Total HW Engineering Costs + EDA Tool Costs Total SW Engineering Costs + ESDA Tool Costs

15.7

20.3 19.4

26.3

32.9

44.9

29.5

39.8

25.2

32.6

27.0

36.9

16.9

23.1

31.7

43.5

29.6

40.7

56.4

79.0

33.6

46.7

31.1

42.5

27.2

35.2

34.0

46.6

21.4

29.4

40.5

55.7

0.0

20.0

40.0

60.0

80.0

100.0

120.0

2009 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 2021 2022 2023 2024

ITRS 2009 Cost Chart

(in Millions of Dollars)

Total HW Engineering Costs + EDA Tool Costs Total SW Engineering Costs + ESDA Tool Costs

1.1 Electronic Design Automation (EDA)

Impact of EDA technologies on

overall IC design productivity and

IC design cost

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

5

1.1 Electronic Design Automation (EDA)

Design for Manufacturability (DFM), optical proximity correction

(OPC), and other techniques emerge at the design-manufacturing

interface. Increased reusability of blocks, including intellectual

property (IP) blocks.

2000 - now

First over-the-cell routing, first 3D and multilayer placement and

routing techniques developed. Automated circuit synthesis and

routability-oriented design become dominant. Start of parallelizing

workloads. Emergence of physical synthesis.

1990 -2000

First performance-driven tools and parallel optimization algorithms

for layout; better understanding of underlying theory (graph theory,

solution complexity, etc.).

1985 -1990

More advanced tools for ICs and PCBs, with more sophisticated

algorithms.

1975 -1985

Layout editors, e.g., place and route tools, first developed for

printed circuit boards.

1965 -1975

Manual design only. 1950 -1965

Circuit and Physical Design Process Advancements Time Period

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

6

1.2 VLSI Design Flow

ENTITY test is

port a: in bit;

end ENTITY test;

DRC

LVS

ERC

Circuit Design

Functional Design

and Logic Design

Physical Design

Physical Verification

and Signoff

Fabrication

System Specification

Architectural Design

Chip

Packaging and Testing

Chip Planning

Placement

Signal Routing

Partitioning

Timing Closure

Clock Tree Synthesis

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

7

1.3 VLSI Design Styles

Layer Palette

Mouse Buttons Bar

Layout Windows

Drawing Tools

Cell Browser

Status Bar

Toolbar Menu Bar

Text Windows

Layout editor

Locator

2

0

1

1

S

p

r

i

n

g

e

r

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

8

1.3 VLSI Design Styles

Common digital cells

IN OUT

0 1

1 0

1 0

1 1

OR INV NOR NAND AND

IN1 IN2 OUT

0 0 0

1 0 0

0 1 0

1 1 1

IN1 IN2 OUT

0 0 0

1 0 1

0 1 1

1 1 1

IN1 IN2 OUT

0 0 1

1 0 0

0 1 0

1 1 0

IN1 IN2 OUT

0 0 1

1 0 1

0 1 1

1 1 0

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

9

1.3 VLSI Design Styles

Vdd

GND

OUT

IN2

IN1

OUT

IN2

IN1

OUT

IN1

Vdd

GND

IN2

Contact

Diffusion layer

p-type

transistor

n-type

transistor

Metal layer

Poly layer

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

10

1.3 VLSI Design Styles

Power (Vdd)-Rail

Ground (GND)-Rail

Contact

Vdd

GND

OUT

IN2

IN1

OUT

IN2

IN1

OUT

IN1

Vdd

GND

IN2

Diffusion layer

p-type

transistor

n-type

transistor

Metal layer

Poly layer

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

11

1.3 VLSI Design Styles

Standard cell layout with

a feedthrough cell

A

GND

Feedthrough

Cell

Pad

Ground

Pad

Routing

Channel

Standard

Cells

Power

Pad

GND

Pad

Ground

Pad

Standard

Cells

Power

Pad

A

A

A

VDD VDD

Standard cell layout using

over-the-cell (OTC routing

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

12

1.3 VLSI Design Styles

Layout with macro cells

Pad

GND

PLA

RAM

Standard Cell

Block

RAM

PLA

Routing Regions

VDD

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

13

1.3 VLSI Design Styles

Field-programmable gate

array (FPGA)

LB LB LB

SB SB

LB LB LB

SB SB

LB LB LB

LB LB LB

SB SB

LB LB LB

SB SB

LB LB LB

LB LB

SB SB

LB LB LB

SB SB

LB LB LB

Logic Element

Switchbox

LB

Connection

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

14

1.4 Layout Layers and Design Rules

Layout layers of an inverter cell

with external connections

Contact

Metal1

polysilicon

p/n diffusion

Vdd

GND

Via

Metal2

Inverter Cell

External

Connections

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

15

1.4 Layout Layers and Design Rules

- Size rules, such as minimum width: The dimensions of any component (shape),

e.g., length of a boundary edge or area of the shape, cannot be smaller than given

minimum values. These values vary across different metal layers.

- Separation rules, such as minimum separation: Two shapes, either on the same

layer or on adjacent layers, must be a minimum (rectilinear or Euclidean diagonal)

distance apart.

- Overlap rules, such as minimum overlap: Two connected shapes on adjacent layers

must have a certain amount of overlap due to inaccuracy of mask alignment to

previously-made patterns on the wafer.

Categories of design rules

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

16

1.4 Layout Layers and Design Rules

Categories of design rules

Minimum Width: a

Minimum Separation: b, c, d

Minimum Overlap: e

a

d

c

b

e

: smallest meaningful technology-

dependent unit of length

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

17

1.5 Physical Design Optimizations

- Technology constraints enable fabrication for a specific technology node and are

derived from technology restrictions. Examples include minimum layout widths and

spacing values between layout shapes.

- Electrical constraints ensure the desired electrical behavior of the design. Examples

include meeting maximum timing constraints for signal delay and staying below

maximum coupling capacitances.

- Geometry (design methodology) constraints are introduced to reduce the overall

complexity of the design process. Examples include the use of preferred wiring

directions during routing, and the placement of standard cells in rows.

Types of constraints

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

18

1.6 Algorithms and Complexity

- Runtime complexity: the time required by the algorithm to complete as a function of

some natural measure of the problem size, allows comparing the scalability of various

algorithms

- Complexity is represented in an asymptotic sense, with respect to the input size n,

using big-Oh notation or O()

- Runtime t(n) is order f (n), written as t(n) = O(f (n)) when

where k is a real number

- Example: t(n) = 7n! + n

2

+ 100, then t(n) = O(n!)

because n! is the fastest growing term as n .

Runtime complexity

k

n f

n t

n

=

) (

) (

lim

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

19

1.6 Algorithms and Complexity

- Example: Exhaustively Enumerating All Placement Possibilities

Given: n cells

Task: find a single-row placement of n cells with minimum total wirelength by using

exhaustive enumeration.

Solution: The solution space consists of n! placement options. If generating and

evaluating the wirelength of each possible placement solution takes 1 s and

n = 20, the total time needed to find an optimal solution would be 77,147 years!

- A number of physical design problems have best-known algorithm complexities that

grow exponentially with n, e.g., O(n!), O(n

n

), and O(2

n

).

- Many of these problems are NP-hard (NP: non-deterministic polynomial time)

No known algorithms can ensure, in a time-efficient manner, globally optimal solution

Heuristic algorithms are used to find near-optimal solutions

Runtime complexity

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

20

1.6 Algorithms and Complexity

- Deterministic: All decisions made by the algorithm are repeatable, i.e., not random.

One example of a deterministic heuristic is Dijkstras shortest path algorithm.

- Stochastic: Some decisions made by the algorithm are made randomly, e.g., using a

pseudo-random number generator. Thus, two independent runs of the algorithm will

produce two different solutions with high probability. One example of a stochastic

algorithm is simulated annealing.

- In terms of structure, a heuristic algorithm can be

Constructive: The heuristic starts with an initial, incomplete (partial) solution and

adds components until a complete solution is obtained.

Iterative: The heuristic starts with a complete solution and repeatedly improves the

current solution until a preset termination criterion is reached.

Heuristic algorithms

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

21

1.6 Algorithms and Complexity

Heuristic algorithms

Constructive Algorithm

Iterative Improvement

no

yes

Termination

Criterion Met?

Return Best-Seen Solution

Problem Instance

Initial Solution

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

22

1.7 Graph Theory Terminology

Graph Hypergraph Multigraph

a

b

c

d

e

f

g

b

e

d

a

c

f

a

b

c

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

23

1.7 Graph Theory Terminology

Directed graphs with cycles Directed acyclic graph

c

a

b d

e

f

g

a b

c

a

b d

e

f

g

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

24

1.7 Graph Theory Terminology

Undirected graph with maximum node degree 3 Directed tree

a

b

c

d

e

f

g

a

b c

d

e

f

g

h i j k

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

25

1.7 Graph Theory Terminology

Rectilinear minimum spanning

tree (RMST)

Rectilinear Steiner minimum

tree (RSMT)

b (2,6)

a (2,1)

c (6,4) c (6,4)

Steiner point

b (2,6)

a (2,1)

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

26

1.8 Common EDA Terminology

Netlist

a

b

x

y

z c N

1

N

2

N

3

N

4

(a: N

1

)

(b: N

2

)

(c: N

5

)

(x: IN1 N

1

, IN2 N

2

, OUT N

3

)

(y: IN1 N

1

, IN2 N

2

, OUT N

4

)

(z: IN1 N

3

, IN2 N

4

, OUT N

5

)

(N

1

: a, x.IN1, y.IN1)

(N

2

: b, x.IN2, y.IN2)

(N

3

: x.OUT, z.IN1)

(N

4

: y.OUT, z.IN2)

(N

5

: z.OUT, c)

Pin-Oriented Netlist Net-Oriented Netlist

N

5

2

0

1

1

S

p

r

i

n

g

e

r

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

27

1.8 Common EDA Terminology

Connectivity graph

a

b

x

y

z c N

1

N

2

N

3

N

4

N

5

a

b

x

y

z c

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

28

1.8 Common EDA Terminology

Connectivity matrix

a

b

x

y

z c N

1

N

2

N

3

N

4

N

5

0 1 0 0 0 0 c

1 0 1 1 0 0 z

0 1 0 2 1 1 y

0 1 2 0 1 1 x

0 0 1 1 0 0 b

0 0 1 1 0 0 a

c z y x b a

2

0

1

1

S

p

r

i

n

g

e

r

V

e

r

l

a

g

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

29

1.8 Common EDA Terminology

n

n n

y y x x d

1 2 1 2

+ =

Distance metric between two points P

1

(x

1

,y

1

) and P

2

(x

2

,y

2

)

P

1

(2,4)

P

2

(6,1)

d

M

= 7

1 2 1 2 2 1

) , ( y y x x P P d

M

+ =

d

M

= 7

with n = 2: Euclidean distance

n = 1: Manhattan distance

d

E

= 5

2

1 2

2

1 2 2 1

) ( ) ( ) , ( y y x x P P d

E

+ =

VLSI Physical Design: From Graph Partitioning to Timing Closure Chapter 1: Introduction

K

L

M

H

L

i e

n

i g

30

Summary of Chapter 1

- IC production experienced huge growth since the 1960s

Exponential decrease in transistor size, cost per transistor, power per transistor, etc

- IC design is impossible without simplification and automation

Row-based standard-cell layout with design rules

Traditionally, each step in the VLSI design flow has been automated separately by

software (CAD) tools

- Software tools use sophisticated algorithms

Many problems in physical design are NP-hard solved by heuristic algorithms that

find near-optimal solutions

Deterministic versus stochastic algorithms

Constructive algorithms versus iterative improvement

Graph algorithms deal with circuit connectivity

Computational geometry deal with circuit layout

S-ar putea să vă placă și

- ISA101 - Human Machine Interfaces For Process Automation SystemsDocument31 paginiISA101 - Human Machine Interfaces For Process Automation SystemsRonald FloresÎncă nu există evaluări

- Schumann Piano Concerto in A Minor Op 54 SM PDFDocument101 paginiSchumann Piano Concerto in A Minor Op 54 SM PDFMKGUÎncă nu există evaluări

- IC Custom Layout DesignDocument10 paginiIC Custom Layout DesignSuresh KumarÎncă nu există evaluări

- VLSI Design Questions With AnswersDocument5 paginiVLSI Design Questions With Answersmani_vlsi100% (4)

- Chap1 111206Document30 paginiChap1 111206manojpeehu100% (1)

- Global Routing: VLSI Physical Design: From Graph Partitioning To Timing ClosureDocument101 paginiGlobal Routing: VLSI Physical Design: From Graph Partitioning To Timing Closureamma4manuÎncă nu există evaluări

- Inverter LayoutDocument22 paginiInverter LayoutPriyal PatelÎncă nu există evaluări

- Vlsi Question BankDocument14 paginiVlsi Question BankGokila Vani50% (2)

- AVLSI 11-07-22 IntroductionDocument26 paginiAVLSI 11-07-22 IntroductionJallapally sai chandanaÎncă nu există evaluări

- VLSI Design ProcessDocument20 paginiVLSI Design ProcessSisay ADÎncă nu există evaluări

- Layout Design RuleDocument71 paginiLayout Design RuleSuja Ganesan100% (7)

- Lec 2Document59 paginiLec 2何習與Încă nu există evaluări

- Course Information SheetDocument3 paginiCourse Information SheetKameshSontiÎncă nu există evaluări

- Micro WindDocument14 paginiMicro Windlak_prabÎncă nu există evaluări

- VLSI Design Lab NewDocument45 paginiVLSI Design Lab NewmtariqanwarÎncă nu există evaluări

- Vlsi Design - Ec - 701 - Unit - IDocument37 paginiVlsi Design - Ec - 701 - Unit - Iangelcrystl4774Încă nu există evaluări

- Effect of Increasing Chip DensityDocument30 paginiEffect of Increasing Chip DensityAhmad KhalidÎncă nu există evaluări

- VLSI Design NotesDocument69 paginiVLSI Design NotesPragnan Chakravorty100% (1)

- Circuit and PD Challenges at The 14nm Technology NodeDocument2 paginiCircuit and PD Challenges at The 14nm Technology NodeswethaswsankÎncă nu există evaluări

- Cad Asic Extra QuestionDocument18 paginiCad Asic Extra QuestionDin_skyDÎncă nu există evaluări

- Computer-Based Project in VLSI Design Co 3/7Document14 paginiComputer-Based Project in VLSI Design Co 3/7Naresh LakhaniÎncă nu există evaluări

- IR Drop AnalysisDocument9 paginiIR Drop AnalysisRohith Raj100% (1)

- ScalingDocument32 paginiScalingNK NKÎncă nu există evaluări

- VLSI Backend Lab ManualDocument56 paginiVLSI Backend Lab ManualAllanki Sanyasi Rao100% (1)

- 2016 Ch1-Intro PDFDocument16 pagini2016 Ch1-Intro PDFTrần Anh TânÎncă nu există evaluări

- IC Design & Low Power TechniquesDocument11 paginiIC Design & Low Power TechniquesMohamed AliÎncă nu există evaluări

- Desgin Rules PDFDocument31 paginiDesgin Rules PDFPrithireddy ThenetiÎncă nu există evaluări

- Rogowski CoilDocument13 paginiRogowski CoilKanishka AhirwarÎncă nu există evaluări

- Ch. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocument43 paginiCh. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- Vlsi Design Unit IDocument39 paginiVlsi Design Unit ISaurabh KatiyarÎncă nu există evaluări

- Low Power VLSI: B.Tech. Project Electronics EngineeringDocument18 paginiLow Power VLSI: B.Tech. Project Electronics EngineeringVipul BajpaiÎncă nu există evaluări

- Scaling & EconomicsDocument29 paginiScaling & EconomicsRoshdy AbdelRassoulÎncă nu există evaluări

- Stick Diagrams and LayoutsDocument17 paginiStick Diagrams and LayoutsPraneetha InumarthiÎncă nu există evaluări

- Chapter01 - An Overview of VLSIDocument12 paginiChapter01 - An Overview of VLSIshashank751Încă nu există evaluări

- Tanner ManualDocument60 paginiTanner ManualFahim Ahmed100% (1)

- Chapter - 1: Ece Department, AcoeDocument55 paginiChapter - 1: Ece Department, AcoeSana SriRamyaÎncă nu există evaluări

- VLSI Answer KeyDocument15 paginiVLSI Answer Keyrendezvous2k23Încă nu există evaluări

- PHD Thesis On Vlsi DesignDocument5 paginiPHD Thesis On Vlsi DesignBuyEssaysTulsa100% (2)

- Layout Design8Document34 paginiLayout Design8Sandeep BoyinaÎncă nu există evaluări

- CMOS Layout: Mask LayersDocument5 paginiCMOS Layout: Mask LayerschittajitsarkarsterÎncă nu există evaluări

- Imp 2Document7 paginiImp 2sohailasghar_tÎncă nu există evaluări

- VLSI Design Lab NewDocument48 paginiVLSI Design Lab NewJubin JainÎncă nu există evaluări

- CAD Algorithms: Physical Design Automation of VLSI SystemsDocument20 paginiCAD Algorithms: Physical Design Automation of VLSI SystemsjeevithaÎncă nu există evaluări

- Mdoc 1Document25 paginiMdoc 1Bhoomek PandyaÎncă nu există evaluări

- P 103Document7 paginiP 103An HoaÎncă nu există evaluări

- Basic VLSI Design Unit-3Document50 paginiBasic VLSI Design Unit-3N.RAMAKUMARÎncă nu există evaluări

- Layout For Analog Integrated Circuits: Analog IC Prof. Guoxing Wang 1Document40 paginiLayout For Analog Integrated Circuits: Analog IC Prof. Guoxing Wang 1Samvel YanÎncă nu există evaluări

- Vlsi NotesDocument5 paginiVlsi NotesDiwakar TiwaryÎncă nu există evaluări

- VLSI: Design FlowDocument37 paginiVLSI: Design FlowCGÎncă nu există evaluări

- Sign OffDocument15 paginiSign OffPraveen Ramesh KarnamÎncă nu există evaluări

- Design RulesDocument14 paginiDesign RulesmayankfirstÎncă nu există evaluări

- VLSI DesignDocument55 paginiVLSI DesignClique for Applied Research in Electronic TechnologyÎncă nu există evaluări

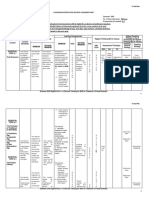

- PDC Lesson Plan NewDocument26 paginiPDC Lesson Plan NewVenky VenkateshÎncă nu există evaluări

- Introduction To VLSI Circuits: Naveen Bhat, Teaching Assistant Karnatak University, DharwadDocument100 paginiIntroduction To VLSI Circuits: Naveen Bhat, Teaching Assistant Karnatak University, DharwadunchalliÎncă nu există evaluări

- Chapter01 - An Overview of VLSIDocument12 paginiChapter01 - An Overview of VLSIParamesh WaranÎncă nu există evaluări

- Paper MSF FinalDocument7 paginiPaper MSF Final918Kiss Secret TipsÎncă nu există evaluări

- 7.the Substrate Integrated Circuits - A New Concept ForDocument8 pagini7.the Substrate Integrated Circuits - A New Concept Forsekhar.nitrklÎncă nu există evaluări

- Ec1401 Vlsi DesignDocument18 paginiEc1401 Vlsi DesignSurya PrakashÎncă nu există evaluări

- 01 EE6306 - MOS Transistor TheoryDocument74 pagini01 EE6306 - MOS Transistor TheoryononahjÎncă nu există evaluări

- ASIC Backend Physical Design Questions - ElectronicsBus 2014Document4 paginiASIC Backend Physical Design Questions - ElectronicsBus 2014Rohith RajÎncă nu există evaluări

- Nand GateDocument1 paginăNand GatekamarajvlsiÎncă nu există evaluări

- Mepco Schlenk Engineering CollegeDocument2 paginiMepco Schlenk Engineering CollegekamarajvlsiÎncă nu există evaluări

- FDSFSDDocument1 paginăFDSFSDkamarajvlsiÎncă nu există evaluări

- PUREITDocument1 paginăPUREITkamarajvlsiÎncă nu există evaluări

- MEMS Modeling Training CourseDocument1 paginăMEMS Modeling Training CoursekamarajvlsiÎncă nu există evaluări

- Synthesis of Reversible Sequential ElementsDocument32 paginiSynthesis of Reversible Sequential ElementskamarajvlsiÎncă nu există evaluări

- RoHS Product ListDocument106 paginiRoHS Product ListkamarajvlsiÎncă nu există evaluări

- RF MEMS Capacitive SwitchDocument3 paginiRF MEMS Capacitive SwitchkamarajvlsiÎncă nu există evaluări

- Kullu Manali SightseeingDocument5 paginiKullu Manali SightseeingkamarajvlsiÎncă nu există evaluări

- Dep ReceiptDocument1 paginăDep ReceiptkamarajvlsiÎncă nu există evaluări

- VL9266 MemsDocument1 paginăVL9266 MemskamarajvlsiÎncă nu există evaluări

- EM Worksohop ProgramDocument2 paginiEM Worksohop ProgramkamarajvlsiÎncă nu există evaluări

- Astable Multivibrator: Circuit DiagramDocument5 paginiAstable Multivibrator: Circuit DiagramkamarajvlsiÎncă nu există evaluări

- Message 2013-05-03 10-00 AMDocument1 paginăMessage 2013-05-03 10-00 AMkamarajvlsiÎncă nu există evaluări

- Transaction DetailsDocument1 paginăTransaction DetailskamarajvlsiÎncă nu există evaluări

- Adjustable Voltage RegulatorDocument3 paginiAdjustable Voltage RegulatorkamarajvlsiÎncă nu există evaluări

- To JCS Karpagam Charity TrustDocument1 paginăTo JCS Karpagam Charity TrustkamarajvlsiÎncă nu există evaluări

- Sean Wolcott Graphic Design 2008 2014Document87 paginiSean Wolcott Graphic Design 2008 2014Audrey WrightÎncă nu există evaluări

- 2002 - Motives and Methods For Participatory Web Design With At-Risk TeensDocument28 pagini2002 - Motives and Methods For Participatory Web Design With At-Risk TeensPaul TreadwellÎncă nu există evaluări

- BTech ME Curriculum Syllabi 2018Document115 paginiBTech ME Curriculum Syllabi 2018GauthamÎncă nu există evaluări

- Comprehensive Famous ArchitectsDocument25 paginiComprehensive Famous ArchitectsExia QuinagonÎncă nu există evaluări

- Macdonald & Rafferty, 2015Document13 paginiMacdonald & Rafferty, 2015Steph Downey100% (1)

- SD3082 Subject Assignment BriefDocument3 paginiSD3082 Subject Assignment BriefSwift StarsÎncă nu există evaluări

- A Simple Guide To The Direct Analysis MethodDocument25 paginiA Simple Guide To The Direct Analysis MethodSamuel PintoÎncă nu există evaluări

- NPD Models Role of Information and Idea Generation For NPD: Session 2Document31 paginiNPD Models Role of Information and Idea Generation For NPD: Session 2Hina SaadÎncă nu există evaluări

- 2 - Estimation of General Characteristics of Fishing Vessels ADocument16 pagini2 - Estimation of General Characteristics of Fishing Vessels AJuan SilvaÎncă nu există evaluări

- GEZE Installation Instructions en 631551Document4 paginiGEZE Installation Instructions en 631551PiotrÎncă nu există evaluări

- DNT NotesDocument9 paginiDNT NotesPranav BISUMBHERÎncă nu există evaluări

- ACE REVIEWED - Submittal - TAS Concrete - Concrete Column Reinforcement - Shop Drawings - Reviewed PDFDocument5 paginiACE REVIEWED - Submittal - TAS Concrete - Concrete Column Reinforcement - Shop Drawings - Reviewed PDFTyler StoneÎncă nu există evaluări

- Foerster and Common Rooman Architecture of Coexistence Ivan Illich Re ReadDocument2 paginiFoerster and Common Rooman Architecture of Coexistence Ivan Illich Re ReadHaider Al-kadhimiÎncă nu există evaluări

- ICT - Designing An AdvertisementDocument19 paginiICT - Designing An AdvertisementLorenzo Mozart Bach100% (1)

- B1 Level English Writing - Theory, The BasicsDocument19 paginiB1 Level English Writing - Theory, The BasicsBob E ThomasÎncă nu există evaluări

- Texto Guia de Ingenieria AntisismicaDocument825 paginiTexto Guia de Ingenieria AntisismicaFrancisco Calderon100% (1)

- Co Po Mapping - R17Document27 paginiCo Po Mapping - R17rashmitshello100% (1)

- Statement of PurposeDocument2 paginiStatement of PurposeDharam ParkashÎncă nu există evaluări

- Achieving Economy and Reliability in Piled Foundation Design For A Building ProjectDocument6 paginiAchieving Economy and Reliability in Piled Foundation Design For A Building ProjectRodrigo RiveraÎncă nu există evaluări

- Synthesis: Verilog Gates: Libra Ry GateDocument26 paginiSynthesis: Verilog Gates: Libra Ry GateSingamaneni AshokkumarÎncă nu există evaluări

- Eapp CidamsDocument13 paginiEapp CidamsMargielyn AguilandoÎncă nu există evaluări

- Case Study - Fika Coffee BarDocument32 paginiCase Study - Fika Coffee Bariris kleinstapelÎncă nu există evaluări

- Implementation Paper - Eye Movement Recognition Based Human Machine Interaction SystemDocument7 paginiImplementation Paper - Eye Movement Recognition Based Human Machine Interaction SystemIJRASETPublicationsÎncă nu există evaluări

- Week3-Courseware-SSP031-CTT8. HUMAN CENTERED DESIGN METHODOLOGYDocument38 paginiWeek3-Courseware-SSP031-CTT8. HUMAN CENTERED DESIGN METHODOLOGYSydney OlandriaÎncă nu există evaluări

- Oliveira Pinho 2008 CITTADocument20 paginiOliveira Pinho 2008 CITTARajesh SahooÎncă nu există evaluări

- Clairemay A. Detoyato Final Nagyud NiDocument164 paginiClairemay A. Detoyato Final Nagyud Nifranz anthonyÎncă nu există evaluări

- ASII - Manualul de IdentitateDocument9 paginiASII - Manualul de IdentitateRareș-Andrei GavriluțăÎncă nu există evaluări

- Architectural Engineering and Design ManagementDocument78 paginiArchitectural Engineering and Design ManagementabhishekBajÎncă nu există evaluări