Documente Academic

Documente Profesional

Documente Cultură

Non Determinism

Încărcat de

ankit13120 evaluări0% au considerat acest document util (0 voturi)

46 vizualizări15 pagininvidia graphics

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PPT, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentnvidia graphics

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPT, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

46 vizualizări15 paginiNon Determinism

Încărcat de

ankit1312nvidia graphics

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPT, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 15

Non-Determinism In C and RTL Models

ICCAD 2006 Ira Chayut, Verification Architect

2006 NVIDIA Corporation

Slide 2

C Models in a Variety of Languages

C Model == Reference Model

Reference Model could be in C, C++, Perl, Python,

Java, Verilog, SystemVerilog, SystemC, emulation,

silicon rendition of the Device Under Test (DUT),

etc.

The DUT can be any implementation,

this presentation assumes a Verilog RTL DUT

2006 NVIDIA Corporation

Slide 3

Validation vs. Verification

Validation: answers the question:

Does the model produce the correct output?

Verification: answers the question:

Does the DUT behavior match that of the

reference model?

2006 NVIDIA Corporation

Slide 4

A Typical Verification Example

Stimulus is applied to the C model and the DUT.

The outputs are then compared.

2006 NVIDIA Corporation

Slide 5

Causes of Mismatches

Errors in:

DUT

C model

stimulus

checker code

compiler or simulator

Differences in the way models handle time

2006 NVIDIA Corporation

Slide 6

Determinism / Non-Determinism

According to Wikipedia:

In a deterministic system, every action, or cause, produces

a reaction, or effect, and every reaction, in turn, becomes

the cause of subsequent reactions. The totality of these

cascading events can theoretically show exactly how the

system will exist at any moment in time.

Thus, a non-deterministic system is one where

knowing the state of a model and the stimulus, we

cannot precisely know the next state and output

At Nvidia the term non-determinism is used for

situations where the C model cannot predict the

DUTs behavior

2006 NVIDIA Corporation

Slide 7

Causes of Non-Determinism

Independence between C model and DUT

Architectural vagueness

Efficiency

Points of arbitration (including memories and

caches)

2006 NVIDIA Corporation

Slide 8

Time and Non-Determinism

Timed-events are the

largest cause of non-

determinism, including:

Memory accesses

Cache fills/hits/misses

Time-outs

Multiple clock domains

Clock jitter in silicon

2006 NVIDIA Corporation

Slide 9

Non-Determinism Work-Arounds

Hints from DUT

Cycle-accurate C models

Smart checkers

Dont verify non-deterministic cases

2006 NVIDIA Corporation

Slide 10

Non-Determinism Example

MUX selects stimulus

until:

FIFO full, or

Timer reaches time-out

C model does not have

concept of time

RTL sees time-outs that

C model does not

!=

2006 NVIDIA Corporation

Slide 11

Hints from DUT

DUT simulation:

provides hints to

untimed C model

gates the C model

weakens the

independent check

by C model

==

2006 NVIDIA Corporation

Slide 12

Cycle-Accurate C Model

Slows C model runs

Slows C model

development

Problem modeling

jitter between async

clock domains

Weakens the

independent check

of C model

2006 NVIDIA Corporation

Slide 13

Smart Checkers

Match out-of-order transactions

Ignore dont care bits

Recognize acceptable extra transactions

Score-board transactions to catch spurious

transactions

Statistical analysis needed sometimes

2006 NVIDIA Corporation

Slide 14

Dont Verify Non-Deterministic Cases

Some cases too difficult

to test

Verify later-stage

results

Validate DUT

Validate in silicon

Avoid non-deterministic

designs

2006 NVIDIA Corporation

Slide 15

Conclusions

C model and DUT behavior may vary for some

stimulus, but both behaviors are correct

Time-based behavior is especially problematic

When non-determinism cannot be avoided:

Smart checkers

Cycle-accurate C models

DUT hints

Validate DUT or silicon

S-ar putea să vă placă și

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- How Formal Verification Can Please Your Project ManagerDocument30 paginiHow Formal Verification Can Please Your Project Managerankit1312Încă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- System Verilog Interview QuestionsDocument22 paginiSystem Verilog Interview QuestionsMani Kiran83% (6)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- CSC 242:-Computer-Aided Systems Design and Verification: Assignment 5Document34 paginiCSC 242:-Computer-Aided Systems Design and Verification: Assignment 5ankit1312Încă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Term Project ReportDocument32 paginiTerm Project Reportankit1312Încă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Model Checking Basics - PsDocument8 paginiModel Checking Basics - Psankit1312Încă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Practical Programming in TCL and TKDocument1.207 paginiPractical Programming in TCL and TKgunit_le100% (3)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Ankit - Jain ResumeDocument1 paginăAnkit - Jain Resumeankit1312Încă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- SyllabusDocument1 paginăSyllabusankit1312Încă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Monthly Ladder Inspection ChecklistDocument4 paginiMonthly Ladder Inspection ChecklistPeter Sare WolloÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Arc Welding ProcessesDocument153 paginiArc Welding Processespratap biswasÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- صيانة المولدات و المحولات الكهربائيهDocument15 paginiصيانة المولدات و المحولات الكهربائيهMostafa AllamÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- cm6800 48x8 NewDocument98 paginicm6800 48x8 Newvijayakumar3661Încă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- BAERD GEN-007 Rev CDocument27 paginiBAERD GEN-007 Rev CPaulÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Technical Report Route To IEng GuidanceDocument11 paginiTechnical Report Route To IEng GuidanceECCÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

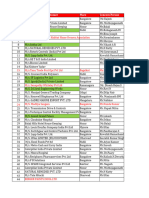

- West Zone: South-West Zone: South Zone: Central Zone: North Zone: North West Zone: East ZoneDocument6 paginiWest Zone: South-West Zone: South Zone: Central Zone: North Zone: North West Zone: East ZoneKanupriyamÎncă nu există evaluări

- EN - 61558 - 2 - 4 (Standards)Document12 paginiEN - 61558 - 2 - 4 (Standards)RAM PRAKASHÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Lab 11 12 ECA HIGH AND LOW PASSDocument32 paginiLab 11 12 ECA HIGH AND LOW PASSAmna EjazÎncă nu există evaluări

- ASW Connection PDFDocument7 paginiASW Connection PDFWawan SatiawanÎncă nu există evaluări

- Buying Solutions' Total Cost of Ownership (TCO) CalculatorDocument93 paginiBuying Solutions' Total Cost of Ownership (TCO) Calculatorankitch123Încă nu există evaluări

- XDocument20 paginiXAlberto BarrosÎncă nu există evaluări

- Sony Video Camera Manual PDFDocument118 paginiSony Video Camera Manual PDFGary Hoehler100% (1)

- Computer Science Ram PresentationDocument11 paginiComputer Science Ram Presentationapi-268896185100% (3)

- Manual Cmp-Smartrw10 CompDocument66 paginiManual Cmp-Smartrw10 CompAllegra AmiciÎncă nu există evaluări

- PEC 2019 Design GuidelinesDocument9 paginiPEC 2019 Design GuidelinesHendrix LevaÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Riviera Sponsorship LetterDocument7 paginiRiviera Sponsorship LetterAnirudh Reddy YalalaÎncă nu există evaluări

- Broadcast Tools Site Sentinel 4 Install Op Manual v2 12-01-2009Document41 paginiBroadcast Tools Site Sentinel 4 Install Op Manual v2 12-01-2009testeemailÎncă nu există evaluări

- Filtration 2Document5 paginiFiltration 2Ramon Dela CruzÎncă nu există evaluări

- W201 Wiring DiagramDocument290 paginiW201 Wiring Diagramilikemyfishbigandblue87% (45)

- C D C SDocument4 paginiC D C SandriÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Karcher Quotation List - 2023Document12 paginiKarcher Quotation List - 2023veereshmyb28Încă nu există evaluări

- Total Productive Maintenance WorksheetDocument2 paginiTotal Productive Maintenance WorksheetSeda De Drasnia100% (1)

- Economics Case StudyDocument28 paginiEconomics Case StudyZehra KHanÎncă nu există evaluări

- Boeing Defence Australia LimitedDocument16 paginiBoeing Defence Australia LimitedMitchÎncă nu există evaluări

- Y62 Patrol Full EditionDocument163 paginiY62 Patrol Full EditionEric Golden100% (8)

- ISO9001 2008certDocument2 paginiISO9001 2008certGina Moron MoronÎncă nu există evaluări

- Genetic Algorithms - Principles and Perspectives - A Guide To GA TheoryDocument327 paginiGenetic Algorithms - Principles and Perspectives - A Guide To GA Theoryluis-barrios-941150% (4)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Fw102 User ManuleDocument12 paginiFw102 User ManulerobÎncă nu există evaluări

- I R Lib ReferenceDocument117 paginiI R Lib Referencebiltou0% (1)