Documente Academic

Documente Profesional

Documente Cultură

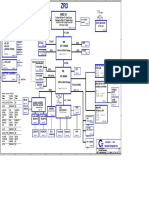

Sic XE

Încărcat de

invincible_shalin6954Descriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Sic XE

Încărcat de

invincible_shalin6954Drepturi de autor:

Formate disponibile

1: Background 1

Alpha Breathing

Breath in

Breath out

Hold

1: Background 3

Memory

The same as that previously described for SIC.

Maximum memory available on a SIC/XE system is

1MB.

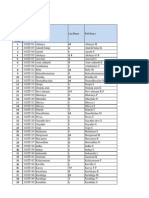

Registers

The SIC/XE machine architecture

1: Background 4

Data formats (48-bit floating point)

f*2^(e-1024)

Instruction formats and addressing modes

e=0 means Format 3 ; e=1 means Format 4

i=0, n=0 means SIC machine (for upward compatible)

i=1, n=0 means immediate addressing

i=0, n=1 means indirect addressing

i=1, n=1 means simple addressing

The SIC/XE machine architecture (cont.)

1: Background 5

1: Background 6

1: Background 7

Instruction set

SIC/XE provides all of the instructions that are available on

the standard versions.

It also provides instructions to perform floating-point

arithmetic operations (ADDF, SUBF, MULF, DIVF..)

Register-to-register arithmetic operations (ADDR,

SUBR,)

Input and Output

SIO (start I/O channel), TIO (test I/O channel) and HIO (halt

I/O channel)

The SIC/XE machine architecture (cont.)

1: Background 8

Data movement

The SIC/XE programming examples

1: Background 9

Data movement

Compared the SIC with SIC/XE

1: Background 10

Arithmetic operations

The SIC/XE programming examples (cont.)

1: Background 11

Looping and indexing operations

The SIC/XE programming examples (cont.)

MOVECH

STR1

STR2

1: Background 12

Indexing and looping operations

The SIC/XE programming examples (cont.)

1: Background 13

Subroutine call and record input operations

The SIC/XE programming examples (cont.)

1: Background 14

CISC: Complex Instruction Set Computers machine.

relatively large and complicated instruction set.

several different instruction formats and length

many different addressing modes.

E.g., VAX, Pentium

The implementation of such an architecture in

hardware tends to be complex.

CISC vs. RISC

1: Background 15

Introduced by Digital Equipment Corporation

(DEC) in 1978.

Memory

All addresses used are byte addresses.

2 bytes forms a word, 4 bytes forms a longword

8 bytes forms a quadword, 16 bytes forms a octaword

Registers

16 general-purpose register. (R15: program counter,

R14: stack pointer, R13: frame pointer, R12: argument

pointer)

The VAX architecture (CISC)

1: Background 16

RISC: Reduced Instruction Set Computers machine

Standard, fixed instruction length

Single-cycle execution of most instructions

Relatively large number of general-purpose registers

Relatively small number of machine instructions

Relatively small number of instruction formats and

addressing modes.

E.g., UltraSPARC, PowerPC, Cray T3E

The implementation of such an architecture in

hardware tends to be simple.

CISC vs. RISC

1: Background 17

Introduced by Sun Microsystem in 1995.

Memory

All addresses used are byte addresses.

2 bytes forms a halfword, 4 bytes forms a word

Registers

A large register file (more than 100 general-purpose

register)

Fixed instruction length

The UltraSPARC architecture (RISC)

S-ar putea să vă placă și

- Tetris FpgaDocument4 paginiTetris Fpgagaqf100% (1)

- 90210-1083DEA E KLogic KLadder PDFDocument154 pagini90210-1083DEA E KLogic KLadder PDFBobyÎncă nu există evaluări

- The Test Access Port and Boundary Scan Architecture - Colin M Maunder and Rodham E Tulloss - Ieee Computer Society Press PDFDocument394 paginiThe Test Access Port and Boundary Scan Architecture - Colin M Maunder and Rodham E Tulloss - Ieee Computer Society Press PDFRupaliÎncă nu există evaluări

- Caal Lab ManualDocument63 paginiCaal Lab ManualFarrukh Abbasi100% (1)

- Logisim LabsDocument157 paginiLogisim LabsJosealberto HernandezÎncă nu există evaluări

- Types of Micro OperationsDocument17 paginiTypes of Micro OperationsP Suresh Babu91% (11)

- ApplicationsDocument44 paginiApplicationsmerinjose123100% (1)

- Analog Labs Manual: IC614 ASSURA410Document108 paginiAnalog Labs Manual: IC614 ASSURA410Kasi BandlaÎncă nu există evaluări

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationDocument13 paginiUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaÎncă nu există evaluări

- Object Code Generation For SICxeDocument41 paginiObject Code Generation For SICxeKruthikaÎncă nu există evaluări

- SP MCQDocument15 paginiSP MCQVishal KesharwaniÎncă nu există evaluări

- AssemblerDocument49 paginiAssemblerkim kimmaÎncă nu există evaluări

- 8086 ProgramingDocument29 pagini8086 ProgramingSumant Arora0% (1)

- 8,16,32 Floating Point Processing in ARMDocument25 pagini8,16,32 Floating Point Processing in ARMOMKAR BHILARE100% (1)

- System Software NotesDocument97 paginiSystem Software NotesTheerthesh Gowda100% (1)

- CH03 Loaders and LinkersDocument20 paginiCH03 Loaders and LinkersTedo Ham100% (4)

- Friend Function and Operator OverloadingDocument54 paginiFriend Function and Operator OverloadingvaibhavÎncă nu există evaluări

- Chapter 7 - Basic Processing UnitDocument47 paginiChapter 7 - Basic Processing UnitMayur Patankar0% (1)

- CO Unit 2-1Document15 paginiCO Unit 2-1Aravinder Reddy SuramÎncă nu există evaluări

- CS1203 System Software UNIT I Question AnsDocument10 paginiCS1203 System Software UNIT I Question AnskeerthisivaÎncă nu există evaluări

- Memory - Lec 3Document74 paginiMemory - Lec 3Danu NimÎncă nu există evaluări

- Unit 2 Assemblers: 2.1 Machine Independent Assembler FeaturesDocument26 paginiUnit 2 Assemblers: 2.1 Machine Independent Assembler FeaturesbenaminsanÎncă nu există evaluări

- System Software Notes 5TH Sem VtuDocument25 paginiSystem Software Notes 5TH Sem VtuNeha Chinni50% (2)

- MP L4 Assembly PDFDocument99 paginiMP L4 Assembly PDFgujjar262069Încă nu există evaluări

- 2.1basic Assemblers FunctionsDocument15 pagini2.1basic Assemblers FunctionsChanchal Rawat100% (1)

- Unit2 AssemblerDocument165 paginiUnit2 AssemblerRameshÎncă nu există evaluări

- CSE-232 LAB ManualDocument23 paginiCSE-232 LAB ManualMuhammad UsmanÎncă nu există evaluări

- A Single Pass Assembler For IBM PCDocument18 paginiA Single Pass Assembler For IBM PCmb_4u67% (3)

- Assignment 3Document2 paginiAssignment 3Dhivya NÎncă nu există evaluări

- Digital Techniques and MicroprocessorsDocument3 paginiDigital Techniques and MicroprocessorsHarshal DevadeÎncă nu există evaluări

- DCLD LabDocument42 paginiDCLD LabRachit ChauhanÎncă nu există evaluări

- System Software Lab ProgramsDocument22 paginiSystem Software Lab ProgramsAbhi Shek100% (1)

- 2 Pass Assembler AlgorithmDocument1 pagină2 Pass Assembler AlgorithmSaraswati BhusanurÎncă nu există evaluări

- EC8681-Microprocessors and Microcontrollers Lab Manual Valliammai-1Document94 paginiEC8681-Microprocessors and Microcontrollers Lab Manual Valliammai-15016 V.GayathriÎncă nu există evaluări

- CA 2marksDocument41 paginiCA 2marksJaya ShreeÎncă nu există evaluări

- Pass 1 Assembler in CDocument15 paginiPass 1 Assembler in CEkta Singh85% (13)

- CoaDocument8 paginiCoaNikhil Singh ChauhanÎncă nu există evaluări

- Lab9 VHDLDocument8 paginiLab9 VHDLFasli CoolÎncă nu există evaluări

- Chapter 3 - String ProcessingDocument28 paginiChapter 3 - String ProcessingTanveer Ahmed HakroÎncă nu există evaluări

- Practical File of Data StructureDocument33 paginiPractical File of Data StructureBlue AceÎncă nu există evaluări

- COA Unit 1Document33 paginiCOA Unit 1Keshav NaganathanÎncă nu există evaluări

- CPP Questions BankDocument4 paginiCPP Questions BankRishikesh MahajanÎncă nu există evaluări

- Systems Software QuestionDocument82 paginiSystems Software QuestionkhalidÎncă nu există evaluări

- Assembly bscs5 QuizDocument3 paginiAssembly bscs5 QuizMutiullahJamil0% (2)

- Stack and SUBROUTINES Bindu AgarwallaDocument15 paginiStack and SUBROUTINES Bindu AgarwallaNobodyÎncă nu există evaluări

- Computer Architecture and Assembly Language Programming - CS401 Fall 2009 Assignment 02 SolutionDocument1 paginăComputer Architecture and Assembly Language Programming - CS401 Fall 2009 Assignment 02 SolutionV XangeÎncă nu există evaluări

- 8086 QuestionsDocument4 pagini8086 Questionsmani_vlsiÎncă nu există evaluări

- Computer Organization: Sandeep KumarDocument117 paginiComputer Organization: Sandeep KumarGaurav NÎncă nu există evaluări

- PPS Lab File With SolutionDocument70 paginiPPS Lab File With SolutionSomesh ShuklaÎncă nu există evaluări

- Program To Calculate Fibonacci Numbers in Assembly Language Using Visual Studio PDFDocument2 paginiProgram To Calculate Fibonacci Numbers in Assembly Language Using Visual Studio PDFDilawarÎncă nu există evaluări

- Computer Organization and ArchitectureDocument3 paginiComputer Organization and ArchitectureAnil MarsaniÎncă nu există evaluări

- Microprocessor and Interfacing Devices/Peripherals: 8086 Instructions SetDocument24 paginiMicroprocessor and Interfacing Devices/Peripherals: 8086 Instructions Setvikas chawlaÎncă nu există evaluări

- Passing Parameters8086Document32 paginiPassing Parameters8086Sivaprakash SÎncă nu există evaluări

- AC58-AT58 Computer OrganizationDocument26 paginiAC58-AT58 Computer OrganizationSaqib KamalÎncă nu există evaluări

- Instruction Codes Computer Registers Computer Instructions Timing and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionDocument38 paginiInstruction Codes Computer Registers Computer Instructions Timing and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionYash Gupta MauryaÎncă nu există evaluări

- Dspa 17ec751 M5Document34 paginiDspa 17ec751 M5digital loveÎncă nu există evaluări

- 6.270 Advanced C Lecture NotesDocument31 pagini6.270 Advanced C Lecture Notessivani05Încă nu există evaluări

- One Pass AssemblerDocument2 paginiOne Pass AssemblerTanvi SharmaÎncă nu există evaluări

- Besck104e-204eDocument3 paginiBesck104e-204eharshagowda0464Încă nu există evaluări

- AMD FX Performance Tuning GuideDocument20 paginiAMD FX Performance Tuning GuideCodrin Darius IlanaÎncă nu există evaluări

- CISCDocument16 paginiCISCAnonymous OQxVUBZVÎncă nu există evaluări

- Micro ProcessorDocument85 paginiMicro Processorkishore532Încă nu există evaluări

- Relational Data Model A Complete Guide - 2020 EditionDe la EverandRelational Data Model A Complete Guide - 2020 EditionÎncă nu există evaluări

- Chapter 2: Advanced Computer ArchitectureDocument101 paginiChapter 2: Advanced Computer ArchitectureTigabu Yaya100% (2)

- 4.5 - Mapping Objective Functions To Fitness FormDocument4 pagini4.5 - Mapping Objective Functions To Fitness Forminvincible_shalin6954Încă nu există evaluări

- 4.2 - Robustness of Traditional Optimization and Search TechniquesDocument4 pagini4.2 - Robustness of Traditional Optimization and Search Techniquesinvincible_shalin6954Încă nu există evaluări

- 4.1 - Introduction To GADocument3 pagini4.1 - Introduction To GAinvincible_shalin6954Încă nu există evaluări

- 4.3 - The Goals of OptimizationDocument4 pagini4.3 - The Goals of Optimizationinvincible_shalin6954Încă nu există evaluări

- Last Date For Submission: 15.03.2017: Assignment-2: Soft Computing (11I006)Document1 paginăLast Date For Submission: 15.03.2017: Assignment-2: Soft Computing (11I006)invincible_shalin6954Încă nu există evaluări

- PING@emergency: K.Padma Sri Lakshmi (152IT165) S.Sindhuja (152IT189)Document3 paginiPING@emergency: K.Padma Sri Lakshmi (152IT165) S.Sindhuja (152IT189)invincible_shalin6954Încă nu există evaluări

- Last Date For Submission: 28.01.2017: Assignment-1: Soft Computing (11I006)Document1 paginăLast Date For Submission: 28.01.2017: Assignment-1: Soft Computing (11I006)invincible_shalin6954Încă nu există evaluări

- Direct HR Cts B.tech ItDocument6 paginiDirect HR Cts B.tech Itinvincible_shalin6954Încă nu există evaluări

- Bse Paper 3 PDFDocument14 paginiBse Paper 3 PDFinvincible_shalin6954Încă nu există evaluări

- Bannari Amman Institute of Technology Department of Information TechnologyDocument7 paginiBannari Amman Institute of Technology Department of Information Technologyinvincible_shalin6954Încă nu există evaluări

- Bannari Amman Institute of Technology Department of Information TechnologyDocument7 paginiBannari Amman Institute of Technology Department of Information Technologyinvincible_shalin6954Încă nu există evaluări

- Sathyamangalam: (Repeat The Three Steps For 8 Times)Document8 paginiSathyamangalam: (Repeat The Three Steps For 8 Times)invincible_shalin6954Încă nu există evaluări

- Bannari Amman Institute of TechnologyDocument2 paginiBannari Amman Institute of Technologyinvincible_shalin6954Încă nu există evaluări

- S7 IT CTS Eligible ListDocument22 paginiS7 IT CTS Eligible Listinvincible_shalin6954Încă nu există evaluări

- Ei73 2 MarksDocument26 paginiEi73 2 MarksSandeep Reddy KankanalaÎncă nu există evaluări

- Efficient Load Balancing in Virtual Machine: Guided ByDocument8 paginiEfficient Load Balancing in Virtual Machine: Guided Byinvincible_shalin6954Încă nu există evaluări

- Newgen Eligible Candidates S7 ITDocument7 paginiNewgen Eligible Candidates S7 ITinvincible_shalin6954Încă nu există evaluări

- Bus Interface UnitDocument4 paginiBus Interface UnitVENKATRAMANÎncă nu există evaluări

- Ade Unit - 4 QBDocument17 paginiAde Unit - 4 QBNithya SÎncă nu există evaluări

- BIT103 Digital LogicDocument1 paginăBIT103 Digital LogicBishalÎncă nu există evaluări

- Modbus Easy Master de W462-E1-07+CP1LDocument4 paginiModbus Easy Master de W462-E1-07+CP1LHarol ValenciaÎncă nu există evaluări

- DeclistDocument6 paginiDeclistNausicaa DdmsÎncă nu există evaluări

- Experiment 2 Wallace Tree Multiplier: 1 ObjectivesDocument10 paginiExperiment 2 Wallace Tree Multiplier: 1 ObjectivesEVD18I001 A BALAVIGNESHÎncă nu există evaluări

- Acer Aspire 3050, 5050 Quanta ZR3 DA0ZR3MB6E0 DA0ZR3MB6C1Document31 paginiAcer Aspire 3050, 5050 Quanta ZR3 DA0ZR3MB6E0 DA0ZR3MB6C1essemirÎncă nu există evaluări

- Digital Electronics and Computer OrganizationDocument3 paginiDigital Electronics and Computer OrganizationSai Prajwal SavanamÎncă nu există evaluări

- Cmos Nor, Deletion Load Nor GateDocument54 paginiCmos Nor, Deletion Load Nor Gatemd siddÎncă nu există evaluări

- BLED112 DatasheetDocument12 paginiBLED112 DatasheetAndualem TadesseÎncă nu există evaluări

- Network TheoryDocument31 paginiNetwork TheoryPradeep M NÎncă nu există evaluări

- Application Kits: PRICE LIST - Currency: USD (No Tax) April 2011Document11 paginiApplication Kits: PRICE LIST - Currency: USD (No Tax) April 2011piyushpandeyÎncă nu există evaluări

- Lab8 2-Bit Binary Adder-SubtractorDocument11 paginiLab8 2-Bit Binary Adder-SubtractorAhmed Razi UllahÎncă nu există evaluări

- Address SingDocument32 paginiAddress SingGousAttarÎncă nu există evaluări

- Ug585 Ch05 InterconnectDocument12 paginiUg585 Ch05 InterconnectIdris TarwalaÎncă nu există evaluări

- Intel 815e SchematicsDocument33 paginiIntel 815e SchematicsTilak AmarghdeÎncă nu există evaluări

- DDI0243C Adk r3p0 TRMDocument226 paginiDDI0243C Adk r3p0 TRMdraksunilÎncă nu există evaluări

- M.tech Mid Question Paper CPLD & FpgaDocument2 paginiM.tech Mid Question Paper CPLD & Fpgakanavath100% (3)

- DEC Manual-2017Document52 paginiDEC Manual-2017Gopalakrishna Murthy C RÎncă nu există evaluări

- DHAR BootDocument6 paginiDHAR BootVikas KumarÎncă nu există evaluări

- K9GAG08U0E Samsung PDFDocument55 paginiK9GAG08U0E Samsung PDFHamza Abbasi AbbasiÎncă nu există evaluări

- Uvm Ref Flow UgDocument24 paginiUvm Ref Flow Ugbrk_318Încă nu există evaluări

- CPU y Sus ComponentesDocument1 paginăCPU y Sus ComponentesStarlyn ElDistinguidoÎncă nu există evaluări

- 01 Schematic Design and VHDL Using AlteraDocument7 pagini01 Schematic Design and VHDL Using AlteraIndira KarimovaÎncă nu există evaluări

- Simple As Possible Computer (SAP-1) : Lecture-3Document44 paginiSimple As Possible Computer (SAP-1) : Lecture-3Tawhid KhondakarÎncă nu există evaluări