Documente Academic

Documente Profesional

Documente Cultură

Memory Devices: RAM, ROM, PROM, EPROM Explained

Încărcat de

samsneelamDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Memory Devices: RAM, ROM, PROM, EPROM Explained

Încărcat de

samsneelamDrepturi de autor:

Formate disponibile

1

Memory Devices

Memory: Is one or more sets of chips

that store data/program instructions,

either temporarily or permanently .

It is critical processing component in

any computer

PCs use several different types

2. RAM,ROM,PROM,EPROM

2

RAM,ROM,PROM,EPROM

Memory Devices

Two most important are

RAM(Random Access Memory)

ROM(Read-only Memory)

They work in different ways and perform

distinct functions

CPU Registers

Cache Memory

3

RAM

RAM is packaged as a chip.

Basic storage unit is a cell (one bit per cell).

Multiple RAM chips form a memory.

Random Access Memory

Volatile

Used for temporary storage

Typical ranges 256 MB - 4 GB

Random Access means direct access to any part of

memory

DRAM and SRAM are volatile memories

Lose information if powered off.

SRAM

stores the bit as a voltage

Low density but high speed

known as cache memory

DRAM made up of MOS transistor gates

Stores bit as a charge

High density and low power consumption

Charge leaks

5

Nonvolatile Memories(ROM)

Nonvolatile memories retain value even if

powered off.

Generic name is read-only memory (ROM).

Misleading because some ROMs can be

read and modified.

Diodes arranged in matrix form

existence of diode means 1 otherwise 0

Various types of ROM are available

PROM, EPROM, EEPROM and Flash Memory

6

Nonvolatile Memories(ROM)

Types of ROMs

Programmable ROM (PROM)

Eraseable programmable ROM (EPROM)

Electrically eraseable PROM (EEPROM)

Flash memory (used in portable digital devices)

Firmware (Program instruction used frequently)

Program stored in a ROM

Boot time code, BIOS (basic input/output

system)

graphics cards, disk controllers.

PROM

programmable read-only memory (PROM)

The key difference from a standard ROM is

that the data is written into a ROM during

manufacture, while with a PROM the data is

programmed into them after manufacture.

So ROMs are used only for large production

runs, while PROMs are used for smaller

production where the program may have to

be changed.

EPROM

erasable programmable read only memory

retains its data when its power supply is

switched off. In other words, it is non-volatile

Stores a bit by charging the floating gate of a

FET

Once programmed, an EPROM can be erased

by exposing it to strong ultraviolet light source

(such as from a mercury-vapor light)

Applications include Product Development,

experimental project and college laboratories

EEPROM

Electrically Erasable Programmable Read-

Only Memory

is a type of non-volatile memory used in

computers and other electronic devices to store

small amounts of data that must be saved when

power is removed, e.g., calibration tables or

device configuration.

Erases the data at the register level electrically

Entire chip can be erased within milli seconds

individual bytes in a traditional EEPROM can be

independently read, erased, and re-written.

An EPROM usually must be removed from the

device for erasing and programming, whereas

EEPROMs can be programmed and erased in-

circuit, by applying special programming

signals

Flash Memory

Difference lies in erasure procedure

Can be erased from entirety or at sector level

unlike EEPROM which erases data at register

level

Suitable for low power system applications

also

Memory Mapping

A Pictorial representation in which memory devices

are located in the entire range of addresses

Interfacing logic defines the range of memory

addresses for each memory device

Housing scheme

Memory Interfacing

Tri-state devices

Buffer

Decoder

Encoder

D flip-flops

Memory Interfacing

Should be able to select the chip

Identify the register

Enable the appropriate buffer

15

8255

Programmable Peripheral

Interface

16

8255

ItisaprogrammableperipheralInterface

withthreei/oports

A8 bits

B8bits

C4bitsupperand4bitslower

82C55 : Pin Layout

18

19

A

B

Y

0

G

2A

G

1

C

G

2B

Y

1

Y

2

Y

3

Y

4

Y

5

Y

6

Y

7

A7

A3

A4

A6

A5

A0

D7 - D0

IORC

IOWC

A1

A2

RESET

RD

WR

A0

A1

RESET

CS

D0

D1

D2

D3

D4

D5

D6

D7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

P

o

r

t

C

P

o

r

t

B

P

o

r

t

A

20

PA,PB,PC

(PortA,B,C)

8biti/oports

CS(ChipSelect) Alowsignalatthispinenablesthechip

RD(Read) Readenable

WR(Write) Writeenable

D0-D7(DataBus)

Bi-directionaldatalines

A0,A1(Address) Addressselect

21

The8255canworkin2modes

thatareI/OmodeandBSRmode

i/omodeisfurtherdividedinto

1.Mode0(BasicI/O)

2.Mode1(StrobeI/O)

3.Mode2(Bi-ConditionalBus)

STB (ACTIVE LOW)

IBF

INTR

OBF

ACK (ACTIVE LOW)

INTR

INTE

23

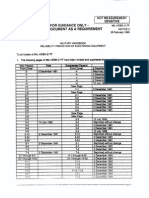

Control Bytes for I/O

mode

1

D0 D1 D2 D3 D4 D5 D6 D7

Group B

Port C (lower)

1 = input

0 = output

Port B

1 = input

0 = output

Mode selection

00 = mode 0

01 = mode 1

1x = mode 2

Group A

Port C (upper)

1 = input

0 = output

Port A

1 = input

0 = output

Mode selection

00 = mode 0

01 = mode 1

1x = mode 2

8255 Control Word

Basic Mode Definitions and Bus Int

Mode 0

Basic I/O

Mode 1

Strobe I/O

Mode 2

Bi-Dir Bus

11-26

Programming 8255

8255 has three operation modes: mode 0, mode 1, and mode 2

8255 PPI contd.

3 ports in 8255 from users point of view

- Port A, Port B and Port C.

Port C composed of two independent 4-bit ports

- PC7-4 (PC Upper) and PC3-0 (PC Lower)

A1 A0 Selected port

0 0 Port A

0 1 Port B

1 0 Port C

1 1 Control port

27

Intel 8255 PPI

8255 40 pin DIP

V

cc

(+5V)

PA

7-0

GND

RD

WR PC

7-4

CS PC

3-0

D

7-0

PB

7-0

A

1

A

0

Reset

Port A

Port C

Control Port

Port B

U3A

7404

1 2

U1

7430

1

2

3

4

5

6

11

12

8

U2A

7404

1 2

A7

M/IO*

Chip Select Circuit

28

A7=0, A6=1, A5=1, A4=1, A3=1, A2=1, & M/IO*= 0

8255 PPI Contd.

There is also a Control port from the Processor point

of view. Its contents decides the working of 8255.

When CS (Chip select) is 0, 8255 is selected for

communication by the processor. The chip select

circuit connected to the CS pin assigns addresses to

the ports of 8255.

For the chip select circuit shown, the chip is selected

when A7=0, A6=1, A5=1, A4=1, A3=1, A2=1, & M/IO*= 0

Port A, Port B, Port C and Control port will have the

addresses as 7CH, 7DH, 7EH, and 7FH respectively.

29

8255 PPI Contd.

30

Mode 0: Simple Input or Output

In this mode, ports A, B are used as two simple 8-bit I/O ports

port C as two 4-bit ports.

Each port can be programmed to function as simply an input port or

an output port. The input/output features in Mode 0 are as follows.

1. Outputs are latched.

2. Inputs are not latched.

3. Ports dont have handshake or interrupt capability.

8255 PPI Contd.

31

Mode 1: Input or Output with Handshake

In this mode, handshake signals are exchanged between

the MPU and peripherals prior to data transfer.

The features of the mode include the following:

1. Two ports (A and B) function as 8-bit I/O ports.

They can be configured as either as input or output ports.

2. Each port uses three lines from ort C as handshake signals.

The remaining two lines of Port C can be used for simple I/O operations.

3. Input and Output data are latched.

4. Interrupt logic is supported.

8255 PPI Contd.

32

Mode 2: Bidirectional Data Transfer

This mode is used primarily in applications such as data transfer

between two computers.

In this mode, Port A can be configured as the bidirectional port

Port B either in Mode 0 or Mode 1.

Port A uses five signals from Port C

as handshake signals for data transfer.

The remaining three signals from port C can be used either

as simple I/O or as handshake for port B.

8255 Handshake signals

Where are the Handshake signals?

Port C pins act as handshake signals, when Port A

and Port B are configured for other than Mode 0.

Port A in Mode 2 and Port B in Mode 1 is possible,

as it needs only 5+3 = 8 handshake signals

After Reset of 8255, Port A , Port B , and Port C are

configured for Mode 0 operation as input ports.

33

8255 Handshake signals Contd.

PC2-0 are used as handshake signals by Port B

when configured in Mode 1. This is immaterial

whether Port B is configured as i/p or o/p port.

PC5-3 are used as handshake signals by Port A

when configured as i/p port in Mode 1.

PC7,6,3 are used as handshake signals by Port A

when configured as o/p port in Mode 1.

PC7-3 are used as handshake signals by Port A

when configured in Mode 2.

34

8255 PPI Contd.

Port A can work in Mode 0, Mode 1, or Mode 2

Port B can work in Mode 0, or Mode 1

Port C can work in Mode 0 only, if at all

Port A, Port B and Port C can work in Mode 0

Port A and Port B can work in Mode 1

Only Port A can work in Mode 2

35

Port C as provider of Status

PC provides status info of PA & PB when not in mode 0

PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

OBF* INTE IBF INTE INT INTE IBF/OBF* INT

PA status in Mode

1 o/p (along with

INT)

PA status in

Mode 1 i/p

PB status in Mode 1

i/p or o/p

PA status in Mode 2

IBF = i/p buffer full

OBF* = o/p buffer full

INT = Interrupt INTE = Interrupt Enable

36

S-ar putea să vă placă și

- Electronic Devices and Circuits (EME-306) Lab 1: ObjectiveDocument7 paginiElectronic Devices and Circuits (EME-306) Lab 1: ObjectiveAhmed SayedÎncă nu există evaluări

- "Keypad and LCD Interfacing Using MicrocontrollerDocument23 pagini"Keypad and LCD Interfacing Using MicrocontrollerKamal PatidarÎncă nu există evaluări

- Testing The PIC Microcontroller (Pic 16F877A)Document6 paginiTesting The PIC Microcontroller (Pic 16F877A)Matt ImriÎncă nu există evaluări

- Yamaha Ef1000is Service ManualDocument108 paginiYamaha Ef1000is Service ManualAnonymous N5EGGPbySÎncă nu există evaluări

- Scrolling Message Display - Project Report - Nov 15, 2011Document71 paginiScrolling Message Display - Project Report - Nov 15, 2011Arun Arya33% (3)

- Microcontroller and Embedded SystemsDocument2 paginiMicrocontroller and Embedded SystemsIndranilÎncă nu există evaluări

- PC Control Using TV RemoteDocument46 paginiPC Control Using TV RemoteManojKumarÎncă nu există evaluări

- The Drive Design of The STM32-based Brushless DC Motor: Song Wang, Wang Guo, Wenqiang DunDocument9 paginiThe Drive Design of The STM32-based Brushless DC Motor: Song Wang, Wang Guo, Wenqiang DunMarco LisiÎncă nu există evaluări

- LM - Build An ARM-based Embedded Web ServerDocument46 paginiLM - Build An ARM-based Embedded Web ServerEmadElDinEzzatÎncă nu există evaluări

- Ssc5x86h ManDocument29 paginiSsc5x86h ManValdenir DuarteÎncă nu există evaluări

- 25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentDocument84 pagini25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentdileeppatraÎncă nu există evaluări

- Audio Player Using The PIC32, MCP4822, microSD Card and The MDDFS LibraryDocument9 paginiAudio Player Using The PIC32, MCP4822, microSD Card and The MDDFS Librarytahmidmc100% (2)

- mcb1700 LAB - Intro - ARM Cortex m3Document22 paginimcb1700 LAB - Intro - ARM Cortex m3RagulANÎncă nu există evaluări

- MicroPIC18F Lite User ManualDocument19 paginiMicroPIC18F Lite User ManualElena Gilbert100% (1)

- Permanent Switch Board ContentDocument56 paginiPermanent Switch Board ContentCrispÎncă nu există evaluări

- 8051 PPT For MSCDocument138 pagini8051 PPT For MSCvikash sharmaÎncă nu există evaluări

- Avr AtmegaDocument309 paginiAvr AtmegakcraussÎncă nu există evaluări

- Samsung UN46C7000WF Chassis N80A PDFDocument129 paginiSamsung UN46C7000WF Chassis N80A PDFJoseGyEjÎncă nu există evaluări

- LPC2148 ARM7 OverviewDocument16 paginiLPC2148 ARM7 OverviewNaagaraaju AaraadhyulaÎncă nu există evaluări

- 8051 PPTDocument30 pagini8051 PPTBhaskarReddyVangalaÎncă nu există evaluări

- Stm32F10Xx8 and Stm32F10Xxb Errata SheetDocument26 paginiStm32F10Xx8 and Stm32F10Xxb Errata SheetHagar2007Încă nu există evaluări

- DSP Based Electrical Lab: Gokaraju Rangaraju Institute of Engineering & Technology (Autonomous)Document77 paginiDSP Based Electrical Lab: Gokaraju Rangaraju Institute of Engineering & Technology (Autonomous)P Praveen KumarÎncă nu există evaluări

- Ch01 Microcontroller History and FeaturesDocument20 paginiCh01 Microcontroller History and Featuresmaissy dellaÎncă nu există evaluări

- Interfacing Programs For 8085Document37 paginiInterfacing Programs For 8085archankumarturagaÎncă nu există evaluări

- VSK - 2148 Emb LabDocument73 paginiVSK - 2148 Emb LabrahumanÎncă nu există evaluări

- Microcontrollers and Embedded SystemsDocument35 paginiMicrocontrollers and Embedded SystemsTarek BarhoumÎncă nu există evaluări

- PIC Single-Chip 4-Digit 99-Minute Timer: DiscussionDocument4 paginiPIC Single-Chip 4-Digit 99-Minute Timer: Discussionravikiran1955Încă nu există evaluări

- STM32 RS-485Document12 paginiSTM32 RS-485mail87523Încă nu există evaluări

- Mbedded Echnosolutions: We Are India 'S One of The Leading Trainings & Jobs Providing OrganizationDocument23 paginiMbedded Echnosolutions: We Are India 'S One of The Leading Trainings & Jobs Providing OrganizationKalyani ShindeÎncă nu există evaluări

- MPMC Unit4Document61 paginiMPMC Unit4Nandhini ShreeÎncă nu există evaluări

- Microchip dsPIC30F2020 SMPS DatasheetDocument286 paginiMicrochip dsPIC30F2020 SMPS DatasheetMarlon MoscosoÎncă nu există evaluări

- Renesas Flash Programmer Sample Circuit For Programming PC Serial PDFDocument5 paginiRenesas Flash Programmer Sample Circuit For Programming PC Serial PDFAjay J VermaÎncă nu există evaluări

- FSM DesignDocument61 paginiFSM DesignParesh SawantÎncă nu există evaluări

- 8051 Microcontroller FAQDocument160 pagini8051 Microcontroller FAQkranthi633Încă nu există evaluări

- Introduction To PSpiceDocument15 paginiIntroduction To PSpiceUmera Anjum100% (1)

- Acx 391 AkbDocument2 paginiAcx 391 AkbmobiFlip.de100% (1)

- Lenovo DMI DecodeDocument14 paginiLenovo DMI DecodeMarcelloÎncă nu există evaluări

- Port ProgrammingDocument29 paginiPort ProgrammingWaleed Ullah Wahlah100% (1)

- RTX51 Tiny RTOS introduction guideDocument3 paginiRTX51 Tiny RTOS introduction guideShraddha SaranÎncă nu există evaluări

- Metering Application ReportDocument428 paginiMetering Application ReportRené PereiraÎncă nu există evaluări

- LPC11U6XDocument97 paginiLPC11U6XDenes MarschalkoÎncă nu există evaluări

- Emb PIC Charles Kim Chap2Document2 paginiEmb PIC Charles Kim Chap2subiÎncă nu există evaluări

- Programming Practices With SimulatorsDocument11 paginiProgramming Practices With Simulatorsarun0% (2)

- Interfacing Prgrammable Keyboard and Display Controller - 8279Document3 paginiInterfacing Prgrammable Keyboard and Display Controller - 8279senthilvlÎncă nu există evaluări

- ARDUINO UNO DocumentDocument25 paginiARDUINO UNO DocumentAilapaka ManojÎncă nu există evaluări

- RC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologiesDocument4 paginiRC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologieskhhoaÎncă nu există evaluări

- Pic Micro ControllerDocument83 paginiPic Micro ControllerDenise Nelson100% (3)

- AVR Lecture 2Document72 paginiAVR Lecture 2Mahrukh Baloch100% (2)

- LPC2148 EbookDocument89 paginiLPC2148 Ebookkarthikeyan_mani1987Încă nu există evaluări

- Orcad PSpice DesignerDocument47 paginiOrcad PSpice DesignerAishwarya JS100% (1)

- Arm ProcessorDocument9 paginiArm ProcessorRahul AgarwalÎncă nu există evaluări

- Circuit TodayDocument30 paginiCircuit TodayBrian GiriÎncă nu există evaluări

- 8 Bit Alu Using Gdi TechniqueDocument7 pagini8 Bit Alu Using Gdi TechniqueTADIBOINA PAVAN KUMARÎncă nu există evaluări

- 12v To 18v ConverterDocument7 pagini12v To 18v ConverterLuis Paulo100% (1)

- 8255 Programmable Peripheral InterfaceDocument27 pagini8255 Programmable Peripheral InterfaceSivaprakasam KarthikeyanÎncă nu există evaluări

- MPMC U3 PDFDocument178 paginiMPMC U3 PDFMani PÎncă nu există evaluări

- Basics of Peripheral Devices and WorkingDocument33 paginiBasics of Peripheral Devices and WorkingNarasimha Murthy Yayavaram100% (1)

- 8155 Static Ram With I/O Ports and TimerDocument59 pagini8155 Static Ram With I/O Ports and Timerchaturveditanisha17Încă nu există evaluări

- Ilovepdf MergedDocument430 paginiIlovepdf MergedYuvraj ChhabraÎncă nu există evaluări

- Military HandbookDocument80 paginiMilitary HandbookLuthfyatma HardyÎncă nu există evaluări

- Pixeles Bca & Mca (Ignou) : ClassesDocument15 paginiPixeles Bca & Mca (Ignou) : ClassesslayrÎncă nu există evaluări

- Computer Memory: Types of RamDocument3 paginiComputer Memory: Types of RamJose Ric Catarus Bataluna Jr.Încă nu există evaluări

- 1985 MMI LSI Databook 6ed PDFDocument794 pagini1985 MMI LSI Databook 6ed PDFgschadowÎncă nu există evaluări

- Thesis Internal Data Bus of A Small Student SatelliteDocument96 paginiThesis Internal Data Bus of A Small Student SatelliteSøren Møller Dath100% (1)

- Mei Cashflow SC / SC Advance Operation & Maintenance ManualDocument14 paginiMei Cashflow SC / SC Advance Operation & Maintenance ManualNosce Te IpsumÎncă nu există evaluări

- Chapter 6Document21 paginiChapter 6adeepadeepÎncă nu există evaluări

- EC574Document1 paginăEC574utkarsh rajwanshÎncă nu există evaluări

- Assignment - Bca - Introduction To ItDocument16 paginiAssignment - Bca - Introduction To Itraj1182100% (1)

- Chapter 1: Introduction To HCS12/MC9S12 The HCS12 Microcontroller Han-Way Huang Minnesota State University, Mankato September 2009Document31 paginiChapter 1: Introduction To HCS12/MC9S12 The HCS12 Microcontroller Han-Way Huang Minnesota State University, Mankato September 2009Omar LopezÎncă nu există evaluări

- Chapter - 4 Computer Memory Notes EnglishDocument6 paginiChapter - 4 Computer Memory Notes EnglishAshish SharmaÎncă nu există evaluări

- Easa Basic Computer StructureDocument33 paginiEasa Basic Computer StructureAlaa MortadaÎncă nu există evaluări

- Fundamentals of Microprocessor and Microcontroller: Dr. Farid FarahmandDocument51 paginiFundamentals of Microprocessor and Microcontroller: Dr. Farid FarahmandvinhkhkÎncă nu există evaluări

- Memory OrganizationDocument36 paginiMemory OrganizationjenyrennyÎncă nu există evaluări

- Fundamentals of Microprocessor and MicrocontrollerDocument55 paginiFundamentals of Microprocessor and MicrocontrollerDarrius Dela PeñaÎncă nu există evaluări

- Memory Devices: RAM, ROM, PROM, EPROM ExplainedDocument37 paginiMemory Devices: RAM, ROM, PROM, EPROM ExplainedsamsneelamÎncă nu există evaluări

- VHDL Beginners BookDocument201 paginiVHDL Beginners Bookapi-3731978100% (7)

- ES Notes PDFDocument160 paginiES Notes PDFerthineni ushaÎncă nu există evaluări

- Ram & Rom 2Document13 paginiRam & Rom 2Rashi GurnaniÎncă nu există evaluări

- D D D D D: TMS27C512 65536 BY 8-BIT UV ERASABLE TMS27PC512 65536 BY 8-BIT Programmable Read-Only MemoriesDocument13 paginiD D D D D: TMS27C512 65536 BY 8-BIT UV ERASABLE TMS27PC512 65536 BY 8-BIT Programmable Read-Only MemoriesasdasdÎncă nu există evaluări

- Anti FuseDocument2 paginiAnti FuseRahmatullah JatoiÎncă nu există evaluări

- ELX304 Topic5 Lesson 1 Pr2Document26 paginiELX304 Topic5 Lesson 1 Pr2Mahesvaran SubramaniamÎncă nu există evaluări

- Problem Sloving Through C ProgrammingDocument51 paginiProblem Sloving Through C Programmingmanoj hmÎncă nu există evaluări

- Lecture 8: ROM & Programmable Logic Devices: Points Addressed in This LectureDocument5 paginiLecture 8: ROM & Programmable Logic Devices: Points Addressed in This LectureiwsisÎncă nu există evaluări

- Sample ChapterDocument16 paginiSample ChapterPreetham SaigalÎncă nu există evaluări

- Complet PRESENTATION On All The Hardwares That Computer Use or NeadDocument361 paginiComplet PRESENTATION On All The Hardwares That Computer Use or Neadpriankush100% (1)

- Memory TypesDocument17 paginiMemory TypesMitul Modi100% (2)

- Programmable Logic DevicesDocument50 paginiProgrammable Logic Devicesanon_463330020Încă nu există evaluări

- MMI PAL Handbook 3ed 1983Document660 paginiMMI PAL Handbook 3ed 1983yewie561Încă nu există evaluări