Documente Academic

Documente Profesional

Documente Cultură

Chapter 2 - Introduction To Logic Circuits

Încărcat de

KarimovaRaikhanovna0 evaluări0% au considerat acest document util (0 voturi)

78 vizualizări80 paginiThis chapter introduces logic circuits and their basic components. It discusses switches, binary logic, AND/OR logic functions, truth tables, logic gates such as NAND and NOR, Boolean algebra concepts like DeMorgan's theorems, and implementations of logic functions using gates. It also covers modeling logic circuits using Verilog, minimizing logic functions, and designing circuits using CAD tools. The chapter contains numerous figures illustrating these concepts.

Descriere originală:

chapter2

Titlu original

Chapter 2 - Introduction to Logic Circuits

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PPT, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentThis chapter introduces logic circuits and their basic components. It discusses switches, binary logic, AND/OR logic functions, truth tables, logic gates such as NAND and NOR, Boolean algebra concepts like DeMorgan's theorems, and implementations of logic functions using gates. It also covers modeling logic circuits using Verilog, minimizing logic functions, and designing circuits using CAD tools. The chapter contains numerous figures illustrating these concepts.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPT, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

78 vizualizări80 paginiChapter 2 - Introduction To Logic Circuits

Încărcat de

KarimovaRaikhanovnaThis chapter introduces logic circuits and their basic components. It discusses switches, binary logic, AND/OR logic functions, truth tables, logic gates such as NAND and NOR, Boolean algebra concepts like DeMorgan's theorems, and implementations of logic functions using gates. It also covers modeling logic circuits using Verilog, minimizing logic functions, and designing circuits using CAD tools. The chapter contains numerous figures illustrating these concepts.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPT, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 80

Chapter 2

Introduction to Logic Circuits

Figure 2.1. A binary switch.

x 1 = x 0 =

(a) Two states of a switch

S

x

(b) Symbol for a switch

2

Figure 2.2. A light controlled by a switch.

(a) Simple connection to a battery

S

(b) Using a ground connection as the return path

Battery Light

Power

supply

S

Light

x

x

3

Figure 2.3. Two basic functions.

(a) The logical AND function (series connection)

S

Power

supply

S

S

Power

supply S

(b) The logical OR function (parallel connection)

Light

Light

x

1

x

2

x

1

x

2

4

Figure 2.4. A series-parallel connection.

S

Power

supply S

Light

S

X

1

X

2

X

3

5

Figure 2.5. An inverting circuit.

S

Light

Power

supply

R

x

6

Figure 2.6. A truth table for the AND and OR operations.

7

Figure 2.7. Three-input AND and OR operations.

8

x

1

x

2

x

n

x

1

x

2

x

n

+ + +

x

1

x

2

x

1

x

2

+

x

1

x

2

x

n

x

1

x

2

x

1

x

2

x

1

x

2

x

n

(a) AND gates

(b) OR gates

x

x

(c) NOT gate

Figure 2.8. The basic gates.

9

Figure 2.9. The function from Figure 2.4.

x

1

x

2

x

3

f x

1

x

2

+ ( ) x

3

=

10

Figure 2.10. An example of logic networks.

Figure 2.11. An example of a logic circuit.

12

Figure 2.12. Addition of binary numbers.

13

Figure 2.13. Proof of DeMorgans theorem in 15a.

14

Figure 2.14. The Venn diagram representation.

x y

z

x

x y x y

x x x

(a) Constant 1 (b) Constant 0

(c) Variable x (d)

(e) (f)

(g) (h)

x

x y x y +

x y z + x y

y

x

Figure 2.15. Verification of the distributive property

x (y + z) = x y + x z

x y

z

x y

z

x y

z

x y

z

x y

z

x y

z

x x y

x y x + z x y z + ( )

(a) (d)

(c) (f)

x z y z + (b) (e)

x y

z

y x

z

x y

z

x y

y z

x y x + z

x z

x y

z

x y

x y x + z y z +

x y

z

x z

y

z

x

y

z

x

Figure 2.15. Verification of the distributive property

x (y + z) = x y + x z

Figure 2.17. Proof of the distributive property 12b.

18

Figure 2.18. Proof of DeMorgans theorem 15a.

19

Figure 2.19. A function to be synthesized.

20

f

(a) Canonical sum-of-products

f

(b) Minimal-cost realization

x

2

x

1

x

1

x

2

Figure 2.20. Two implementations of the function in Figure 2.19.

21

Figure 2.21. A bubble gumball factory.

22

Figure 2.22 Three-variable minterms and maxterms.

23

Figure 2.23. A three-variable function.

24

Figure 2.24. Two realizations of a function in Figure 2.23.

f

(a) A minimal sum-of-products realization

f

(b) A minimal product-of-sums realization

x

1

x

2

x

3

x

2

x

1

x

3

25

Figure 2.25. NAND and NOR gates.

x

1

x

2

x

n

x

1

x

2

x

n

+ + +

x

1

x

2

x

1

x

2

+

x

1

x

2

x

n

x

1

x

2

x

1

x

2

x

1

x

2

x

n

(a) NAND gates

(b) NOR gates

26

x

1

x

2

x

1

x

2

x

1

x

2

x

1

x

2

x

1

x

2

x

1

x

2

x

1

x

2

x

1

x

2

+ =

(a)

x

1

x

2

+ x

1

x

2

= (b)

Figure 2.26. DeMorgans theorem in terms of logic gates.

27

Figure 2.27. Using NAND gates to implement a sum-of-products.

x

1

x

2

x

3

x

4

x

5

x

1

x

2

x

3

x

4

x

5

x

1

x

2

x

3

x

4

x

5

28

Figure 2.28. Using NOR gates to implement a product-of sums.

x

1

x

2

x

3

x

4

x

5

x

1

x

2

x

3

x

4

x

5

x

1

x

2

x

3

x

4

x

5

29

Figure 2.29 NOR-gate realization of the function in Example 2.11.

x

1

f

(a) POS implementation

(b) NOR implementation

f

x

3

x

2

x

1

x

3

x

2

30

Figure 2.30. NAND-gate realization of the function in Example 2.10.

f

f

(a) SOP implementation

(b) NAND implementation

x

1

x

3

x

2

x

3

x

2

x

1

31

Figure 2.31. Truth table for a three-way light control.

32

Figure 2.32. Implementation of the function in Figure 2.31.

f

(a) Sum-of-products realization

(b) Product-of-sums realization

f

x

1

x

3

x

2

x

3

x

1

x

2

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 0

1 1 1 1

(a) Truth table

s x

1

x

2

f (s, x

1

, x

2

)

f

x

1

x

2

s

f

s

x

1

x

2

0

1

(c) Graphical symbol

(b) Circuit

0

1

(d) More compact truth-table representation

f (s, x

1

, x

2

)

s

x

1

x

2

Figure 2.33. Implementation of a multiplexer.

Figure 2.34. Display of numbers.

35

Figure 2.35. A typical CAD system.

Design conception

Verilog Schematic capture

DESIGN ENTRY

Design correct?

Functional simulation

No

Yes

No

Synthesis

Physical design

Chip configuration

Timing requirements met?

Timing simulation

Figure 2.36. The logic circuit for a multiplexer.

37

Figure 2.37. Verilog code for the circuit in Figure 2.36.

38

Figure 2.38. Verilog code for a four-input circuit.

module example2 (x1, x2, x3, x4, f, g, h);

input x1, x2, x3, x4;

output f, g, h;

and (z1, x1, x3);

and (z2, x2, x4);

or (g, z1, z2);

or (z3, x1, ~x3);

or (z4, ~x2, x4);

and (h, z3, z4);

or (f, g, h);

endmodule

39

Figure 2.39. Logic circuit for the code in Figure 2.38.

40

Figure 2.40. Using the continuous assignment to specify the circuit in

Figure 2.36.

41

Figure 2.41. Using the continuous assignment to specify the circuit in

Figure 2.39.

module example4 (x1, x2, x3, x4, f, g, h);

input x1, x2, x3, x4;

output f, g, h;

assign g = (x1 & x3) | (x2 & x4);

assign h = (x1 | ~x3) & (~x2 | x4);

assign f = g | h;

endmodule

42

Figure 2.42. Behavioral specification of the circuit in Figure 2.36.

43

Figure 2.43. A more compact version of the code in Figure 2.42.

44

Figure 2.44. A logic circuit with two modules.

45

Figure 2.45. Verilog specification of the circuit in Figure 2.12.

46

Figure 2.46. Verilog specification of the circuit in Figure 2.34.

47

Figure 2.47. Hierarchical Verilog code for the circuit in Figure 2.44.

48

Figure 2.48 The function f (x

1

, x

2

, x

3

) = m(0, 2, 4, 5, 6).

49

x

2

(a) Truth table (b) Karnaugh map

0

1

0 1

m

0

m

2

m

3

m

1

x

1

x

2

0 0

0 1

1 0

1 1

m

0

m

1

m

3

m

2

x

1

Figure 2.49. Location of two-variable minterms.

50

Figure 2.50. The function of Figure 2.19.

x

1

x

2

1 0

1 1

f x

2

x

1

+ =

0

1

0 1

1

51

Figure 2.51. Location of three-variable minterms.

x

1

x

2

x

3

00 01 11 10

0

1

(b) Karnaugh map

x

2

x

3

0 0

0 1

1 0

1 1

m

0

m

1

m

3

m

2

0

0

0

0

0 0

0 1

1 0

1 1

1

1

1

1

m

4

m

5

m

7

m

6

x

1

(a) Truth table

m

0

m

1

m

3

m

2

m

6

m

7

m

4

m

5

52

Figure 2.52. Examples of three-variable Karnaugh maps.

53

Figure 2.53. A four-variable Karnaugh map.

x

1

x

2

x

3

x

4

00 01 11 10

00

01

11

10

x

2

x

4

x

1

x

3

m

0

m

1

m

5

m

4

m

12

m

13

m

8

m

9

m

3

m

2

m

6

m

7

m

15

m

14

m

11

m

10

54

Figure 2.54. Examples of four-variable Karnaugh maps.

55

Figure 2.55. A five-variable Karnaugh map.

x

1

x

2

x

3

x

4

00 01 11 10

1 1

1 1

1 1

00

01

11

10

x

1

x

2

x

3

x

4

00 01 11 10

1

1 1

1 1

1 1

00

01

11

10

f

1

x

1

x

3

x

1

x

3

x

4

x

1

x

2

x

3

x

5

+ + =

x

5

1 = x

5

0 =

56

Figure 2.56. Three-variable function f (x

1

, x

2

, x

3

) = m(0, 1, 2, 3, 7).

x

1

x

2

x

3

1 1

1 1

x

1

0 0

1 0

00 01 11 10

0

1

x

2

x

3

57

Figure 2.57. Four-variable function f ( x

1

,, x

4

) =

m(2, 3, 5, 6, 7, 10, 11, 13, 14).

x

1

x

2

x

3

x

4

00 01 11 10

1 1

1 1

1 1

00

01

11

10

x

1

x

3

1 1

1

x

3

x

4

x

1

x

2

x

4

x

2

x

3

x

2

x

3

x

4

58

Figure 2.58. The function f ( x

1

,, x

4

) =

m(0, 4, 8, 10, 11, 12, 13, 15).

x

1

x

2

x

3

x

4

00 01 11 10

1

1 1 1 1

1

00

01

11

10

x

1

x

2

x

4

1

1

x

3

x

4

x

1

x

2

x

4

x

1

x

2

x

3

x

1

x

2

x

3

x

1

x

3

x

4

59

Figure 2.59. The function f ( x

1

,, x

4

) =

m(0, 2, 4, 5, 10, 11, 13, 15).

x

1

x

2

x

3

x

4

00 01 11 10

1

1

1

1

1

1

00

01

11

10 1

1

x

1

x

3

x

4

x

2

x

3

x

4

x

2

x

3

x

4

x

1

x

3

x

4

x

1

x

2

x

4

x

1

x

2

x

4

x

1

x

2

x

3

x

1

x

2

x

3

60

Figure 2.60. POS minimization of f (x

1

, x

2

, x

3

) = M(4, 5, 6).

x

1

x

2

x

3

1

00 01 11 10

0

1

1 0 0

1 1 1 0

x

1

x

2

+ ( )

x

1

x

3

+ ( )

61

Figure 2.61. POS minimization of f ( x

1

,, x

4

) =

M(0, 1, 4, 8, 9, 12, 15).

x

1

x

2

x

3

x

4

0

00 01 11 10

0 0 0

0 1 1 0

1 1 0 1

1 1 1 1

00

01

11

10

x

2

x

3

+ ( )

x

3

x

4

+ ( )

x

1

x

2

x

3

x

4

+ + + ( )

62

Figure 2.62. Two implementations of the function f ( x

1

,, x

4

) =

m(2, 4, 5, 6, 10) + D(12, 13, 14, 15).

x

1

x

2

x

3

x

4

0

00 01 11 10

1 d 0

0 1 d 0

0 0 d 0

1 1 d 1

00

01

11

10

x

2

x

3

x

3

x

4

(a) SOP implementation

x

1

x

2

x

3

x

4

0

00 01 11 10

1 d 0

0 1 d 0

0 0 d 0

1 1 d 1

00

01

11

10

x

2

x

3

+ ( )

x

3

x

4

+ ( )

(b) POS implementation

Figure 2.63. Using dont-care minterms when displaying

BCD numbers.

Figure 2.64. An example of multiple-output synthesis.

x

1

x

2

x

3

x

4

00 01 11 10

1 1

1 1

1 1

1 1

00

01

11

10

(a) Function

1

f

1

x

1

x

2

x

3

x

4

00 01 11 10

1 1

1 1

1 1 1

1 1

00

01

11

10

(b) Function f

2

f

1

f

2

x

2

x

3

x

4

x

1

x

3

x

1

x

3

x

2

x

3

x

4

(c) Combined circuit for f

1

f

2

and

Figure 2.65. An example of multiple-output synthesis.

x

1

x

2

x

3

x

4

00 01 11 10

1

1 1

1

00

01

11

10

(a) Optimal realization of (b) Optimal realization of

1

f

3

f

4

(c) Optimal realization of f

3

1

1

x

1

x

2

x

3

x

4

00 01 11 10

1

1 1

1

00

01

11

10

1 1

1

x

1

x

2

x

3

x

4

00 01 11 10

1 1

1

1

00

01

11

10

1

1 1

x

1

x

2

x

3

x

4

00 01 11 10

1 1

1

1

00

01

11

10

1

1 1

and together f

4

f

3

f

4

x

1

x

4

x

3

x

4

x

1

x

1

x

2

x

2

x

4

x

4

(d) Combined circuit for f

3

f

4

and

x

2

Figure 2.66. The Venn diagrams for Example 2.23.

(a) Function A (b) Function B

(c) Function C (d) Function f

x

1

x

3

x

2

x

1

x

2

x

1

x

2

x

1

x

2

x

3

x

3

x

3

67

Figure 2.67. Karnaugh maps for Example 2.26.

Figure 2.68. Karnaugh maps for Example 2.27.

Figure 2.69. A K-map that represents the function in Example 2.28.

70

Figure 2.70. The logic circuit for Example 2.29.

71

Figure 2.70. Verilog code for Example 2.29.

72

Figure 2.72. The circuit for Example 2.30.

73

Figure 2.73. Verilog code for Example 2.30.

74

x

1

x

2

x

3

x

4

(a)

x

1

x

2

x

3

x

4

(b)

Figure P2.1. Two attempts to draw a four-variable Venn diagram.

75

x

3

x

2

x

1

x

4

x

3

x

2

x

1

m

0

m

1

m

2

Figure P2.2. A four-variable Venn diagram.

76

Figure P2.3. A timing diagram representing a logic function.

1

0

1

0

1

0

1

0

x

1

x

2

Time

x

3

f

77

1

0

1

0

1

0

1

0

x

1

x

2

Time

x

3

f

Figure P2.4. A timing diagram representing a logic function.

78

Figure P2.5. Circuit for problem 2.78.

f

g

x

2

x

4

x

4

x

1

x

3

x

1

x

3

x

2

x

3

x

4

x

1

x

3

x

4

x

2

x

1

x

1

x

4

x

3

x

1

x

4

Figure P2.6. Circuit for problem 2.79.

x

1

x

2

x

2

x

1

x

3

x

4

x

2

x

1

x

2

x

3

x

1

x

3

x

2

g

f

S-ar putea să vă placă și

- Analytic Geometry: Graphic Solutions Using Matlab LanguageDe la EverandAnalytic Geometry: Graphic Solutions Using Matlab LanguageÎncă nu există evaluări

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesDe la EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesEvaluare: 1.5 din 5 stele1.5/5 (2)

- Digital Logic Ideal Solution Ch2Document14 paginiDigital Logic Ideal Solution Ch2Abdullah Muhammad AlmubaileshÎncă nu există evaluări

- m20 Rev3 - Dugopolski - PDFDocument2 paginim20 Rev3 - Dugopolski - PDFSkyezine Via Kit FoxÎncă nu există evaluări

- MATH 223: Calculus II: Dr. Joseph K. AnsongDocument38 paginiMATH 223: Calculus II: Dr. Joseph K. AnsongTennysonÎncă nu există evaluări

- Principles of Econometrics 4e Chapter 2 SolutionDocument33 paginiPrinciples of Econometrics 4e Chapter 2 SolutionHoyin Kwok84% (19)

- Additional Mathematics CXC 2014 SolvedDocument5 paginiAdditional Mathematics CXC 2014 SolvedAbigail Johnson67% (24)

- FunctionsDocument9 paginiFunctions叶蕊雅Încă nu există evaluări

- Calcprobonly PDFDocument71 paginiCalcprobonly PDFSLKÎncă nu există evaluări

- Rexercises 1 R BasicDocument35 paginiRexercises 1 R BasicJohn StephenÎncă nu există evaluări

- 1 3 ProblemsDocument6 pagini1 3 ProblemsKelseyÎncă nu există evaluări

- Math Camp Sample Problems F 2016Document3 paginiMath Camp Sample Problems F 2016Nam Giang HàÎncă nu există evaluări

- Verlogic3 Chapter2Document80 paginiVerlogic3 Chapter2tiến nam nguyễnÎncă nu există evaluări

- UntitledDocument6 paginiUntitledxRubnzxÎncă nu există evaluări

- 2201 Test 2 Quadratics 2014Document5 pagini2201 Test 2 Quadratics 2014Jonah Micah Milan MangacoÎncă nu există evaluări

- 11SAT Review Pack AnswerkeyDocument18 pagini11SAT Review Pack AnswerkeyAyman YehyaÎncă nu există evaluări

- Tutorial CalculusDocument2 paginiTutorial CalculusphilibethenockÎncă nu există evaluări

- 2012 Differentiation Barely PassedDocument10 pagini2012 Differentiation Barely PassedcsanjeevanÎncă nu există evaluări

- Assignment 3Document7 paginiAssignment 3sanaullah sanyÎncă nu există evaluări

- CCP Math Test PracticeDocument5 paginiCCP Math Test PracticestaticsccpÎncă nu există evaluări

- M2 R08 MayJune 10Document3 paginiM2 R08 MayJune 10shibhiÎncă nu există evaluări

- G9 Math Q1 - Week 4 - Solving Quadratic EquationDocument63 paginiG9 Math Q1 - Week 4 - Solving Quadratic EquationMechael ManzanoÎncă nu există evaluări

- Practice B Module 1 2Document5 paginiPractice B Module 1 2api-257938314Încă nu există evaluări

- Sheet 1Document2 paginiSheet 1mohamedÎncă nu există evaluări

- 2003 Test BDocument10 pagini2003 Test BDerny FleurimaÎncă nu există evaluări

- Answer SolutionDocument65 paginiAnswer SolutionjibranqqÎncă nu există evaluări

- Edexcel C3 June 2005 To June 2011 All Questions Mark SchemeDocument44 paginiEdexcel C3 June 2005 To June 2011 All Questions Mark SchemeOrhan AtestemurÎncă nu există evaluări

- 3 PDF Covariance VariogramDocument22 pagini3 PDF Covariance VariogramTeguh Akbar HarahapÎncă nu există evaluări

- Engineering Mathematics II Model Question Paper StudyhauntersDocument3 paginiEngineering Mathematics II Model Question Paper StudyhauntersSriram JÎncă nu există evaluări

- Mathematics s.2 2222222222Document5 paginiMathematics s.2 2222222222BashirÎncă nu există evaluări

- Exercise Chapter 3Document26 paginiExercise Chapter 3Samuel Sim Shien ShuangÎncă nu există evaluări

- Extremum and Concavity of A Single Variable FunctionDocument6 paginiExtremum and Concavity of A Single Variable FunctionAbirami SÎncă nu există evaluări

- Calculus NoteDocument95 paginiCalculus NoteAfeef Abu BakarÎncă nu există evaluări

- ODD01Document21 paginiODD01ilovedamonsalvatore3Încă nu există evaluări

- Unit 7 Test Review Fall 2021Document2 paginiUnit 7 Test Review Fall 2021BobÎncă nu există evaluări

- Developing Models For OptimizationDocument29 paginiDeveloping Models For OptimizationmohammadÎncă nu există evaluări

- Chapter2 - Problems of Chapter 2Document48 paginiChapter2 - Problems of Chapter 2Vuthy Chey100% (1)

- Redch 0Document22 paginiRedch 0zaqwaÎncă nu există evaluări

- Math 8 1.2Document30 paginiMath 8 1.2Via Camille Hermoso JavierÎncă nu există evaluări

- m26 Rev3t PDFDocument2 paginim26 Rev3t PDFSkyezine Via Kit FoxÎncă nu există evaluări

- UNIT 02 - DifferentiationDocument45 paginiUNIT 02 - DifferentiationFaiZul IshAkÎncă nu există evaluări

- 3 Techniques of Differentiation 44Document20 pagini3 Techniques of Differentiation 44Edgar LinaresÎncă nu există evaluări

- Homework 01 FunctionsDocument1 paginăHomework 01 FunctionsdiegoadjgtÎncă nu există evaluări

- Tutorial 1Document5 paginiTutorial 1Snehal SolankeÎncă nu există evaluări

- FKB20203-Tutorial (Limits and Continuity)Document12 paginiFKB20203-Tutorial (Limits and Continuity)Shafinaz ChachaÎncă nu există evaluări

- Salas S, Hille E., Etgen G. Calculus. One and Several Variables (10ed., Wiley, 2007) (ISBN 0471698040) (O) (1171s) - MCet - (已拖移)Document3 paginiSalas S, Hille E., Etgen G. Calculus. One and Several Variables (10ed., Wiley, 2007) (ISBN 0471698040) (O) (1171s) - MCet - (已拖移)He Xin HanÎncă nu există evaluări

- Tutorial 3 (Chapter4 Interpolation)Document3 paginiTutorial 3 (Chapter4 Interpolation)Mahfuzah MustaphaÎncă nu există evaluări

- Scientific Computing Selected SolutionsDocument3 paginiScientific Computing Selected Solutionsnomitav1150% (2)

- Kvadrat BinomaDocument0 paginiKvadrat BinomaAleksandar JerinicÎncă nu există evaluări

- Calculus I (1,2,3,4) RevisionDocument6 paginiCalculus I (1,2,3,4) RevisionYousra AzabÎncă nu există evaluări

- B.E. Degree Examinations: April/May 2011Document4 paginiB.E. Degree Examinations: April/May 2011Dhanabal Palanisamy PÎncă nu există evaluări

- Chapter 02Document24 paginiChapter 02Jennifer BennettÎncă nu există evaluări

- Chapter 2 - Graphs of Functions IIDocument18 paginiChapter 2 - Graphs of Functions IInasir6165Încă nu există evaluări

- Assignment 2 SQQM1023 A111Document3 paginiAssignment 2 SQQM1023 A111Syuhada RosliÎncă nu există evaluări

- Calculus Test 2 Study GuideDocument20 paginiCalculus Test 2 Study GuideSpencer ThomasÎncă nu există evaluări

- Tut 6Document4 paginiTut 6Batrisya LeeÎncă nu există evaluări

- Problem Collection PDFDocument40 paginiProblem Collection PDFDIEGO MARTIN MAESOÎncă nu există evaluări

- MCR3U7 Review QuestionsDocument4 paginiMCR3U7 Review QuestionsAD - 10PJ 960521 Turner Fenton SSÎncă nu există evaluări

- Test Bank for Precalculus: Functions & GraphsDe la EverandTest Bank for Precalculus: Functions & GraphsEvaluare: 5 din 5 stele5/5 (1)

- Linear Programming and Resource Allocation ModelingDe la EverandLinear Programming and Resource Allocation ModelingÎncă nu există evaluări

- Thickness Effect On Flame Spread Characteristics of Expanded Polystyrene in Different EnvironmentsDocument12 paginiThickness Effect On Flame Spread Characteristics of Expanded Polystyrene in Different EnvironmentsKarimovaRaikhanovnaÎncă nu există evaluări

- Test KMEE1168 2009 Sem 1Document1 paginăTest KMEE1168 2009 Sem 1KarimovaRaikhanovnaÎncă nu există evaluări

- Scopus ResultsDocument1 paginăScopus ResultsKarimovaRaikhanovnaÎncă nu există evaluări

- Exam English 2008Document4 paginiExam English 2008KarimovaRaikhanovnaÎncă nu există evaluări

- Figure 1a Figure 1bDocument33 paginiFigure 1a Figure 1bKarimovaRaikhanovnaÎncă nu există evaluări

- Theory: Ac Through Pure Ohmic Resistance AloneDocument18 paginiTheory: Ac Through Pure Ohmic Resistance AloneKarimovaRaikhanovnaÎncă nu există evaluări

- Electronic Computers Then and NowDocument17 paginiElectronic Computers Then and NowKarimovaRaikhanovnaÎncă nu există evaluări

- Solution Mid Term Test 2015Document3 paginiSolution Mid Term Test 2015KarimovaRaikhanovnaÎncă nu există evaluări

- Bce Final Notes DbacerDocument75 paginiBce Final Notes DbacerKarimovaRaikhanovnaÎncă nu există evaluări

- Types of Computers: Introduction To Computer SystemsDocument7 paginiTypes of Computers: Introduction To Computer SystemsKarimovaRaikhanovnaÎncă nu există evaluări

- Assignment: Data Communication (Keew3202) Student: Indira Karimova (Kew100701)Document6 paginiAssignment: Data Communication (Keew3202) Student: Indira Karimova (Kew100701)KarimovaRaikhanovnaÎncă nu există evaluări

- Tutorial 3 - Proposal & AcceptanceDocument13 paginiTutorial 3 - Proposal & AcceptanceKarimovaRaikhanovnaÎncă nu există evaluări

- East Halmahera Ferronickel Development Project (P3Fh Project)Document2 paginiEast Halmahera Ferronickel Development Project (P3Fh Project)nailulfalah17Încă nu există evaluări

- Sony CDX-G3100UE, G3100UV, G3150UP, G3150UV PDFDocument38 paginiSony CDX-G3100UE, G3100UV, G3150UP, G3150UV PDFboroda2410Încă nu există evaluări

- TASKalfa 420i 520i (SM)Document504 paginiTASKalfa 420i 520i (SM)Joshua Wilson50% (2)

- Viewsonic vx1937w WM W-Led vs12825-1 vs13679-1 SM Rev.1b 2010Document118 paginiViewsonic vx1937w WM W-Led vs12825-1 vs13679-1 SM Rev.1b 2010Carlos A. TorresÎncă nu există evaluări

- Indicating InstrumentsDocument26 paginiIndicating InstrumentsSweetMaina100% (1)

- Information Technology Past Paper June 2006Document9 paginiInformation Technology Past Paper June 2006Dudley Clarke75% (4)

- 1 - Angle ModulationDocument34 pagini1 - Angle ModulationNilegn Vllgn100% (1)

- C191HM Powermeter and Harmonic Manager CommunicationsDocument30 paginiC191HM Powermeter and Harmonic Manager CommunicationsRoberto GarridoÎncă nu există evaluări

- M5500 Web1Document2 paginiM5500 Web1luis rangelÎncă nu există evaluări

- Applications and Processing of CeramicsDocument17 paginiApplications and Processing of CeramicsTasnim Arif100% (1)

- Cation ConductivityDocument8 paginiCation ConductivityJayanath Nuwan SameeraÎncă nu există evaluări

- Ieee Paper 1Document12 paginiIeee Paper 1angel0712Încă nu există evaluări

- BA Fieldbus Module Type 2131 Profibus enDocument60 paginiBA Fieldbus Module Type 2131 Profibus enGuillermo Osvaldo Rivera MelladoÎncă nu există evaluări

- Experiment No - 14Document8 paginiExperiment No - 14Konem SolutionsÎncă nu există evaluări

- IntegratorDocument2 paginiIntegratorlabdownloadÎncă nu există evaluări

- Tutorial - 2: Boolean Algebra & Combinational LogicDocument15 paginiTutorial - 2: Boolean Algebra & Combinational LogicShreyash SillÎncă nu există evaluări

- EIE FormatDocument13 paginiEIE Formatapi-19989949Încă nu există evaluări

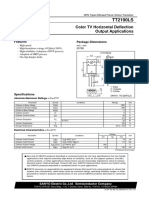

- TT2190LS: Color TV Horizontal Deflection Output ApplicationsDocument4 paginiTT2190LS: Color TV Horizontal Deflection Output ApplicationsFreddyÎncă nu există evaluări

- Operating Manual: CAL ControlsDocument39 paginiOperating Manual: CAL ControlskmpoulosÎncă nu există evaluări

- GCT1 CompsDocument7 paginiGCT1 CompsDelta VisionÎncă nu există evaluări

- (CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100Document10 pagini(CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100krazykrnxboyÎncă nu există evaluări

- Manual: Installation & UserDocument39 paginiManual: Installation & UserAthan CruzÎncă nu există evaluări

- Commodore Magazine Vol-08-N09 1987 SepDocument132 paginiCommodore Magazine Vol-08-N09 1987 SepSteven DÎncă nu există evaluări

- 1KW 60782 0 - AC DC - PowerSupplyTestingAppNote PDFDocument16 pagini1KW 60782 0 - AC DC - PowerSupplyTestingAppNote PDFNamÎncă nu există evaluări

- Make A Ribbon ControllerDocument16 paginiMake A Ribbon ControllerVaclav MullerÎncă nu există evaluări

- ET End Sem18Document3 paginiET End Sem18venkatarao HanumanthuÎncă nu există evaluări

- Intel® PXA270 Processor: Electrical, Mechanical, and Thermal SpecificationDocument130 paginiIntel® PXA270 Processor: Electrical, Mechanical, and Thermal SpecificationMilton DavidÎncă nu există evaluări

- Magnetics Powder Core Material Developments PDFDocument30 paginiMagnetics Powder Core Material Developments PDFVenkateswaran KrishnamurthyÎncă nu există evaluări

- Speedybee F7V3 Stack ENDocument1 paginăSpeedybee F7V3 Stack ENPaulo DinisÎncă nu există evaluări