Documente Academic

Documente Profesional

Documente Cultură

Lec 15 COAL Interrupts

Încărcat de

Rai Hessy100%(1)100% au considerat acest document util (1 vot)

150 vizualizări13 paginiThe document discusses interrupts in the 8086 microprocessor. There are five types of interrupts: hardware, non-maskable, software, internal, and reset. When an interrupt occurs, the CPU pushes flags and return address to the stack and fetches the interrupt service routine address from the interrupt vector table. The interrupt service routine executes and returns using the IRET instruction to resume the original program. Common sources of interrupts are timers, keyboards, disks, and other peripheral devices.

Descriere originală:

coal interputs

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PPTX, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentThe document discusses interrupts in the 8086 microprocessor. There are five types of interrupts: hardware, non-maskable, software, internal, and reset. When an interrupt occurs, the CPU pushes flags and return address to the stack and fetches the interrupt service routine address from the interrupt vector table. The interrupt service routine executes and returns using the IRET instruction to resume the original program. Common sources of interrupts are timers, keyboards, disks, and other peripheral devices.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPTX, PDF, TXT sau citiți online pe Scribd

100%(1)100% au considerat acest document util (1 vot)

150 vizualizări13 paginiLec 15 COAL Interrupts

Încărcat de

Rai HessyThe document discusses interrupts in the 8086 microprocessor. There are five types of interrupts: hardware, non-maskable, software, internal, and reset. When an interrupt occurs, the CPU pushes flags and return address to the stack and fetches the interrupt service routine address from the interrupt vector table. The interrupt service routine executes and returns using the IRET instruction to resume the original program. Common sources of interrupts are timers, keyboards, disks, and other peripheral devices.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPTX, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 13

“8086 Interrupts”

Lecture-15

M. M. Yasin

myasin@ciitsahiwal.edu.pk

Fall 2015 - M. M. Yasin 1.1

“8086 Interrupts”

Introduction

An interrupt is the method of processing the

microprocessor by a peripheral device. It is used to cause a

temporary halt in the execution of a program.

Microprocessor responds to the interrupt with an

interrupt service routine, which is a short program or

subroutine that instructs the microprocessor on how to

handle the interrupt.

There are two basic type of interrupts:

(1) Non-Maskable: It requires an immediate response by

microprocessor, usually used for serious circumstances like

power failure.

(2) Maskable: Microprocessor can ignore it depending upon

some predetermined conditions.

Fall 2015 - M. M. Yasin 1.2

“8086 Interrupts”

Interrupt can be divided into five groups:

1. Hardware interrupt

2. Non-Maskable interrupt

3. Software interrupt

4. Internal interrupt

5. Reset

Fall 2015 - M. M. Yasin 1.3

“8086 Interrupts”

Hardware, Software and Internal interrupts are serviced on

priority basis.

Each interrupt is given a different priority level by assigning it

a type number. Type 0 identifies the highest-priority and type

255 identifies the lowest- priority interrupt.

The 80x86 chips allow up to 256 vectored interrupts. This

means that you can have up to 256 different sources for an

interrupt and the 80x86 will directly call the service routine

for that interrupt without any software processing.

(This is in contrast to non-vectored interrupts that transfer control directly

to a single interrupt service routine, regardless of the interrupt source).

Fall 2015 - M. M. Yasin 1.4

“8086 Interrupts”

Interrupt Vector Table Details

The 80x86 provides a 256 entry interrupt vector table

beginning at address 0:0 in memory. This is a 1K table

containing 256 4-byte entries.

Each entry in this table contains a segmented address that

points at the interrupt service routine in memory.

Int 0 4: Dedicated to specific interrupts, details in the next

slide.

Int 5 31: Reserved by Intel for use in future

microprocessors.

Int 32 255: Available to use for hardware and software

interrupts.

Fall 2015 - M. M. Yasin 1.5

“8086 Interrupts”

Details of INT 0 4

INT 0: Known as divide by zero interrupt. For cases where the

quotient becomes particularly large to be placed.

INT 1: Known as single step interrupt. This type of interrupt is

primarily used for debugging purposes in assembly language.

INT 2: Also known as Non-Maskable NMI interrupt. These

type of interrupts are used for emergency scenarios such as

power failure.

INT 3: Breakpoint interrupts. When this interrupt occurs, a

program would execute up to its break point.

INT 4: Also known as overflow interrupt, is generally existent

after an arithmetic operation was performed.

Fall 2015 - M. M. Yasin 1.6

“8086 Interrupts”

What happens when an Interrupt occurs

When an interrupt occurs, regardless of the source, the 80x86

does the following:

1. The CPU pushes the flags register onto the stack.

2. The CPU pushes a far return address (segment:offset) onto

the stack, segment value first.

3. The CPU determines the cause of the interrupt (i.e., the

interrupt number) and fetches the four byte interrupt vector

from address 0:vector*4.

– The interrupt type N is sent to the Central Processor Unit (CPU) via

the Data bus from the hardware interface.

– The interrupt vector contents are fetched, from (4 x N) and then

placed into the IP and from (4 x N +2) into the CS.

Fall 2015 - M. M. Yasin 1.7

“8086 Interrupts”

4. The CPU transfers control to the routine specified by the

interrupt vector table entry.

What happens when an Interrupt Service Routine finishes…

When the interrupt service routine wants to return control, it

must execute an IRET (interrupt return) instruction. The

interrupt return pops the return address and the flags off the

stack.

Fall 2015 - M. M. Yasin 1.8

“8086 Interrupts”

Hardware Interrupt

The primary sources of interrupts are the PCs timer chip,

keyboard, serial ports, parallel ports, disk drives, CMOS real-

time clock, mouse, sound cards, and other peripheral devices.

Non-Maskable Interrupt (NMI)

The processor provides a single non-maskable interrupt pin

(NMI) which has higher priority than the maskable interrupt

request pin (INTR). A typical use would be to activate a power

failure routine.

Fall 2015 - M. M. Yasin 1.9

“8086 Interrupts”

Maskable Interrupt

Whenever an external signal activates the INTR pin, the

microprocessor will be interrupted only if interrupts are

enabled using set interrupt Flag instruction.

If the interrupts are disabled using clear interrupt Flag

instruction, the microprocessor will not get interrupted even

if INTR is activated. That is, INTR can be masked.

INTR is a non vectored interrupt, which means, the 8086 does

not know where to branch to service the interrupt. The 8086

has to be told by an external device like a Programmable

Interrupt controller regarding the branch.

Fall 2015 - M. M. Yasin 1.10

“8086 Interrupts”

Software Interrupt Instructions

There are instructions in 8086 which cause an interrupt.

They are INT instructions with type number specified.

For example, INT 3 instruction. It’s a Break Point Interrupt

instruction.

When a break point is inserted, the system executes the

instructions up to the breakpoint, and then goes to the break

point procedure.

Unlike the single-Step feature which stops execution after

each instruction, the breakpoint feature executes all the

instructions up to the inserted breakpoint and then stops

execution.

Fall 2015 - M. M. Yasin 1.11

“8086 Interrupts”

Reset

Processor initialization or start up is accomplished with

activation (HIGH) of the RESET pin.

The 8086 RESET is required to be HIGH for greater than 4 CLK

cycles.

The 8086 will terminate operations on the high-going edge of

RESET and will remain inactive as long as RESET is HIGH.

The low-going transition of RESET triggers an internal reset

sequence for approximately 10 CLK cycles. After this interval

the 8086 operates normally beginning with the instruction in

absolute location FFFF0H.

Fall 2015 - M. M. Yasin 1.12

“8086 Interrupts”

Reset

Table: Process initialization register content

Fall 2015 - M. M. Yasin 1.13

S-ar putea să vă placă și

- Interrupts in 8086Document4 paginiInterrupts in 8086Radhakrishna100% (1)

- Database Recovery TechnequesDocument25 paginiDatabase Recovery Technequesusman saleem100% (1)

- Introduction To MicroprocessorDocument31 paginiIntroduction To MicroprocessorMuhammad DawoodÎncă nu există evaluări

- Easy8051 v6 Development SystemDocument4 paginiEasy8051 v6 Development SystemShobhit SinghÎncă nu există evaluări

- Ec2304 LP III EceDocument5 paginiEc2304 LP III EcesunvenkatÎncă nu există evaluări

- Real Time Systems NotesDocument127 paginiReal Time Systems NotesVijay Kumar100% (1)

- A Comprehensive Study of Intel Core I3, I5 and I7 Family: Presentation (2) 'Document29 paginiA Comprehensive Study of Intel Core I3, I5 and I7 Family: Presentation (2) 'Ian John MontalboÎncă nu există evaluări

- Embedded Systems: ARM Programming and OptimizationDe la EverandEmbedded Systems: ARM Programming and OptimizationÎncă nu există evaluări

- Vxworks - Final PDFDocument125 paginiVxworks - Final PDFBhanu Prakash K100% (1)

- Compilation 1,2,3Document7 paginiCompilation 1,2,3Kharolina BautistaÎncă nu există evaluări

- VX Worksproject 10Document32 paginiVX Worksproject 10Abhay Kumar Sahu100% (1)

- 8087 Numeric Data Co ProcessorDocument22 pagini8087 Numeric Data Co ProcessorAbhishek SinghÎncă nu există evaluări

- Lab 1Document7 paginiLab 1Tanjila Islam Ritu 1811017642Încă nu există evaluări

- Analyzing Kernel Crash On Red HatDocument9 paginiAnalyzing Kernel Crash On Red Hatalexms10Încă nu există evaluări

- 8085 Complete ArchitectureDocument39 pagini8085 Complete ArchitectureSana KhanÎncă nu există evaluări

- CSE-232 LAB ManualDocument23 paginiCSE-232 LAB ManualMuhammad UsmanÎncă nu există evaluări

- The Fetch and Execute Cycle: Machine Language: Next SectionDocument36 paginiThe Fetch and Execute Cycle: Machine Language: Next SectionSurageÎncă nu există evaluări

- Lab Assignment 2: MIPS Single-Cycle Implementation: Electrical and Computer Engineering University of CyprusDocument23 paginiLab Assignment 2: MIPS Single-Cycle Implementation: Electrical and Computer Engineering University of CyprusNguyễn Trường Giang100% (1)

- CS1203 System Software UNIT I Question AnsDocument10 paginiCS1203 System Software UNIT I Question AnskeerthisivaÎncă nu există evaluări

- Win862 User ManualDocument9 paginiWin862 User ManualktweiÎncă nu există evaluări

- Ee8551 8085 NotesDocument31 paginiEe8551 8085 NotesKUMARANSCRÎncă nu există evaluări

- Hands On Contiki OS and Cooja Simulator: Exercises (Part II)Document15 paginiHands On Contiki OS and Cooja Simulator: Exercises (Part II)Vassilios KotsiouÎncă nu există evaluări

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationDocument13 paginiUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaÎncă nu există evaluări

- Internal Architecture 8086Document3 paginiInternal Architecture 8086firoz83% (6)

- Lab 2 No AnswersDocument2 paginiLab 2 No Answersnemanja0% (1)

- Priority Assignment in Waiting Line ProblemsDocument8 paginiPriority Assignment in Waiting Line ProblemsmduhovichÎncă nu există evaluări

- Assignment 1Document4 paginiAssignment 1ashar565Încă nu există evaluări

- Comparison of Windows and LinuxDocument35 paginiComparison of Windows and LinuxgeethuuuuÎncă nu există evaluări

- AC58-AT58 Computer OrganizationDocument26 paginiAC58-AT58 Computer OrganizationSaqib KamalÎncă nu există evaluări

- Kernel Overview: Differences Between Kernel Modules and User ProgramsDocument12 paginiKernel Overview: Differences Between Kernel Modules and User ProgramsvirendrakumarthakurÎncă nu există evaluări

- DSPecelabmanualDocument108 paginiDSPecelabmanualmailmeasddÎncă nu există evaluări

- Very Simple Threading ExampleDocument38 paginiVery Simple Threading ExamplephanishyamnagaÎncă nu există evaluări

- 7.1.2.8 Lab - Using The Windows Calculator With Network AddressesDocument10 pagini7.1.2.8 Lab - Using The Windows Calculator With Network AddressesParthPatel100% (2)

- Lecture05 - 8086 AssemblyDocument43 paginiLecture05 - 8086 Assemblytesfu zewduÎncă nu există evaluări

- Assembly LanguageDocument7 paginiAssembly LanguageFranchezka YuÎncă nu există evaluări

- Lecture 15 8086 StackDocument37 paginiLecture 15 8086 Stackfreddy tanatsaÎncă nu există evaluări

- Microprocessor 8088Document11 paginiMicroprocessor 8088bobby khanÎncă nu există evaluări

- Cross Compiler & Assembler & LinkerDocument37 paginiCross Compiler & Assembler & Linkervarun2313676Încă nu există evaluări

- Chapter 8 - PipeliningDocument38 paginiChapter 8 - Pipeliningnagpal3Încă nu există evaluări

- CHAPTER - 07 / LECTURE - 01 / Data Link LayerDocument8 paginiCHAPTER - 07 / LECTURE - 01 / Data Link LayerNagaraj VaratharajÎncă nu există evaluări

- Advanced Microprocessor PDFDocument1 paginăAdvanced Microprocessor PDFAmish Tankariya50% (2)

- Lab 06Document4 paginiLab 06xyzs8386100% (1)

- Group 6 Cpu Design PresentationDocument50 paginiGroup 6 Cpu Design PresentationFerry AriÎncă nu există evaluări

- Dos and Bios InterruptsDocument4 paginiDos and Bios Interruptscpsrinivasu1221569100% (1)

- Debugger XtensaDocument68 paginiDebugger Xtensacarver_uaÎncă nu există evaluări

- Chapter 9: 8086/8088 Hardware SpecificationsDocument28 paginiChapter 9: 8086/8088 Hardware SpecificationsChanchan LebumfacilÎncă nu există evaluări

- Low Level C Programming PDFDocument30 paginiLow Level C Programming PDFlucadeldiabloÎncă nu există evaluări

- Group Assignment: Technology Park MalaysiaDocument46 paginiGroup Assignment: Technology Park MalaysiaKesikan Velan50% (2)

- DsPIC30F4011 - Robotics 3Document33 paginiDsPIC30F4011 - Robotics 3Senthil Kumar100% (1)

- Chapter 4 Microprocessor SystemDocument71 paginiChapter 4 Microprocessor SystemGetTrendingÎncă nu există evaluări

- Ucos II IntroDocument49 paginiUcos II IntroprincegirishÎncă nu există evaluări

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocument8 paginiRipple Carry and Carry Lookahead Adders: 1 ObjectivesYasser RaoufÎncă nu există evaluări

- Boano Thesis 2009Document172 paginiBoano Thesis 2009cjwangÎncă nu există evaluări

- 8051 Microcontroller FAQDocument160 pagini8051 Microcontroller FAQkranthi633Încă nu există evaluări

- Hawk BoardDocument7 paginiHawk BoardVijay P PulavarthiÎncă nu există evaluări

- QuizDocument1 paginăQuizRai HessyÎncă nu există evaluări

- Review 4Document3 paginiReview 4Rai HessyÎncă nu există evaluări

- Lab ManualDocument12 paginiLab ManualRai HessyÎncă nu există evaluări

- ProblemDocument7 paginiProblemRai HessyÎncă nu există evaluări

- Mega Hertz (MHZ) Giga Hertz (GHZ) - Both A, B NoneDocument2 paginiMega Hertz (MHZ) Giga Hertz (GHZ) - Both A, B NoneRai HessyÎncă nu există evaluări

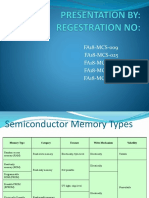

- Fa18-Mcs-009 Fa18-Mcs-025 Fa18-Mcs-029 Fa18-Mcs-036 Fa18-Mcs-040Document22 paginiFa18-Mcs-009 Fa18-Mcs-025 Fa18-Mcs-029 Fa18-Mcs-036 Fa18-Mcs-040Rai HessyÎncă nu există evaluări

- COAL PresentationDocument11 paginiCOAL PresentationRai HessyÎncă nu există evaluări

- Sagan WaltzDocument14 paginiSagan WaltzKathleen RoseÎncă nu există evaluări

- Evelyn Arizpe - Teresa Colomer - Carmen Martínez-Roldán - Visual Journeys Through Wordless Narratives - An International Inquiry With Immigrant Children and The Arrival-Bloomsbury Academic (2014)Document290 paginiEvelyn Arizpe - Teresa Colomer - Carmen Martínez-Roldán - Visual Journeys Through Wordless Narratives - An International Inquiry With Immigrant Children and The Arrival-Bloomsbury Academic (2014)Lucia QuirogaÎncă nu există evaluări

- Paper 3 FrinqDocument4 paginiPaper 3 Frinqapi-301975170Încă nu există evaluări

- Compact Switch: Series 96201, 96211, 96221Document2 paginiCompact Switch: Series 96201, 96211, 96221Sales DIGIHU100% (1)

- Moodle2Word Word Template: Startup Menu: Supported Question TypesDocument6 paginiMoodle2Word Word Template: Startup Menu: Supported Question TypesinamÎncă nu există evaluări

- April FoolDocument179 paginiApril FoolrogeraccuraÎncă nu există evaluări

- Internet in My LifeDocument4 paginiInternet in My LifeАндріана ПрусÎncă nu există evaluări

- Joy BoosterDocument2 paginiJoy BoosterAlexsandro TorezinÎncă nu există evaluări

- The Status of The Translation ProfessionDocument172 paginiThe Status of The Translation ProfessionVeaceslav MusteataÎncă nu există evaluări

- SOP For Production DepartmentDocument5 paginiSOP For Production DepartmentDaniel SusantoÎncă nu există evaluări

- Sensory Play Activities Kids Will LoveDocument5 paginiSensory Play Activities Kids Will LoveGoh KokMingÎncă nu există evaluări

- PMP Exam Questions and Answers PDFDocument12 paginiPMP Exam Questions and Answers PDFAshwin Raghav SankarÎncă nu există evaluări

- Abbreviations For O&G IndustryDocument38 paginiAbbreviations For O&G IndustryMike George MeyerÎncă nu există evaluări

- T.Y.B.B.A. (CA) Sem VI Practical Slips 2019 PatternDocument30 paginiT.Y.B.B.A. (CA) Sem VI Practical Slips 2019 PatternJai Ramteke100% (2)

- Design and Fabrication of Light Electric VehicleDocument14 paginiDesign and Fabrication of Light Electric VehicleAshish NegiÎncă nu există evaluări

- Sequence Analytical and Vector Geometry at Teaching of Solid Geometry at Secondary SchoolDocument10 paginiSequence Analytical and Vector Geometry at Teaching of Solid Geometry at Secondary SchoolJuan S. PalmaÎncă nu există evaluări

- Syllabus ClinPhar143Document2 paginiSyllabus ClinPhar143Angel GoÎncă nu există evaluări

- Syllabus (2020) : NTA UGC-NET Computer Science and ApplicationsDocument24 paginiSyllabus (2020) : NTA UGC-NET Computer Science and ApplicationsDiksha NagpalÎncă nu există evaluări

- Heat and Mass Chapter 2Document49 paginiHeat and Mass Chapter 2Mvelo PhungulaÎncă nu există evaluări

- AMST 398 SyllabusDocument7 paginiAMST 398 SyllabusNatÎncă nu există evaluări

- Gulfpub Wo 201805Document81 paginiGulfpub Wo 201805Patricia.PÎncă nu există evaluări

- Jazz - Installing LED DRLsDocument16 paginiJazz - Installing LED DRLsKrishnaÎncă nu există evaluări

- Eps 400 New Notes Dec 15-1Document47 paginiEps 400 New Notes Dec 15-1BRIAN MWANGIÎncă nu există evaluări

- 0 - Danica Joy v. RallecaDocument2 pagini0 - Danica Joy v. RallecaRandy Jake Calizo BaluscangÎncă nu există evaluări

- Extension of MDRRMO OfficeDocument12 paginiExtension of MDRRMO OfficeJustin YuabÎncă nu există evaluări

- How Plants SurviveDocument16 paginiHow Plants SurviveGilbertÎncă nu există evaluări

- Bruner, Jerome - The Growth of MindDocument11 paginiBruner, Jerome - The Growth of MindTalia Tijero100% (1)

- The Goldfish and Its Culture. Mulertt PDFDocument190 paginiThe Goldfish and Its Culture. Mulertt PDFjr2010peruÎncă nu există evaluări

- Mechanical Energy Storage: Created by Nick StroudDocument24 paginiMechanical Energy Storage: Created by Nick StroudAli ShazanÎncă nu există evaluări

- EtchDocument2 paginiEtchlex bactolÎncă nu există evaluări