Documente Academic

Documente Profesional

Documente Cultură

Chapter 2

Încărcat de

aregawi weleabezgi0 evaluări0% au considerat acest document util (0 voturi)

31 vizualizări114 paginiA computer system consists of a processor, memory, I/O, and interconnections between these components. Data and instructions are stored together in memory and can be addressed without regard to type. The memory hierarchy ranges from fast but expensive and small registers and caches to larger but slower disks and tapes. This arrangement balances the tradeoffs between capacity, access time, and cost for the overall system.

Descriere originală:

Titlu original

Chapter 2.pptx

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PPTX, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentA computer system consists of a processor, memory, I/O, and interconnections between these components. Data and instructions are stored together in memory and can be addressed without regard to type. The memory hierarchy ranges from fast but expensive and small registers and caches to larger but slower disks and tapes. This arrangement balances the tradeoffs between capacity, access time, and cost for the overall system.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPTX, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

31 vizualizări114 paginiChapter 2

Încărcat de

aregawi weleabezgiA computer system consists of a processor, memory, I/O, and interconnections between these components. Data and instructions are stored together in memory and can be addressed without regard to type. The memory hierarchy ranges from fast but expensive and small registers and caches to larger but slower disks and tapes. This arrangement balances the tradeoffs between capacity, access time, and cost for the overall system.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PPTX, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 114

CHAPTER TWO

COMPUTER SYSTEM

2.1 MEMORY SYSTEMS

1 perpared by LieltiTse 11/5/2019

Computer System

A computer system consists of a processor, memory, I/O, and

the interconnections among these major components.

The functional behavior of the system consists of the exchange of

data and control signals among these components.

To support this exchange these components must be

interconnected.

2 perpared by LieltiTse 11/5/2019

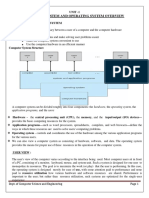

Computer Components

3 perpared by LieltiTse 11/5/2019

Computer Component

Virtually all contemporary computer designs are based on

concepts referred to as von Neumann architecture.

Von Neumann architecture is based on three key concepts.

Data and instructions are stored in a single read-write

memory.

Contents of this memory are addressable by location, without

regard to the type of data contained there.

Execution occurs in a sequential fashion from one instruction

to the next.

4 perpared by LieltiTse 11/5/2019

Computer Component

CPU exchanges data with memory. For this purpose, it typically

makes use of two internal registers:

A memory address register (MAR), which specifies the address

in memory for the next read or write.

A memory buffer register (MBR), which contains the data to be

written into memory or receives the data read from memory.

Similarly, an I/O address register(I/OAR) specifies a particular

I/O device.

An I/O buffer (I/OBR) register is used for the exchange of data

between an I/O module and the CPU.

An I/O module transfers data from external devices to CPU and

memory, and vice versa.

5 perpared by LieltiTse 11/5/2019

Computer Function

The basic function performed by a computer is execution of a

program

Which consists of a set of instructions stored in memory.

In its simplest form, instruction processing consists of two

steps:

1. The processor reads (fetches) instructions from memory

one at a time and

2. executes each instruction.

Program execution consists of repeating the process of

instruction fetch and instruction execution.

The processor required for a single instruction is called an

instruction cycle.

6 perpared by LieltiTse 11/5/2019

Computer Function

At the beginning of each instruction cycle, the processor

fetches an instruction from memory.

In a typical processor, a register called the program counter

(PC) holds the address of the instruction to be fetched next.

The processor always increments the PC after each instruction

fetch so that it will fetch the next instruction in sequence.

The fetched instruction is loaded into a register in the

processor known as the instruction register (IR).

The instruction contains bits that specify the action the

processor is to take.

The processor interprets the instruction and performs the

required action.

7 perpared by LieltiTse 11/5/2019

Computer Function

Virtually all computers provide mechanism by which other

modules (I/O, memory) may interrupt normal processing of

processor.

Interrupts are provided primarily as a way to improve processing

efficiency.

The most common classes of interrupts:

Program: Occurs as a result of an instruction execution, such as

arithmetic overflow, division by zero, etc.

Timer: Generated by a timer within the processor and allows the

operating system to perform certain functions on a regular basis.

I/O: Generated by an I/O controller, to signal normal completion of an

operation or to signal a variety of error conditions.

Hardware failure: Generated by a failure such as power failure or memory

parity error.

8 perpared by LieltiTse 11/5/2019

Computer Function

From the point of view of the user program, an interrupt is just

an interruption of the normal sequence of execution.

When the interrupt processing is completed, execution resumes.

To accommodate interrupts, an interrupt cycle is added to the

instruction cycle.

In the interrupt cycle, the processor checks to see if any

interrupts have occurred, indicated by the presence of an

interrupt signal.

If no interrupts are pending, the processor proceeds to the fetch

cycle and fetches the next instruction of the current program.

9 perpared by LieltiTse 11/5/2019

Computer Function

If an interrupt is pending, the processor does the following:

It suspends execution of the current program being executed

and saves its context on the system stack – a special place in

memory.

It sets the program counter to the starting address of an

interrupt handler routine.

10 perpared by LieltiTse 11/5/2019

Memory System

• No one technology is optimal in satisfying the memory

requirements for a computer system.

• As a consequence, the typical computer system is equipped with a

hierarchy of memory subsystems:

Some internal to the system (directly accessible by the

processor) and

Some external to the system (accessed by the processor via an

I/O module).

11 perpared by LieltiTse 11/5/2019

Memory System

What do we need?

A memory to store very large programs and to work at a speed

comparable to that of the CPU.

The reality is:

The larger a memory, the slower it will be;

The faster a memory, the greater the cost per bit.

A solution:

To build a composite memory system which combines a small

and fast memory with a large and slow memory, and behaves,

most of the time, like a large and fast memory.

This two-level principle can be extended to a hierarchy of

many levels.

12 perpared by LieltiTse 11/5/2019

Memory System

• Computer memory is organized into a hierarchy. At the highest

level (closest to the processor) are the processor registers.

• Next comes one or more levels of cache, When multiple levels

are used, they are denoted L1, L2, and so on.

• Next comes main memory, which is usually made out of

dynamic random-access memory (DRAM). All of these are

considered internal to the computer system.

• The hierarchy continues with external memory, with the next

level typically being a fixed hard disk, and one or more levels

below that consisting of removable media such as optical disks

and tape.

13 perpared by LieltiTse 11/5/2019

Memory System

There are trade-offs between three key characteristics of

memory: cost, capacity, and access time. The following

relationship holds:

Faster access time ---greater cost per bit

Greater capacity --- less cost per bit

Greater capacity ---slower access time

The dilemma facing the designer is clear. The designer

would like to use memory technologies that provide for

large-capacity memory, both because the capacity is needed

and because the cost per bit is low.

14 perpared by LieltiTse 11/5/2019

Memory hierarchy

The design constraints on a computer’s memory can be summed

up by three questions:

How much?

How fast?

How expensive?

As might be expected, there is a trade-off among the three key

characteristics of memory: namely,

Capacity

access time

cost.

15 perpared by LieltiTse 11/5/2019

Memory hierarchy…

A variety of technologies are used to implement memory

systems, and across this spectrum of technologies, the following

relationships hold:

Faster access time, greater cost per bit

Greater capacity, smaller cost per bit

Greater capacity, slower access time

As one goes down the hierarchy, the following occur:

Decreasing cost per bit

Increasing capacity

Increasing access time

Decreasing frequency of access of the memory by the

processor

16 perpared by LieltiTse 11/5/2019

Memory Hierarchy - Diagram

17 perpared by LieltiTse 11/5/2019

Hierarchy List

Registers

L1 Cache

L2 Cache

Main memory

Disk

Optical

Tape

18 perpared by LieltiTse 11/5/2019

Access methods

Sequential

Start at the beginning and read through in order

Access time depends on location of data and previous

location

e.g. tape

Direct

Individual blocks have unique address

Access is by jumping to vicinity plus sequential search

Access time depends on location and previous location

e.g. disk

19 perpared by LieltiTse 11/5/2019

Access method …

Random

Individual addresses identify locations exactly

Access time is independent of location or previous access

e.g. RAM

Associative

Data is located by a comparison with contents of a portion

of the store

Access time is independent of location or previous access

e.g. cache

20 perpared by LieltiTse 11/5/2019

Memory classification

Semi conductor Main memory

Nowadays, the use of semiconductor chips for main memory is

almost universal.

Organization

The basic element of a semiconductor memory is the

memory cell.

Although a variety of electronic technologies are used, all

semiconductor memory cells share certain properties:

Exhibit 2 stable (or semi-stable) states which can represent

binary 1 or 0.

Capable of being written into (at least once) to set states.

Capable of being read to sense states.

21 perpared by LieltiTse 11/5/2019

Cont…

Organization

Most commonly cell has three functional terminals capable of

carrying an electrical signal.

Select terminal: Selects a memory cell for a read or write

operation.

Control terminal: Indicates read or write.

Other terminal: For writing, it provides an electrical sign

al that sets state of cell to 1 or 0. For reading, it is used for

output of cell’s state.

22 perpared by LieltiTse 11/5/2019

Cont…

Main memory:

Memory is the workspace for the computer’s processor.

It holds the instructions that the processor executes and the data

that those instructions work with.

It is a temporary storage area where the programs and data being

operated on by the processor must reside.

Memory storage is considered temporary because the data and

programs remain there only as long as the computer has

electrical power or is not reset.

When we talk about a computer’s memory, we usually mean the

RAM or physical memory in the system, which is mainly the

memory chips or modules the processor uses to store primary

active programs and data.

23 perpared by LieltiTse 11/5/2019

Cont…

Physically, the main memory in a system is a collection of chips

or modules containing chips that are usually plugged into the

motherboard.

These chips or modules vary in their electrical and physical

designs and must be compatible with the system into which they

are being installed to function properly.

Three main memory plays a significant role in the following

important aspects of your computer system:

Performance

Software Support

Reliability and Stability

Upgradability

24 perpared by LieltiTse 11/5/2019

Cont…

1. RAM (random access memory)

Holds data and instructions used by CPU

Volatile (unlike ROM, the contents of RAM are lost when the power

is turned off).

RAM is also sometimes called read-write memory or RWM.

RAM is much faster than ROM.

RAM is stored in modules: DIMMs, RIMMs, SIMMs

There are many different types of RAMs:

static RAM (SRAM) and

dynamic RAM (DRAM)

Memory cache is made up of SRAM (it is faster)

25 perpared by LieltiTse 11/5/2019

Cont…

One distinguishing characteristic of RAM is that it is possible

both to read data from the memory and to write new data into the

memory easily and rapidly.

Both the reading and writing are accomplished through the

use of electrical signals.

The other distinguishing characteristic of RAM is that it is

volatile. A RAM must be provided with a constant power supply.

If the power is interrupted, then the data are lost.

Thus, RAM can be used only as temporary storage. The two

traditional forms of RAM used in computers are DRAM and

SRAM.

26 perpared by LieltiTse 11/5/2019

Static RAM

It holds its data without external refresh, for as long as power is

supplied to the circuit.

SRAM is much faster than DRAM and much more capable of

keeping pace with modern processors.

SRAM memory is available in access times of 2ns or less, so it can

keep pace with processors running 500MHz or faster.

SRAMs are much lower in density(SRAM chips are physically

larger and store fewer bits overall) and much more expensive than

DRAMs,

SRAM is up to 30 times larger physically and up to 30 times more

expensive than DRAM.

SRAM is manufactured in a way rather similar to how processors

are: highly-integrated transistor patterns photo-etched into silicon.

Each SRAM bit is comprised of between four and six transistors,

which is why SRAM takes up much more space compared to

DRAM, which uses only one (plus a capacitor).

27 perpared by LieltiTse 11/5/2019

Strength and Weakness of SRAM

Strengths:

Simplicity: SRAMs don't require external refresh circuitry or

other work in order for them to keep their data intact.

Speed: SRAM is faster than DRAM.

Weaknesses:

Cost: SRAM is several times more expensive than DRAM.

Size: SRAMs take up much more space than DRAMs.

Cache memory is a type of SRAM memory, which can run fast

enough to match the CPU,

Three types: L1,L2,L3(L1 is the fastest)

28 perpared by LieltiTse 11/5/2019

Dynamic RAM

Dynamic RAM is a type of RAM that only holds its data if it is

continuously accessed by special logic called a refresh circuit.

The memory cells in a DRAM chip are tiny capacitors that retain a

charge to indicate a bit.

DRAM must be constantly refreshed; otherwise, the electrical

charges in the individual memory capacitors will drain and the data

will be lost even if it continues to have power supplied to it.

Refresh occurs when the system memory controller takes a tiny

break and accesses all the rows of data in the memory chips.

Refreshing the memory takes processor time away from other tasks

because each refresh cycle takes several CPU cycles to complete.

DRAMs use only one transistor and capacitor pair per bit, which

makes them very dense, offering more memory capacity per chip

than other types of memory.

29 perpared by LieltiTse 11/5/2019

Cont…

The transistor for each DRAM bit cell reads the charge state of the

adjacent capacitor.

If the capacitor is charged, the cell is read to contain a 1; no charge

indicates a 0.

The charge in the tiny capacitors is constantly draining, which is

why the memory must be refreshed constantly.

The problem with capacitors is that they only hold a charge for a

short period of time, and then it fades away.

DRAMs are inexpensive, slow and the chips can be densely

packed, so a lot of memory capacity can fit in a small space.

Currently, DRAM chips are available with densities of up to 1Gb or

more. This means that DRAM chips are available with one billion

or more transistors!

30 perpared by LieltiTse 11/5/2019

SRAM vs. DRAM

Both static and dynamic RAMs are volatile; that is, power must be

continuously supplied to the memory to preserve the bit values.

A dynamic memory cell is simpler and smaller than a static memory

cell. Thus, a DRAM is more dense (smaller cells means more cells

per unit area) and less expensive than a corresponding SRAM.

On the other hand, a DRAM requires the supporting refresh

circuitry. For larger memories, the fixed cost of the refresh circuitry

is more than compensated for by the smaller variable cost of DRAM

cells. Thus, DRAMs tend to be favored for large memory requirements.

A final point is that SRAMs are generally somewhat faster than

DRAMs. Because of these relative characteristics, SRAM is used

for cache memory (both on and off chip), and DRAM is used for

main memory.

31 perpared by LieltiTse 11/5/2019

2. ROM (Read-Only- Memory

Is a type of memory that can permanently or semi-permanently

store data.

Non-volatile (retains data after PC is turned off)

The fact that ROM cannot easily be modified provides a

measure of security against accidental (or malicious) changes

to its contents.

ROM is an ideal place to put the PC’s startup instruction. i.e.

the software that boots the system.

The main ROM BIOS is contained in a ROM chip on the

motherboard, but there are also adapter cards with ROMs on

them as well.

ROMs on adapter cards contain auxiliary BIOS routines and

drivers needed by the particular card, especially for those cards

that must be active early in the boot process, such as video

cards.

32 perpared by LieltiTse 11/5/2019

ROM Types

A. ROM: is designed to perform a specific function and cannot be

changed.

This is inflexible and so regular ROMs are only used generally

for programs that are static (not changing often) and mass-

produced.

B. Programmable ROM (PROM): can be programmed using

special equipment; it can be written to, but only once.

The writing process is performed electrically and may be

performed by a supplier or customer at a time later than the

original chip fabrication.

Special equipment is required for the writing process.

PROMs provide flexibility and convenience.

33 perpared by LieltiTse 11/5/2019

Cont…

C. Electrically Erasable Programmable ROM (EEPROM): is

ROM that can be erased and reprogrammed under software

control.

This is the most flexible type of ROM, and is now commonly

used for holding BIOS programs.

When you hear reference to a flash BIOS or doing a BIOS

upgrade by "flashing", this refers to reprogramming the BIOS

EEPROM with a special software program.

Any location can be read from ROM in any order, so it is random

access as well.

Finally, one other characteristic of ROM, compared to RAM, is that

it is much slower, typically having double the access time of RAM

or more.

34 perpared by LieltiTse 11/5/2019

Cont…

D. Flash Memory

Gets its name because the microchip is organized so that a

section of memory cells are erased in a single action (flash).

First introduced in the mid-1980s.

Flash memory is intermediate between EPROM and

EEPROM in both cost and functionality.

Like EEPROM, flash memory uses an electrical erasing

technology. An entire flash memory can be erased in one or

a few seconds, which is much faster than EPROM.

In addition, it is possible to erase just blocks of memory

rather than an entire chip. However, flash memory does not

provide byte-level erasure.

35 perpared by LieltiTse 11/5/2019

Cont…

E. Erasable Programmable ROM (EPROM)

EPROM is read and written electrically, as with PROM.

However, before a write operation, all the storage cells must

be erased to the same initial state by exposure of the

packaged chip to ultraviolet radiation.

Ultraviolet light of a specific frequency can be shined through this

window for a specified period of time, which will erase the EPROM

and allow it to be reprogrammed again

This erasure process can be performed repeatedly; each

erasure can take as much as 20 minutes to perform.

Thus, the EPROM can be altered multiple times and holds

its data virtually indefinitely.

EPROM is more expensive than PROM.

36 perpared by LieltiTse 11/5/2019

Cache Memory

Cache: A small, very fast, memory used to store data and

instructions, that have recently been used or are likely to be used

soon.

When a byte of memory is retrieved by the Memory

Management Unit (MMU), a copy of that byte and a number of

other nearby bytes are placed in the cache.

Sits between normal main memory and CPU

37 perpared by LieltiTse 11/5/2019

Cache memory levels

Modern systems often contain several levels of cache:

L1 Cache:

On the CPU chip.

Smallest and fastest cache.

L2 Cache:

Larger and slower than L1 cache.

L3 Cache:

Larger and slower than L2 cache.

38 perpared by LieltiTse 11/5/2019

Element of Cache design

There are a few basic design elements that serve to classify and

differentiate cache architectures:

39 perpared by LieltiTse 11/5/2019

Cont…

40 perpared by LieltiTse 11/5/2019

Mapping

The transfer of data from main memory to cache memory is

referred as mapping process.

There are three types of cache mapping:

1. Direct Mapping: maps each block of main memory into only one

possible cache line.

2. Fully Associative Mapping: permits each main memory block to

be loaded into any line of the cache.

3. Set Associative Mapping: the cache is divided into a number of

sets of cache lines; each main memory block can be mapped into

ant line in a particular set.

41 perpared by LieltiTse 11/5/2019

Direct Mapping

Maps each block of main memory into only one possible

cache line.

Mapping is expressed as

i = j modulo m

where i = cache line number

j = main memory block number

m = number of lines in cache

42 perpared by LieltiTse 11/5/2019

Cont…

In direct mapping, 24 bit memory address contains:

2 bit word identifier

22 bit block identifier

8 bit tag

14 bit line no

43 perpared by LieltiTse 11/5/2019

Cont…

44 perpared by LieltiTse 11/5/2019

Fully associative mapping

Allows each memory block to be loaded into any line of cache. In

this case, the cache control logic interprets a memory address simply

as a tag and a word field.

Tag uniquely identifies a block of main memory. To determine

whether a block is in cache, cache control logic must simultaneously

examine every line’s tag for a match.

It requires fully associative memory. Implementation is

expensive and has very complex circuitry.

45 perpared by LieltiTse 11/5/2019

Cont…

In associative mapping, a 24 bit memory address consists of

2 bit word

22 bit tag

46 perpared by LieltiTse 11/5/2019

Set associative mapping

Compromise between direct and associative mappings to

reduce their disadvantages. Cache is divided into v sets,

each of which

consists k lines.

m = v × k

i = j modulo v

where i = cache set number

j = main memory block number

m = number of lines in cache

So a given block will map directly to a particular set, but

can occupy any line in that set (associative mapping is used

within set).

47 perpared by LieltiTse 11/5/2019

Cont…

In set associative mapping, a 24 bit memory address consists of:

9 bit tag

13 bit set (identifies a unique set of lines within cache)

2 bit word

48 perpared by LieltiTse 11/5/2019

Replacement algorithms

• When all lines are occupied bringing in a new block requires that

an existing line be overwritten.

• There are four most common algorithms:

1. Least-recently-used (LRU): The idea is to replace that block in

set which has been in cache longest with no reference to it.

2. First-in-first-out (FIFO): The idea is to replace that block in

set which has been in cache longest.

3. Least-frequently-used (LFU): The idea is to replace that block

in set which has experienced fewest references.

4. Random: The idea is to replace a random block in set.

49 perpared by LieltiTse 11/5/2019

Write Policy

The problem:

How to keep cache content and main memory content

consistent without losing too much performance?

The are mostly two techniques to overcome these problems:

Write through:

All write operations are passed to main memory:

If the addressed location is currently in the cache, the cache is

updated so that it is coherent with the main memory.

Write back:

Write operations update only the cache memory which is not

kept coherent with main memory. When the slot is replaced from

the cache, its content has to be copied back to memory.

50 perpared by LieltiTse 11/5/2019

Secondary memory

Figure. Hard disk construction and Operation

51 perpared by LieltiTse 11/5/2019

Secondary memory…

Disk storage:-

Disks are workhorse storage devices that hold enormous amounts

of data.

Disk Geometry:-

Disks are constructed from platters. Each platter consists of two

sides, or surfaces, that are coated with magnetic recording

material.

A rotating spindle in the center of the platter spins the platter at a

fixed rotational rate, typically between 5400 and 15,000

revolutions per minute (RPM).

52 perpared by LieltiTse 11/5/2019

Cont…

Each surface consists of a collection of concentric

rings called tracks.

Each track is partitioned into a collection of sectors.

Each sector contains an equal number of data bits (typically 512

bytes) encoded in the magnetic material on the sector.

Sectors are separated by gaps where no data bits are stored.

Gaps store formatting bits that identify sectors.

53 perpared by LieltiTse 11/5/2019

54 perpared by LieltiTse 11/5/2019

Cont…

Disk geometry

55 perpared by LieltiTse 11/5/2019

56 perpared by LieltiTse 11/5/2019

Cont…

Disk manufacturers describe the geometry of multiple-platter

drives in terms of cylinders, where a cylinder is the collection of

tracks on all the surfaces that are equidistant from the center of the

spindle.

For example, if a drive has three platters and six surfaces, and the

tracks on each surface are numbered consistently, then cylinder k

is the collection of the six instances of track k.

57 perpared by LieltiTse 11/5/2019

Disk Capacity

The maximum number of bits that can be recorded by a disk is

known as its maximum capacity, or simply capacity.

Disk capacity is determined by the following technology factors:

Recording density (bits/in): The number of bits that can be

squeezed into a 1-inch segment of a track.

Track density (tracks/in): The number of tracks that can be

squeezed into a 1-inch segment of the radius extending from the

center of the platter.

58 perpared by LieltiTse 11/5/2019

Cont…

Areal density (bits/in2): The product of the recording density and

the track density.

The capacity of a disk is given by the following formula:

59 perpared by LieltiTse 11/5/2019

Disk Operation

Disks read and write bits stored on the magnetic surface using a

read/write head connected to the end of an actuator arm.

By moving the arm back and forth along its radial axis, the drive

can position the head over any track on the surface. This

mechanical motion is known as a seek.

60 perpared by LieltiTse 11/5/2019

Cont…

61 perpared by LieltiTse 11/5/2019

Cont…

Platters

Multiple-platter disks employ a movable head, with one read-

write head per platter surface. All of the

heads are mechanically fixed so that all are at the same distance

from the center of the disk and move together.

Thus, at any time, all of the heads are positioned over tracks that

are of equal distance from the center of the disk.

Single-platter disks employ only a single platter.

62 perpared by LieltiTse 11/5/2019

Cont…

Disks read and write data in sector-sized blocks.

The access time for a sector has three main components:

seek time,

rotational latency

transfer time:

63 perpared by LieltiTse 11/5/2019

Input Output System

64 perpared by LieltiTse 11/5/2019

Introduction

The computer system’s I/O architecture is its interface to the

outside world.

This architecture provides a systematic means of controlling

interaction with the outside world and provides the operating

system with the information it needs to manage I/O activity

effectively.

The are three principal I/O techniques:

programmed I/O

interrupt-driven I/O

direct memory access (DMA)

65 perpared by LieltiTse 11/5/2019

Introduction…

programmed I/O, in which I/O occurs under the direct and

continuous control of the program requesting the I/O operation.

interrupt-driven I/O, in which a program issues an I/O

command and then continues to execute, until it is interrupted by

the I/O hardware to signal the end of the I/O operation.

direct memory access (DMA), in which a specialized I/O

processor takes over control of an I/O operation to move a large

block of data.

Two important examples of external I/O interfaces are:

FireWire

Infiniband.

66 perpared by LieltiTse 11/5/2019

Input output devices

There are a wide variety of peripherals with various methods of

operation.

It would be impractical to incorporate the necessary logic within

the processor to control a range of devices.

The data transfer rate of peripherals is often much slower than

that of the memory or processor.

Thus, it is impractical to use the high-speed system bus to

communicate directly with a peripheral.

67 perpared by LieltiTse 11/5/2019

Cont…

On the other hand, the data transfer rate of some peripherals is faster

than that of the memory or processor.

Again, the mismatch would lead to inefficiencies if not managed

properly.

Peripherals often use different data formats and word lengths than

the computer to which they are attached.

68 perpared by LieltiTse 11/5/2019

Purpose of I/O Modules

Interface to the processor and memory via the system bus or control

switch.

Interface to one or more peripheral devices.

69 perpared by LieltiTse 11/5/2019

External Devices

An external device connected to an I/O module is often referred to

as a peripheral device or, simply, a peripheral.

External device categories into three:

Human readable: communicate with the computer user –VDT,

printers etc.

Machine readable: communicate with equipment – disk drive or

tape drive

Communication: communicate with remote devices – may be

human readable or machine readable

70 perpared by LieltiTse 11/5/2019

The External Device – I/O Module

The interface to the I/O module is in the form of control, data,

and status signals.

Control signals determine the function that the device will

perform, such as send data to the I/O module (INPUT or

READ), accept data from the I/O module (OUTPUT or WRITE),

report status, or perform some control function particular to the

device (e.g., position a disk head).

Data are in the form of a set of bits to be sent to or received

from the I/O module.

Status signals indicate the state of the device. Examples are

READY/NOT-READY to show whether the device is ready for

data transfer.

71 perpared by LieltiTse 11/5/2019

Cont…

Control logic associated with the device controls the device’s

operation in response to direction from the I/O module.

The transducer converts data from electrical to other forms of

energy during output and from other forms to electrical during

input.

Typically, a buffer is associated with the transducer to temporarily

hold data being transferred between the I/O module and the

external environment.

72 perpared by LieltiTse 11/5/2019

Block Diagram of an External Device

73 perpared by LieltiTse 11/5/2019

I/O modules function

The major functions or requirements for an I/O module fall into

the following categories:

Control and timing: Coordinates flow of traffic between internal

resources and external devices.

Processor communication involves following:

Command decoding: I/O module accepts commands

from CPU typically sent as signals on control bus (e.g. READ

sector, WRITE sector, SEEK track number).

Data: Data are exchanged between CPU and I/O module over data

bus.

74 perpared by LieltiTse 11/5/2019

Cont…

Status reporting: Used to know status of I/O module. Common

status signals are BUSY and READY.

Address recognition: An I/O module must recognize

one unique address for each peripheral it controls.

Device communication: On the other side of I/O module,

communication involves commands, status information and data.

Data buffering: Rate of data transfer to or from CPU is

orders of magnitude faster than to or from external devices.

I/O module buffers data so that peripheral can send or

receive at its rate and CPU can send or receive at its rate.

Error detection: I/O module must detect and correct or

report error that occur to CPU.

One class of errors includes mechanical and electrical

malfunctions reported by device (e.g. paper jam).

Another class includes data errors during transmission.

75 perpared by LieltiTse 11/5/2019

Keyboard/Monitor

Most common means of computer/user interaction

Keyboard provides input that is transmitted to the computer

Monitor displays data provided by the computer

The character is the basic unit of exchange

Each character is associated with a 7 or 8 bit code

76 perpared by LieltiTse 11/5/2019

Disk Drive

Contains electronics for exchanging data, control, and status

signals with an I/O module

Contains electronics for controlling the disk read/write mechanism

Fixed-head disk – transducer converts between magnetic patterns

on the disk surface and bits in the buffer

Moving-head disk – must move the disk arm rapidly across the

surface

77 perpared by LieltiTse 11/5/2019

Interconnection Structures

The collection of paths connecting the various modules is called

the Interconnection structure.

• Supports the following types of transfers:

• Memory to CPU: Processor reads an instruction or a unit of

data from memory.

• CPU to memory: Processor writes a unit of data to memory.

• I/O to CPU: Processor reads data from an I/O device.

• CPU to I/O: Processor sends data to an I/O device.

• I/O to or from memory: An I/O module is allowed to

exchange directly with memory, without going through

processor, using Direct Memory Access (DMA).

• The most common types of interconnection structure is the BUS.

78 perpared by LieltiTse 11/5/2019

Bus Interconnection

A bus is a communication pathway connecting two or more

devices. A key characteristic of a bus is that it is a shared

transmission medium.

Typically, a bus consists of multiple communication pathways, or

lines. Each line is capable of transmitting signals representing

binary 1 and binary 0.

A bus that connects major computer components (processor,

memory, I/O) is called a system bus.

79 perpared by LieltiTse 11/5/2019

Bus Interconnection

Bus Structure

A system bus consists, typically, of from about 50 to hundreds of

separate lines. Each line is assigned a particular meaning or

function.

Generally the bus has three functional groups: Data, address, and

control lines(bus).

80 perpared by LieltiTse 11/5/2019

Bus Interconnection

Data lines: collectively are called the data bus.

Transfers data from different computer system components

the width of the data bus is a key factor in determining overall

system performance.

Address lines: are used to designate the source or destination of the

data on the data bus.

The width of the address bus determines the maximum possible

memory capacity of the system.

Control lines: are used to control the access to and the use of the

data and address lines.

Because the data and address lines are shared by all components,

there must be a means of controlling their use.

81 perpared by LieltiTse 11/5/2019

Bus Interconnection

Typical control lines includes:

Memory write: Causes data on the bus to be written into the

addressed location.

Memory read: Causes data from the addressed location to be

placed on the bus.

I/O write: Causes data on the bus to be output to the addressed

I/O port.

I/O read: Causes data from the addressed I/O port to be placed

on the bus.

Transfer ACK: Indicates that data have been accepted from or

placed on the bus.

Bus request: Indicates that a module needs to gain control of

the bus.

82 perpared by LieltiTse 11/5/2019

Bus interconnection

Bus grant: Indicates that a requesting module has been granted

control of the bus.

Interrupt request: Indicates that an interrupt is pending.

Interrupt ACK: Acknowledges that the pending interrupt has

been recognized.

Clock: Is used to synchronize operations.

Reset: Initializes all modules

83 perpared by LieltiTse 11/5/2019

Bus Interconnection

The operation of the bus:

If one module wishes to send data to another, it must do two

things:

obtain the use of the bus

transfer data via the bus

If one module wishes to request data from another module, it

must:

obtain the use of the bus

transfer a request to the other module over the appropriate

control and address lines

it must then wait for that second module to send the data

84 perpared by LieltiTse 11/5/2019

I/O Modules

Module Functions are:

Control and timing

Processor communication

Device communication

Data buffering

Error detection

85 perpared by LieltiTse 11/5/2019

I/O control steps

Processor checks I/O module for external device status

I/O module returns status

If device ready, processor gives I/O module command to request

data transfer

I/O module gets a unit of data from device

Data transferred from the I/O module to the processor

86 perpared by LieltiTse 11/5/2019

Processor communication

Command decoding: I/O module accepts commands from the

processor sent as signals on the control bus. Examples: READ

SECTOR, WRITE SECTOR, SEEK track number, and SCAN

record ID.

Data: data exchanged between the processor and I/O module over

the data bus

Status reporting: common status signals BUSY and READY are

used because peripherals are slow

Address recognition: I/O module must recognize a unique

address for each peripheral that it controls

87 perpared by LieltiTse 11/5/2019

I/O module communication

Device communication: commands, status information, and data

Data buffering: data comes from main memory in rapid burst and

must be buffered by the I/O module and then sent to the device at

the device’s rate

Error detection: responsible for reporting errors to the processor.

They may include:

Malfunctions by device (paper jam)

Data errors (parity checking at the device level)

Internal errors to the I/O module such as buffer overruns

88 perpared by LieltiTse 11/5/2019

Typical I/O Device Data Rates

89 perpared by LieltiTse 11/5/2019

I/O Module Structure

Block Diagram of an I/O Module

90 perpared by LieltiTse 11/5/2019

Cont…

I/O module functions allow the processor to view devices is a

simple-minded way

I/O module may hide device details from the processor so the

processor only functions in terms of simple read and write

operations – timing, formats, etc…

I/O module may leave much of the work of controlling a device

visible to the processor – rewind a tape, etc…

91 perpared by LieltiTse 11/5/2019

I/O Techniques

Programmed

Interrupt driven

Direct Memory Access (DMA)

92 perpared by LieltiTse 11/5/2019

Programmed I/O

Processor executes an I/O instruction by issuing command to

appropriate I/O module

I/O module performs the requested action and then sets the

appropriate bits in the I/O status register – I/O module takes not

further action to alert the processor – it does not interrupt the

processor

The processor periodically checks the status of the I/O module

until it determines that the operation is complete

93 perpared by LieltiTse 11/5/2019

I/O Commands

The processor issues an address, specifying I/O module and

device, and an I/O command. The commands are:

Control: activate a peripheral and tell it what to do

Test: test various status conditions associated with an I/O module

and its peripherals

Read: causes the I/O module to obtain an item of data from the

peripheral and place it into an internal register

Write: causes the I/O module to take a unit of data from the data

bus and transmit it to the peripheral

94 perpared by LieltiTse 11/5/2019

Three Techniques for Input of a Block of Data

95 perpared by LieltiTse 11/5/2019

Interrupt-Driven I/O

Overcomes the processor having to wait long periods of time for

I/O modules

The processor does not have to repeatedly check the I/O module

status

To avoid the processor being not performing an useful

computation, a hardware signal called an interrupt to the processor

can do it.

At least one of the bus control lines, called an interrupt-request

line, is usually dedicated for this purpose

An interrupt-service routine usually is needed and is executed

when an interrupt request is issued

On the other hand, the processor must inform the device that its

request has been recognized so that it may remove its interrupt-

request signal.

An interrupt-acknowledge signal serves this function

96 perpared by LieltiTse 11/5/2019

Simple Interrupt Processing

97 perpared by LieltiTse 11/5/2019

I/O module view point

I/O module receives a READ command form the processor

I/O module reads data from desired peripheral into data register

I/O module interrupts the processor

I/O module waits until data is requested by the processor

I/O module places data on the data bus when requested

98 perpared by LieltiTse 11/5/2019

Processor view point

The processor issues a READ command

The processor performs some other useful work

The processor checks for interrupts at the end of the instruction

cycle

The processor saves the current context when interrupted by the

I/O module

The processor read the data from the I/O module and stores it in

memory

The processor the restores the saved context and resumes execution

99 perpared by LieltiTse 11/5/2019

Design Issues

How does the processor determine which device issued the

interrupt

How are multiple interrupts dealt with

Device identification

Multiple interrupt lines – each line may have multiple I/O

modules

Software poll – poll each I/O module

Separate command line – TESTI/O

Processor read status register of I/O module

Time consuming

100 perpared by LieltiTse 11/5/2019

Cont…

Daisy chain

Hardware poll

Common interrupt request line

Processor sends interrupt acknowledge

Requesting I/O module places a word of data on the data lines

– “vector” that uniquely identifies the I/O module – vectored

interrupt

101 perpared by LieltiTse 11/5/2019

Cont…

Bus arbitration

I/O module first gains control of the bus

I/O module sends interrupt request

The processor acknowledges the interrupt request

I/O module places its vector of the data lines

102 perpared by LieltiTse 11/5/2019

Cont…

Multiple interrupts

The techniques above not only identify the requesting I/O module

but provide methods of assigning priorities

Multiple lines – processor picks line with highest priority

Software polling – polling order determines priority

Daisy chain – daisy chain order of the modules determines priority

Bus arbitration – arbitration scheme determines priority

103 perpared by LieltiTse 11/5/2019

Direct Memory Access

To transfer large blocks of data at high speed, a special control

unit may be provided between an external device and the main

memory, without continuous intervention by the processor.

This approach is called direct memory access (DMA)

DMA transfers are performed by a control circuit that is part of the

I/O device interface.

We refer to this circuit as a DMA controller.

104 perpared by LieltiTse 11/5/2019

Direct Memory Access…

Drawback of Programmed and Interrupt-Driven I/O

I/O transfer rate limited to speed that processor can test and

service devices

Processor tied up managing I/O transfers

DMA Controller Function

.DMA controller requests data bus control from CPU.

CPU grants the data bus control to the DMA controller

DMA controller reads device and writes to memory

DMA controller generates an interrupt request

105 perpared by LieltiTse 11/5/2019

Typical DMA Block Diagram

106 perpared by LieltiTse 11/5/2019

I/O Interfaces

The External Interface: FireWire and Infiniband

Key to the operation of an I/O module is an internal buffer that

can store data being passed between the peripheral and the rest of

the system.

With a new generation of high-speed serial interfaces, parallel

interfaces are becoming much less common.

107 perpared by LieltiTse 11/5/2019

I/O Interface

One major characteristic of the interface is whether it is

serial or parallel.

In a parallel interface, there are multiple lines connecting

the I/O module and the peripheral, and multiple bits are

transferred simultaneously.

In a serial interface, there is only one line used to transmit

data, and bits must be transmitted one at a time.

108 perpared by LieltiTse 11/5/2019

Cont…

The connection between an I/O module in a computer system

and external devices can be:

A point-to-point interface provides a dedicated line

between the I/O module and the external device. On small

systems (PCs, workstations), typical point-to-point links

include those to the keyboard, printer and external modem.

Of increasing importance are multipoint external interfaces,

used to support external mass storage devices (disk and

tape drives) and multimedia devices (CD-ROMs, video,

audio). These multipoint interfaces are in effect external buses.

109 perpared by LieltiTse 11/5/2019

Standard I/O Interfaces

The processor bus is the bus defined by the signals on the

processor chip itself.

Devices that require a very high speed connection to the

processor, such as the main memory, may be connected directly

to this bus

The motherboard usually provides another bus that can support

more devices.

The two buses are interconnected by a circuit, which we called a

bridge, that translates the signals and protocols of one bus into

those of the other

The expansion bus is not subject to these limitations, and

therefore it can use a standardized signaling structure

110 perpared by LieltiTse 11/5/2019

Universal Serial Bus (USB)

The USB has been designed to meet several key objectives

Provide a simple, low-cost, and easy to use interconnection system

that overcomes the difficulties due to the limited number of I/O

ports available on a computer

Accommodate a wide range of data transfer characteristics for I/O

devices, including telephone and Internet connections

Enhance user convenience through a “plug-and-play” mode of

operation

111 perpared by LieltiTse 11/5/2019

FireWire Serial Bus – IEEE 1394

FireWire is a high-speed, low cost and easy to implement

serial bus.

In fact, FireWire is finding favor not only for computer

systems, but also in consumer electronics products, such as

digital cameras, DVD players/recorders, and televisions.

In these products, FireWire is used to transport video images,

which are increasingly coming from digitized sources.

Very high speed serial bus

Low cost

Easy to implement

Used with digital cameras, televisions etc.

112 perpared by LieltiTse 11/5/2019

Infiniband

Recent I/O specification aimed at high-end server market

First version released early 2001

Standard for data flow between processors and intelligent I/O

devices

Intended to replace PCI bus in servers

Greater capacity, increased expandability, enhanced flexibility

Connect servers, remote storage, network devices to central fabric

of switches and links

113 perpared by LieltiTse 11/5/2019

Cont…

Figure illustrates the InfiniBand architecture:

114 perpared by LieltiTse 11/5/2019

S-ar putea să vă placă și

- Operating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesDe la EverandOperating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesÎncă nu există evaluări

- Chapter 2Document114 paginiChapter 2millionÎncă nu există evaluări

- Chapter 2 Embedded MicrocontrollersDocument5 paginiChapter 2 Embedded MicrocontrollersyishakÎncă nu există evaluări

- CS8493 Operating Systems Question BankDocument160 paginiCS8493 Operating Systems Question BankMelvinÎncă nu există evaluări

- Development of Computer Organizatio1Document8 paginiDevelopment of Computer Organizatio1Salsabila IrbahÎncă nu există evaluări

- Computer SciencesDocument29 paginiComputer SciencesX x A7md x XÎncă nu există evaluări

- 2.1 Computer-System OperationDocument20 pagini2.1 Computer-System OperationHasib PeyalÎncă nu există evaluări

- TSN2101/TOS2111 - Tutorial 1 (Introduction To Operating Systems)Document5 paginiTSN2101/TOS2111 - Tutorial 1 (Introduction To Operating Systems)MoonÎncă nu există evaluări

- Os FaqDocument14 paginiOs Faqd_dharaÎncă nu există evaluări

- csc708 - Computer ArchitectureDocument7 paginicsc708 - Computer ArchitectureMichael T. BelloÎncă nu există evaluări

- Unit 2 Computer Systems: StructureDocument13 paginiUnit 2 Computer Systems: StructureCamilo AmarcyÎncă nu există evaluări

- Chapter 1 EditDocument463 paginiChapter 1 Edittthanhhoa17112003Încă nu există evaluări

- Chapter 1 Edit PDFDocument40 paginiChapter 1 Edit PDFDragon.D. ArthurÎncă nu există evaluări

- Operating Systems Chapter (1) Review Questions: Memory or Primary MemoryDocument8 paginiOperating Systems Chapter (1) Review Questions: Memory or Primary MemoryNataly AdelÎncă nu există evaluări

- Lecture # 01-03: Basic Parts of Computer, What Is Microprocessor & Difference Between Microprocessor & MicrocontrollerDocument26 paginiLecture # 01-03: Basic Parts of Computer, What Is Microprocessor & Difference Between Microprocessor & MicrocontrollerHammad MughalÎncă nu există evaluări

- CHAPTER FIVcoaEDocument18 paginiCHAPTER FIVcoaEMohammedÎncă nu există evaluări

- What Is An Operating System?: Unit - 1Document18 paginiWhat Is An Operating System?: Unit - 1Arthi AnnamallaÎncă nu există evaluări

- OS - Unit 1 - NotesDocument15 paginiOS - Unit 1 - Notestanay282004guptaÎncă nu există evaluări

- Week 2 Internal Components of A Computer Fundamental Characteristics of A ProcessorDocument4 paginiWeek 2 Internal Components of A Computer Fundamental Characteristics of A ProcessorSunil NagumallaÎncă nu există evaluări

- Chapter 1: Computer System OverviewDocument5 paginiChapter 1: Computer System OverviewDeenesh KumarÎncă nu există evaluări

- Unit 3Document33 paginiUnit 3Avantee SinghÎncă nu există evaluări

- Pages From Operating - System - Concepts-1Document37 paginiPages From Operating - System - Concepts-1Desire MdlovuÎncă nu există evaluări

- Group 6Document7 paginiGroup 6Lê Chí CườngÎncă nu există evaluări

- Different Levels of The Memory HierarchyDocument200 paginiDifferent Levels of The Memory Hierarchymoonstar_dmeÎncă nu există evaluări

- Design and Implementation of An EPROM ProgrammerDocument124 paginiDesign and Implementation of An EPROM ProgrammerChidozie Ijeomah100% (1)

- Operating SystemsDocument42 paginiOperating SystemsKishore KumarÎncă nu există evaluări

- 11th Opearting System July 2022Document7 pagini11th Opearting System July 2022baljitÎncă nu există evaluări

- MMGMNT PDFDocument55 paginiMMGMNT PDFalihamzaÎncă nu există evaluări

- Computer System: Operating Systems: Internals and Design PrinciplesDocument56 paginiComputer System: Operating Systems: Internals and Design PrinciplesHurrain QueenÎncă nu există evaluări

- Operating Systems: Balqees TalalDocument23 paginiOperating Systems: Balqees TalalamjdÎncă nu există evaluări

- Chapter 4,5&6Document30 paginiChapter 4,5&6desÎncă nu există evaluări

- Unit 1: MotherboardDocument17 paginiUnit 1: MotherboardAkash SahaÎncă nu există evaluări

- WS1.2-OS IntroDocument2 paginiWS1.2-OS Introhaingoc0217Încă nu există evaluări

- CH 1Document52 paginiCH 1Mustafa Hamdy MahmoudÎncă nu există evaluări

- 1.1 Eight Ideas:: Unit 1 Overview & Instructions SyllabusDocument22 pagini1.1 Eight Ideas:: Unit 1 Overview & Instructions SyllabuskalaivaniÎncă nu există evaluări

- OS Module 1Document51 paginiOS Module 1webprogram32Încă nu există evaluări

- Os Unit-1 GanaDocument25 paginiOs Unit-1 GanaRamÎncă nu există evaluări

- What Are A Process and Process Table?Document10 paginiWhat Are A Process and Process Table?JackÎncă nu există evaluări

- Operating SystemDocument15 paginiOperating SystemBonventure KipkiruiÎncă nu există evaluări

- BSIT 1st Semester Paper 2Document5 paginiBSIT 1st Semester Paper 2Asif SyedÎncă nu există evaluări

- Fundamentals of ProgrammingDocument25 paginiFundamentals of ProgrammingperiyarphdÎncă nu există evaluări

- Computer Organization and Architecture Module 1 (Kerala University) NotesDocument30 paginiComputer Organization and Architecture Module 1 (Kerala University) NotesAssini Hussain100% (11)

- Computer Organization and Architecture Module 1Document46 paginiComputer Organization and Architecture Module 1Assini Hussain100% (1)

- 1.intro MA PDFDocument59 pagini1.intro MA PDFPoosarla TejaÎncă nu există evaluări

- CS8493 2marks PDFDocument36 paginiCS8493 2marks PDFSparkerz S Vijay100% (1)

- Engine 2018Document45 paginiEngine 2018AloyceÎncă nu există evaluări

- 2 Basic Computer ArchitectureDocument21 pagini2 Basic Computer Architecturemasyuki2002Încă nu există evaluări

- Computer Data StorageDocument12 paginiComputer Data StorageChristina MagnetaÎncă nu există evaluări

- Operating System Concepts - 8 EditionDocument30 paginiOperating System Concepts - 8 EditionManohar DattÎncă nu există evaluări

- ExercisesDocument33 paginiExercisesJeype Malbas VillarubiaÎncă nu există evaluări

- Icf 7 - Q1-W5-6 LasDocument14 paginiIcf 7 - Q1-W5-6 LasCathy De Andres GaspanÎncă nu există evaluări

- Os Module1Document37 paginiOs Module1lingaraj_superstarÎncă nu există evaluări

- OS Notes Ch1 For StudentDocument6 paginiOS Notes Ch1 For Studentseema negiÎncă nu există evaluări

- Chapter 1comDocument38 paginiChapter 1comaregawi weleabezgiÎncă nu există evaluări

- Exercise 1Document2 paginiExercise 1Lam Tien Hung (K17 HCM)Încă nu există evaluări

- Os (Unit 1)Document40 paginiOs (Unit 1)gopalhelpyouÎncă nu există evaluări

- Basic Structure of Computer ArchitectureDocument53 paginiBasic Structure of Computer Architecturenikhilmalagi0% (1)

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12De la EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12Încă nu există evaluări

- Endalcachew PDFDocument10 paginiEndalcachew PDFaregawi weleabezgiÎncă nu există evaluări

- C++ Worksheet $ AssignmentDocument14 paginiC++ Worksheet $ Assignmentaregawi weleabezgiÎncă nu există evaluări

- Endalcachew PDFDocument10 paginiEndalcachew PDFaregawi weleabezgi100% (1)

- 1-0-1 Computer Basics Student Manual PDFDocument21 pagini1-0-1 Computer Basics Student Manual PDFMay ann argenioÎncă nu există evaluări

- Chapter - 1 Earth MaterialsDocument55 paginiChapter - 1 Earth Materialsaregawi weleabezgiÎncă nu există evaluări

- Chapter Two - Lecture - 02Document47 paginiChapter Two - Lecture - 02aregawi weleabezgiÎncă nu există evaluări

- Temperatue and DiplacementDocument63 paginiTemperatue and Diplacementaregawi weleabezgi100% (1)

- Chapter 5Document16 paginiChapter 5aregawi weleabezgiÎncă nu există evaluări

- ppt3 Measurt PDFDocument74 paginippt3 Measurt PDFaregawi weleabezgiÎncă nu există evaluări

- Chapter TwoDocument44 paginiChapter Twoaregawi weleabezgiÎncă nu există evaluări

- Chapter 3Document10 paginiChapter 3aregawi weleabezgiÎncă nu există evaluări

- Chapter 5Document13 paginiChapter 5aregawi weleabezgiÎncă nu există evaluări

- Transmission Line ParameterDocument75 paginiTransmission Line Parameteraregawi weleabezgi100% (1)

- Chapter 6Document13 paginiChapter 6aregawi weleabezgiÎncă nu există evaluări

- Chapter 4Document20 paginiChapter 4aregawi weleabezgiÎncă nu există evaluări

- SIMATIC S7-300: The Universal Controller For System Solutions With Factory Automation As Focal PointDocument81 paginiSIMATIC S7-300: The Universal Controller For System Solutions With Factory Automation As Focal PointDeath ZoneÎncă nu există evaluări

- Home Automation Using Chatbot and Voice AssistantDocument5 paginiHome Automation Using Chatbot and Voice AssistantJOEL STEPHEN 19BEE0262Încă nu există evaluări

- Introduction To 68HC11 MICROCONTROLLERDocument72 paginiIntroduction To 68HC11 MICROCONTROLLERNarasimha Murthy Yayavaram100% (3)

- Me6703 Cim PDFDocument34 paginiMe6703 Cim PDFHimanshu MishraÎncă nu există evaluări

- Ku Cse SyllabusDocument75 paginiKu Cse SyllabusAshrith KaparaboinaÎncă nu există evaluări

- ICTICT501 - Research and Review Hardware Technology Options For OrganisationsDocument48 paginiICTICT501 - Research and Review Hardware Technology Options For OrganisationsMike TombocÎncă nu există evaluări

- DEFINITIONS Under Cyber LawDocument2 paginiDEFINITIONS Under Cyber Lawpranjal yadavÎncă nu există evaluări

- Staad Pro Tutorial Part3Document50 paginiStaad Pro Tutorial Part3mech_nedian9714Încă nu există evaluări

- 5 ModbusDocument39 pagini5 ModbusMahar Tri WahyudinÎncă nu există evaluări

- VPEG Sequence Control ST16Document50 paginiVPEG Sequence Control ST16Nik Sayko100% (2)

- DFC10093 Chapter 3Document108 paginiDFC10093 Chapter 3Navinaash Chanthra SegaranÎncă nu există evaluări

- Introduction To Computing: Input and OutputDocument54 paginiIntroduction To Computing: Input and OutputChristianLouisNoquisÎncă nu există evaluări

- RE - 5 - Three-Phase Non-Directional Overcurrent Protection Low-Set Stage (NOC3Low) High-Set Stage (NOC3High) Instantaneous Stage (NOC3Inst)Document25 paginiRE - 5 - Three-Phase Non-Directional Overcurrent Protection Low-Set Stage (NOC3Low) High-Set Stage (NOC3High) Instantaneous Stage (NOC3Inst)rajesh100% (1)

- Computer PDF Book PDFDocument145 paginiComputer PDF Book PDFGovind Vishwakarma100% (1)

- Eage2012 Open Source Workshop Seaseis PosterDocument2 paginiEage2012 Open Source Workshop Seaseis PosterAjay PundirÎncă nu există evaluări

- DCC 080 EngDocument22 paginiDCC 080 EngApeco WorkshopÎncă nu există evaluări

- S7-300 Module Data - Analog IO Module SM 334Document7 paginiS7-300 Module Data - Analog IO Module SM 334dragon_tudvnÎncă nu există evaluări

- Java Mini-ReportDocument29 paginiJava Mini-Report4AL20IS037PRASAD ACHARIÎncă nu există evaluări

- w342 E1 15+Cs CJ CP Nsj+ComrefmanualDocument268 paginiw342 E1 15+Cs CJ CP Nsj+ComrefmanualÁgó AttilaÎncă nu există evaluări

- Project PPT Varun KR PandeyDocument18 paginiProject PPT Varun KR Pandeyvarun pandey 1065Încă nu există evaluări

- Honeywell En0b0564 Ge51r0711Document18 paginiHoneywell En0b0564 Ge51r0711jmarimonÎncă nu există evaluări

- Two Pass MacroprocessorDocument10 paginiTwo Pass MacroprocessorKrishna Prasad67% (9)

- Kenwood KDC MPV 5025 Service ManualDocument34 paginiKenwood KDC MPV 5025 Service ManualDejan PušacÎncă nu există evaluări

- C语言的科学与艺术 (英文版)Document596 paginiC语言的科学与艺术 (英文版)周帅Încă nu există evaluări

- Electrical and Electronics Engineering Vii Semester: Course Theory/Lab L T P C CodeDocument66 paginiElectrical and Electronics Engineering Vii Semester: Course Theory/Lab L T P C Codejitendra jhaÎncă nu există evaluări

- Wsi PSDDocument18 paginiWsi PSDДрагиша Небитни ТрифуновићÎncă nu există evaluări

- Bluetooth Based Home AutomationDocument15 paginiBluetooth Based Home AutomationSiddharth DevÎncă nu există evaluări

- Computer Studies NotesDocument30 paginiComputer Studies Notessyed_talha_373% (11)

- GEMSTUDIO Users GuideDocument312 paginiGEMSTUDIO Users GuideFercho Martinez GarciaÎncă nu există evaluări

- Computers in GeneralDocument75 paginiComputers in GenerallvsaruÎncă nu există evaluări