Documente Academic

Documente Profesional

Documente Cultură

Memory Hierarchy Technology: I I I I

Încărcat de

manu12041990Descriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Memory Hierarchy Technology: I I I I

Încărcat de

manu12041990Drepturi de autor:

Formate disponibile

Memory Hierarchy Technology

Storage devices such as registers, caches, main memory, disk devices, and tape units are often organised as a hierarchy. The memory technology and storage organisation at each level are characterised by four parameters:

access time (ti) memory size (si) cost per byte (ci) transfer bandwidth (bi)

Memory Hierarchy Technology

The access time ti refers to the round-trip time from the CPU to the ith-level memory. The memory size si is the number of bytes or words in level i. The cost of the memory is estimated by the product c is i. The bandwidth bi refers to the rate at which information is transferred between adjacent levels.

Peripheral Technology

Besides disk drives and tape units, peripheral devices include printers, plotters, terminals, monitors, graphics displays, optical scanners, image digitizers, output microfilm devices, etc. Some I/O devices are tied to specialpurpose or multimedia applications.

Memory and I/O Subsystems

Memory Classification

Classification of memories according to several attributes:

Accessing method:

RAM (Random Access Memory) SAM (Sequential Access Memory) DASD (Direct Access Storage Devices)

Access time

Primary memory (RAMs) Secondary memory (DASDs & optimal SAMs)

Optimization of Memory Hierarchy

The goal in designing an n-level memory hierarchy is to achieve a:

Performance close to that of the fastest memory

Cost per bit close to that of the cheapest memory

Program behaviour with respect to memory References

Performance depends on:

Access time & memory size of each level

Management policies Design of processor-memory interconnected network

Inclusion, Coherence, and Locality

Information stored in a memory hierarchy (M1, M2, ... , Mn) satisfies three important properties: inclusion, coherence, and locality. We consider cache memory the innermost level M1, which directly communicates with the CPU registers. The outermost level Mn contains all the information words stored.

Inclusion Property

The inclusion property is stated as

M 1 M 2 ... M n

The set inclusion relationship implies that all information items are originally stored in the outermost level Mn. During the processing, subsets of Mn are copied into Mn-1. Similarly, subsets of Mn-1, are copied into Mn-2, and so on.

Coherence Property

The coherence property requires that copies of the same information item at successive memory levels be consistent. If a word is modified in the cache, copies of that word must be updated immediately or eventually at all higher levels. The hierarchy should be maintained as such. The first method is called write-through (WT), which demands immediate update in Mi+l if a word is modified in for i = 1, 2, ... , n 1. The second method is write-back (WB), which delays the update in Mi+1 until the word being modified in Mi is replaced or removed from Mi.

Locality of References

The memory hierarchy was developed based on a program behaviour known as locality of references. Memory references are generated by the CPU for either instruction or data access. There are three dimensions of the locality property:

Temporal locality Spatial locality Sequential locality

Memory Capacity Planning

The performance of a memory hierarchy is determined by the effective access time Teff to any level in the hierarchy. It depends on the hit ratios and access frequencies at successive levels.

Hierarchy Optimization

The total cost of a memory hierarchy is estimated as follows:

Ctotal ci si

i 0

Virtual Memory System

In many applications, large programs cannot fit in main memory for execution.

The natural solution is to introduce management schemes that intelligently allocate portions of memory to users as necessary for the efficient running of their programs.

Virtual Memory Models

The idea is to expand the use of the physical memory among many programs with the help of an auxiliary (backup) memory such as disk arrays.

Only active programs or portions of them become residents of the physical memory at one time. The vast majority of programs or inactive programs are stored on disk.

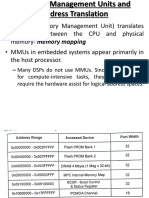

Address Spaces

Each word in the physical memory is identified by a unique physical address. All memory words in the main memory form a physical address space. Virtual addresses are generated by the processor during compile time. The virtual addresses must be translated into physical addresses at run time. A system of translation tables and mapping functions are used in this process.

Memory Management

The various memory management techniques include:

Fixed-partition

Dynamic Virtual -> segmentation & paging

Memory management is concerned with the following functions:

Keeping track of the status of each location Determining the allocation policy for memory Allocation : status info must be updated

Deallocation: release of previously allocated memory

Program relocation

During the execution of a program, the processor generates logical addresses which are mapped into the physical address space in main memory.

The address mapping is performed:

when the program is initially loaded (static relocation) During the execution of the program (dynamic relocation)

Disadvantages of static relocation

Makes it difficult for processors to share info which is modifiable during execution

If a program is displaced from main memory by mapping, it must be reloaded into the same set of memory locations -> binding the physical address space of the program for the duration of the execution -> inefficient

Address map implementation

Direct mapping: not efficient -> slow

Associative mapping: uses associative memory (AM) that maintains the mapping between recently used virtual and physical memory addresses.

Memory Replacement Policies

Memory management policies include the allocation and deallocation of memory pages to active processes and the replacement of memory pages.

Page replacement refers to the process in which a resident page in main memory is replaced by a new page transferred from the disk.

Page Replacement Policies

The following page replacement policies are specified in a demand paging memory system for a page fault at time t.

Least recently used (LRU)

Optimal (OPT) algorithm First-in-first-out (FIFO) Least frequently used (LFU) Circular FIFO

Random replacement

Examples of memory management allocation policies

Least Recently Used (LRU)- replaces the page with the largest backward distance <popular>

Belady's Optimal Algorithm (MIN)- replaces the page with the largest forward distance First-In, First-Out (FIFO)- replaces the page that has been in memory for the longest time.

Last-In, First-Out (LIFO)- replaces the page that has been in memory for the shortest time.

Random (RAND)- chooses a page at random for replacement

S-ar putea să vă placă și

- Ilovepdf MergedDocument86 paginiIlovepdf MergedWalter WhiteÎncă nu există evaluări

- OS Module3.2 MemoryDocument65 paginiOS Module3.2 MemoryDavidÎncă nu există evaluări

- Memory Management: Presented By:-Mr. P C Kaufa ND Computer Architecture and ServicingDocument38 paginiMemory Management: Presented By:-Mr. P C Kaufa ND Computer Architecture and ServicingGloria MatopeÎncă nu există evaluări

- Untitled DocumentDocument24 paginiUntitled Documentdihosid99Încă nu există evaluări

- OS NotesDocument79 paginiOS NotesSawn HotÎncă nu există evaluări

- OS Chapter 5Document112 paginiOS Chapter 5200339616138Încă nu există evaluări

- Main Memory ManagementDocument7 paginiMain Memory ManagementpoojajadhavÎncă nu există evaluări

- Operating System - Memory Management: Process Address SpaceDocument21 paginiOperating System - Memory Management: Process Address SpaceMamathaÎncă nu există evaluări

- Unit-2 OS Ch-1 CompleteDocument18 paginiUnit-2 OS Ch-1 CompleteVaibhavÎncă nu există evaluări

- Unit 4 - Operating System - WWW - Rgpvnotes.inDocument17 paginiUnit 4 - Operating System - WWW - Rgpvnotes.inVEDANSH PARGAIEN CO20366Încă nu există evaluări

- Operating System - Memory Management: Process Address SpaceDocument10 paginiOperating System - Memory Management: Process Address SpaceNelson RajaÎncă nu există evaluări

- Unit 4-PagingDocument20 paginiUnit 4-PagingBarani KumarÎncă nu există evaluări

- Memory Management in OSDocument76 paginiMemory Management in OSratanÎncă nu există evaluări

- Module4 OSDocument49 paginiModule4 OSabinrj123Încă nu există evaluări

- Unit 4-Memory MaangementDocument15 paginiUnit 4-Memory MaangementHabtieÎncă nu există evaluări

- Chapter 2 Part 1Document31 paginiChapter 2 Part 1jeffÎncă nu există evaluări

- Process Address Space: Memory ManagementDocument17 paginiProcess Address Space: Memory ManagementMohit SainiÎncă nu există evaluări

- Memory-Management StrategiesDocument70 paginiMemory-Management StrategiesNico Jhon R AlmarinezÎncă nu există evaluări

- Os (Unit 1)Document40 paginiOs (Unit 1)gopalhelpyouÎncă nu există evaluări

- M2: Memory Management: Binding of Instructions and Data To MemoryDocument3 paginiM2: Memory Management: Binding of Instructions and Data To Memory왕JΔIRΩÎncă nu există evaluări

- Need For Memory Hierarchy: (Unit-1,3) (M.M. Chapter 12)Document23 paginiNeed For Memory Hierarchy: (Unit-1,3) (M.M. Chapter 12)Alvin Soriano AdduculÎncă nu există evaluări

- Process Address Space: Symbolic AddressesDocument10 paginiProcess Address Space: Symbolic AddressesManmeetÎncă nu există evaluări

- CSA - Chapter 1Document39 paginiCSA - Chapter 1Nikita vermaÎncă nu există evaluări

- Memory ManagementDocument127 paginiMemory ManagementGlrmnÎncă nu există evaluări

- Module3 22Document29 paginiModule3 22Sourav SamantarayÎncă nu există evaluări

- Com Roan in & Ar It ReDocument35 paginiCom Roan in & Ar It ReWaseem Muhammad KhanÎncă nu există evaluări

- AcaDocument71 paginiAcaRishabh PurwarÎncă nu există evaluări

- Lecture 3 - Memory ManagementDocument33 paginiLecture 3 - Memory Managementadi50% (2)

- Mod 1Document78 paginiMod 1Pratheeksha GowdaÎncă nu există evaluări

- Chapter Three Memory Management (Main Memory)Document33 paginiChapter Three Memory Management (Main Memory)Riyad TamamÎncă nu există evaluări

- Memory HierarchyDocument16 paginiMemory HierarchyAnime LegacyÎncă nu există evaluări

- UNIT IV - Compatibility ModeDocument77 paginiUNIT IV - Compatibility ModeRudraksh sahÎncă nu există evaluări

- Unit 7 - Parallel Processing ParadigmDocument26 paginiUnit 7 - Parallel Processing ParadigmMUHMMAD ZAID KURESHIÎncă nu există evaluări

- Os Memory ManagementDocument6 paginiOs Memory ManagementMd Omar FaruqÎncă nu există evaluări

- Unit 3 2015Document25 paginiUnit 3 2015pathakpranavÎncă nu există evaluări

- Chapter 8: Memory ManagementDocument51 paginiChapter 8: Memory ManagementRashi KumariÎncă nu există evaluări

- OS Module IVDocument73 paginiOS Module IVsitsekharÎncă nu există evaluări

- Memory Management: Background Swapping Contiguous Allocation Paging Segmentation Segmentation With PagingDocument55 paginiMemory Management: Background Swapping Contiguous Allocation Paging Segmentation Segmentation With PagingsumipriyaaÎncă nu există evaluări

- Chapter - 5 - Memory Management and IO ManagementDocument18 paginiChapter - 5 - Memory Management and IO ManagementNabaa 'Abdallah Salim Al SanidiaÎncă nu există evaluări

- Parallel and Distributed Algorithms-IMPORTANT QUESTIONDocument15 paginiParallel and Distributed Algorithms-IMPORTANT QUESTIONCHITRA MINI100% (1)

- CSC 403 Lecture 2Document16 paginiCSC 403 Lecture 2koredekayode2023Încă nu există evaluări

- CH 6Document37 paginiCH 6jobÎncă nu există evaluări

- Chapter 3Document15 paginiChapter 3yordanos yohannesÎncă nu există evaluări

- In Uni-Processor Systems, Main Memory Is Divided Into Two Parts As Shown BelowDocument32 paginiIn Uni-Processor Systems, Main Memory Is Divided Into Two Parts As Shown Belowgeetanjali_7800Încă nu există evaluări

- Unit 4aDocument104 paginiUnit 4aKoushik ThummalaÎncă nu există evaluări

- Memory Management: Sadaqat Ali Khan BangashDocument27 paginiMemory Management: Sadaqat Ali Khan BangashFasihuddin KhanÎncă nu există evaluări

- Memory Management UpdatedDocument115 paginiMemory Management UpdatedAbhinay YadavÎncă nu există evaluări

- Chapter 3-Memory ManagementDocument51 paginiChapter 3-Memory ManagementdsweetalkerÎncă nu există evaluări

- 16.1 Operating System (0S)Document52 pagini16.1 Operating System (0S)Sevara KazimovaÎncă nu există evaluări

- Chapter 6 - Memory ManagementDocument60 paginiChapter 6 - Memory Managementsibhat mequanintÎncă nu există evaluări

- Basic Operational ConceptsDocument29 paginiBasic Operational ConceptsIndu BalakrishnanÎncă nu există evaluări

- Op Last SladeDocument50 paginiOp Last SladeAzizcan YalçınÎncă nu există evaluări

- Lesson1 Docx-1Document14 paginiLesson1 Docx-1shaikhsahil hafijÎncă nu există evaluări

- 2.operating System - Basics2Document18 pagini2.operating System - Basics2Shashank RahÎncă nu există evaluări

- ES-Module 1Document104 paginiES-Module 1Remya Bharathy100% (1)

- Co Unit 1 NotesDocument51 paginiCo Unit 1 NotesKishan Bhat K100% (1)

- Unit VDocument129 paginiUnit VKHARDEKAR SUJALÎncă nu există evaluări

- Unit 3-Explaining The Memory Management Logical and and Physical Data Flow DiagramsDocument38 paginiUnit 3-Explaining The Memory Management Logical and and Physical Data Flow DiagramsLeah RachaelÎncă nu există evaluări

- Os Unit1Document55 paginiOs Unit1VishwaÎncă nu există evaluări

- HP Data Protector SoftwareDocument22 paginiHP Data Protector Softwareespectante2012Încă nu există evaluări

- 12C Upgrade v2Document33 pagini12C Upgrade v2nakguptaÎncă nu există evaluări

- 1624-MCA (Master of Computer Applications)Document39 pagini1624-MCA (Master of Computer Applications)Leonardo BaileyÎncă nu există evaluări

- Questions & AnswerDocument80 paginiQuestions & Answeranzrain100% (2)

- CS1253 2,16marksDocument24 paginiCS1253 2,16marksRevathi RevaÎncă nu există evaluări

- QuestionsDocument83 paginiQuestionsNagarjuna TammisettiÎncă nu există evaluări

- Linux Commands 3Document52 paginiLinux Commands 3Rakesh RakeeÎncă nu există evaluări

- 12 CSE Syllabus 2012 13Document57 pagini12 CSE Syllabus 2012 13rickyali_rocksÎncă nu există evaluări

- IxServer 6.80 User Guide 6.80Document36 paginiIxServer 6.80 User Guide 6.80iTiSWRiTTENÎncă nu există evaluări

- SQLCAT's Guide To BI and AnalyticsDocument202 paginiSQLCAT's Guide To BI and AnalyticsOluwatobiAdewaleÎncă nu există evaluări

- Master of Computer Applications (Mca)Document65 paginiMaster of Computer Applications (Mca)Ramkishan BohareÎncă nu există evaluări

- Exercise 2 Memory ManagementDocument2 paginiExercise 2 Memory ManagementMayank GargÎncă nu există evaluări

- OS - All-5-UnitDocument185 paginiOS - All-5-UnithariÎncă nu există evaluări

- AIX, Solaris, HP-Ux & Linux Tips For System Administrators: UNIX Commands Comparison SheetDocument17 paginiAIX, Solaris, HP-Ux & Linux Tips For System Administrators: UNIX Commands Comparison SheeteusphorusÎncă nu există evaluări

- Types of Operating System SchedulersDocument26 paginiTypes of Operating System SchedulersVa SuÎncă nu există evaluări

- Debugger Hc12Document52 paginiDebugger Hc12carver_uaÎncă nu există evaluări

- 2020-11-09 10.26.57 Error - 2276Document17 pagini2020-11-09 10.26.57 Error - 2276Steven RaeyenÎncă nu există evaluări

- Oracle Listener Error Code 12500Document3 paginiOracle Listener Error Code 12500sanyahvÎncă nu există evaluări

- Computer Architecture MCQ SDocument19 paginiComputer Architecture MCQ SAbdulRehmanÎncă nu există evaluări

- Rhce NotesDocument46 paginiRhce Notesm988512345Încă nu există evaluări

- Chapter 3 Exercise Answers 1 - 6Document3 paginiChapter 3 Exercise Answers 1 - 6Geovanny Raposo50% (4)

- Session 15 EXT2 and EXT3 AmzbDocument47 paginiSession 15 EXT2 and EXT3 AmzbamzeusÎncă nu există evaluări

- Linux - A Beginner's GuideDocument107 paginiLinux - A Beginner's Guideb3475m3100% (13)

- How To Install Oracle Database 10g Release2 On Widows XPDocument17 paginiHow To Install Oracle Database 10g Release2 On Widows XPmrn_bdÎncă nu există evaluări

- Architecture of 80386Document39 paginiArchitecture of 80386Imran KhanÎncă nu există evaluări

- Chapter 1Document43 paginiChapter 1VishnuNarayananÎncă nu există evaluări

- Unix Sample Questions..Document17 paginiUnix Sample Questions..Sai Anil KumarÎncă nu există evaluări

- NeoPiano Mini ManualDocument18 paginiNeoPiano Mini ManualDD100% (1)

- Combined Paging and SegmentationDocument33 paginiCombined Paging and SegmentationTech_MX100% (1)

- Freebsd GuideDocument131 paginiFreebsd GuideAlexandru-Marian CiotlosÎncă nu există evaluări