DocumentWAVE SHAPINGîncărcat de

DocumentWAVE SHAPINGîncărcat de KavyashreeM

KavyashreeM DocumentPDC_Notes.pdfîncărcat de

DocumentPDC_Notes.pdfîncărcat de KavyashreeM

KavyashreeM Documentde1999 LPVLSI paperîncărcat de

Documentde1999 LPVLSI paperîncărcat de KavyashreeM

KavyashreeM Documentslyw038c.pdfîncărcat de

Documentslyw038c.pdfîncărcat de KavyashreeM

KavyashreeM Documentidoc.pub_vlsi-design-interview-questions.pdfîncărcat de

Documentidoc.pub_vlsi-design-interview-questions.pdfîncărcat de KavyashreeM

KavyashreeM Documentglitch free clock multiplexer(mux) _ RTLeryîncărcat de

Documentglitch free clock multiplexer(mux) _ RTLeryîncărcat de KavyashreeM

KavyashreeM DocumentCH 5.pdfîncărcat de

DocumentCH 5.pdfîncărcat de KavyashreeM

KavyashreeM Documente-2014_0.pdfîncărcat de

Documente-2014_0.pdfîncărcat de KavyashreeM

KavyashreeM DocumentDigital_Systems_Principles_and_Applicati.pdfîncărcat de

DocumentDigital_Systems_Principles_and_Applicati.pdfîncărcat de KavyashreeM

KavyashreeM DocumentPartial_Adiabatic.pdfîncărcat de

DocumentPartial_Adiabatic.pdfîncărcat de KavyashreeM

KavyashreeM DocumentDesign_and_optimization_of_low_voltage_h.pdfîncărcat de

DocumentDesign_and_optimization_of_low_voltage_h.pdfîncărcat de KavyashreeM

KavyashreeM Document76417776-Physical-Design-Complete.pdfîncărcat de

Document76417776-Physical-Design-Complete.pdfîncărcat de KavyashreeM

KavyashreeM Document2009-11EDSSC2009încărcat de

Document2009-11EDSSC2009încărcat de KavyashreeM

KavyashreeM Document1000017819.pdfîncărcat de

Document1000017819.pdfîncărcat de KavyashreeM

KavyashreeM Documentlab3_testbench_tutorial.pdfîncărcat de

Documentlab3_testbench_tutorial.pdfîncărcat de KavyashreeM

KavyashreeM DocumentCummingsSNUG2002SJ_FIFO1_rev1_2încărcat de

DocumentCummingsSNUG2002SJ_FIFO1_rev1_2încărcat de KavyashreeM

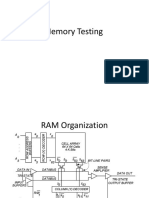

KavyashreeM DocumentUnit4_memorytestingîncărcat de

DocumentUnit4_memorytestingîncărcat de KavyashreeM

KavyashreeM DocumentUnit4_BISTîncărcat de

DocumentUnit4_BISTîncărcat de KavyashreeM

KavyashreeM Document3145_AppB.pdfîncărcat de

Document3145_AppB.pdfîncărcat de KavyashreeM

KavyashreeM Document3145_AppF.pdfîncărcat de

Document3145_AppF.pdfîncărcat de KavyashreeM

KavyashreeM Documentperlîncărcat de

Documentperlîncărcat de KavyashreeM

KavyashreeM Document3145_AppA.pdfîncărcat de

Document3145_AppA.pdfîncărcat de KavyashreeM

KavyashreeM Documentperlîncărcat de

Documentperlîncărcat de KavyashreeM

KavyashreeM DocumentARM_AMBA3_APB.pdfîncărcat de

DocumentARM_AMBA3_APB.pdfîncărcat de KavyashreeM

KavyashreeM Documentmatsuzuka2017încărcat de

Documentmatsuzuka2017încărcat de KavyashreeM

KavyashreeM DocumentARM_AMBA3_APB.pdfîncărcat de

DocumentARM_AMBA3_APB.pdfîncărcat de KavyashreeM

KavyashreeM Documentcapactr_inductr.pdfîncărcat de

Documentcapactr_inductr.pdfîncărcat de KavyashreeM

KavyashreeM DocumentCAP & IND.pdfîncărcat de

DocumentCAP & IND.pdfîncărcat de KavyashreeM

KavyashreeM Documentedge detection.pdfîncărcat de

Documentedge detection.pdfîncărcat de KavyashreeM

KavyashreeM DocumentDadoria2018_Article_PerformanceEvaluationOfDominoLîncărcat de

DocumentDadoria2018_Article_PerformanceEvaluationOfDominoLîncărcat de KavyashreeM

KavyashreeM Document001-course-outline.pptîncărcat de

Document001-course-outline.pptîncărcat de KavyashreeM

KavyashreeM DocumentPartial_Adiabaticîncărcat de

DocumentPartial_Adiabaticîncărcat de KavyashreeM

KavyashreeM DocumentF19_L1_Op_Amp.pptxîncărcat de

DocumentF19_L1_Op_Amp.pptxîncărcat de KavyashreeM

KavyashreeM DocumentF19_L1_Op_Amp (1).pptxîncărcat de

DocumentF19_L1_Op_Amp (1).pptxîncărcat de KavyashreeM

KavyashreeM DocumentDASHBOARDîncărcat de

DocumentDASHBOARDîncărcat de KavyashreeM

KavyashreeM Documentpurchase-orderîncărcat de

Documentpurchase-orderîncărcat de KavyashreeM

KavyashreeM DocumentAnalog lab cadence procedure.pdfîncărcat de

DocumentAnalog lab cadence procedure.pdfîncărcat de KavyashreeM

KavyashreeM DocumentAnalog lab cadence procedure.pdfîncărcat de

DocumentAnalog lab cadence procedure.pdfîncărcat de KavyashreeM

KavyashreeM DocumentIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H.pdfîncărcat de

DocumentIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H.pdfîncărcat de KavyashreeM

KavyashreeM DocumentIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.Hîncărcat de

DocumentIAT-II Question paper with solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.Hîncărcat de KavyashreeM

KavyashreeM Document3 ECE - PDC UNIT - I.pdfîncărcat de

Document3 ECE - PDC UNIT - I.pdfîncărcat de KavyashreeM

KavyashreeM DocumentFSM verilog.pdfîncărcat de

DocumentFSM verilog.pdfîncărcat de KavyashreeM

KavyashreeM DocumentBubble sort.docxîncărcat de

DocumentBubble sort.docxîncărcat de KavyashreeM

KavyashreeM DocumentBubble sort.docxîncărcat de

DocumentBubble sort.docxîncărcat de KavyashreeM

KavyashreeM DocumentDesign_of_a_High_Speed_Adder (1).pdfîncărcat de

DocumentDesign_of_a_High_Speed_Adder (1).pdfîncărcat de KavyashreeM

KavyashreeM DocumentDesign_of_Parallel_Prefix_Adders.pdfîncărcat de

DocumentDesign_of_Parallel_Prefix_Adders.pdfîncărcat de KavyashreeM

KavyashreeM DocumentLOWPOWEREFFICIENTDADDAMULTIPLIER.pdfîncărcat de

DocumentLOWPOWEREFFICIENTDADDAMULTIPLIER.pdfîncărcat de KavyashreeM

KavyashreeM DocumentLOWPOWEREFFICIENTDADDAMULTIPLIERîncărcat de

DocumentLOWPOWEREFFICIENTDADDAMULTIPLIERîncărcat de KavyashreeM

KavyashreeM DocumentECE645_lecture3_fast_adders (1).pptîncărcat de

DocumentECE645_lecture3_fast_adders (1).pptîncărcat de KavyashreeM

KavyashreeM

Documente Academic

Documente Profesional

Documente Cultură