Documente Academic

Documente Profesional

Documente Cultură

Examen AC

Încărcat de

Agafitei AndreiTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Examen AC

Încărcat de

Agafitei AndreiDrepturi de autor:

Formate disponibile

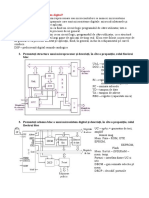

Unitatea Citire/Decodificare

Unitatea Citire/Decodificare este implementat ca band de asamblare, cu apte

segmente, etichetate de la IFU0 la ROB n figura 4.11. Unitile Repartizare/Execuie i

Retragere au alte cinci segmente, formnd n total o band de asamblare cu 12 segmente.

Instruciunile intr n banda de asamblare n segmentul IFU0, unde sunt ncrcate linii

ntregi de 32 octei din memoria intermediar I. Ori de cte ori tamponul intern este gol, se

copiaz n el o alt linie din memoria intermediar. Registrul NEXT ghideaz procesul de

citire.

Fig. 4.11. Structura intern simplificat a unitii Citire/Decodificare

Memorie intermediar I nivel 1

Cache line fetcher

Decodificator al lungimii

instruciunii

Aliniator de instruciuni

Urmtorul IP

Predictor dinamic de

ramificaii

0 1 2

Secveniator de

microoperaii

Predictor static de

ramificaii

Plasator n coada de

microoperaii

Alocator de registre

Microoperaiile trec n ROB

Segment al benzii de asamblare

IFU0

IFU1

IFU2

ID0

ID1

RAT

ROB

Deoarece setul de instruciuni Intel, adesea numit IA32, are instruciuni de lungime

variabil, cu mai multe formate, urmtorul segment al benzii de asamblare, IFU1,

analizeaz fluxul de octei pentru a localiza adresa de start a fiecrei instruciuni. Dac

este necesar, IFU1 poate cuta n avans pn la 30 de instruciuni IA-32. Mergnd att de

departe nainte, ntlnete patru sau cinci ramificaii condiionate. Prediciile nu pot fi

corecte pentru fiecare, aa c valoarea cutrii att de mult n avans este mic. Segmentul

IFU2 aliniaz instruciunile astfel c urmtorul segment le poate decodifica uor.

Decodificarea ncepe n segmentul ID0. Decodificarea n Pentium II const n conversia

fiecrei instruciuni IA-32 n una sau mai multe micro-operaii. Instructiunile IA-32 mai

simple, ca transferurile registru la registru, se pot converti ntr-o singur micro-operaie.

Altele mai complexe pot necesita pn la patru micro-operaii. Cteva extrem de complexe

necesit chiar mai multe i folosesc ROM-ul secveniatorului de micro-operaii pentru a

genera secvena.

Segmentul IDO are trei decodificatoare interne. Dou din ele sunt pentru instruciuni

simple, al treilea le gestioneaz pe celelalte. Ceea ce rezult din segmentul IDO este o

secven de micro-operaii. Fiecare micro-operaie conine un cod de operaie, dou registre

surs i un registru destinaie.

Micro-operaiile sunt plasate n coad n segmentul ID1. Acest segment mai execut i

detecia ramificaiilor. Mai nti se face o predicie static, pentru orice eventualitate.

Predicia depinde de o serie de factori, dar pentru ramificaiile relative la instruciunea

curent se presupune c vor fi efectuate cele napoi, iar cele nainte nu vor fi efectuate.

Dup aceasta urmeaz predictorul dinamic de ramificaii, utiliznd un algoritm bazat pe

istorie ca n figura 4.6. Este evident c pentru o band de asamblare cu 12 segmente

penalizarea pentru o eroare de predicie este enorm, de aceea se utilizeaz 4 bii de istorie

n loc de 2 ca n exemplul prezentat anterior. Dac ramificaia nu este n tabela de istorie,

se utilizeaz predicia static.

Pentru a evita dependenele WAR i WAW, Pentium II permite redenumirea registrelor,

aa cum a fost prezentat pe exemplul din figura 4.8. Registrele reale numite n

instructiunile IA-32 pot fi nlocuite n micro-operaii de oricare din cele 40 de registre

temporale interne localizate n ROB. Aceast redenumire este efectuat n segmentul RAT.

n ROB sunt depozitate cte trei micro-operaii pe ciclu de ceas. Operanzii sunt, de

asemenea, colectai aici, dac sunt disponibili. Dac operanzii unei micro-operaii i

registrul rezultat sunt toi disponibili, iar unitatea de execuie este liber, aceast

instruciune este candidat s fie lansat n execuie. Dac nu, rmne n ROB pn cnd

toate resursele sale au fost obinute.

Unitatea Repartizare/Execuie

Unitatea Repartizare/Execuie este ilustrat n figura 4.12. Unitatea de

Repartizare/Execuie planific i execut micro-operaii, rezolvnd dependenele i

conflictele de resurse. Dei numai trei instruciuni pot fi decodificate pe ciclu de ceas n

ID0, pot fi lansate n execuie pn la cinci micro-operaii ntr-un ciclu, cte una pe fiecare

port. Aceast rat nu poate fi susinut pentru c ea depete capacitatea unitii

Retragere. Micro-operaiile pot fi lansate n orice ordine, dar Unitatea de Retragere le

retrage n ordine. Se utilizeaz o tabel de scor complex pentru a gestiona micro-operaii

n desfurare, registre i uniti de execuie. Cnd o micro-operaie este eligibil pentru

execuie ea poate fi nceput, chiar dac altele puse mai devreme n ROB nu sunt gata. Un

algoritm complex o alege pe cea mai bun instruciune pentru a fi urmtoarea lansat n

execuie cnd mai multe micro-operaii sunt eligibile pentru execuie de ctre aceeai

unitate de execuie. De exemplu, execuia unei ramificaii este mult mai important dect

execuia unei instruciuni aritmetice, deoarece prima afecteaz fluxul programului.

Fig. 4.12. Unitatea de Repartizare/Execuie

Unitatea de Repartizare/Execuie conine o staie de rezervare i uniti de execuie

conectate la cinci porturi. Staia de rezervare este o coad cu 20 intrri pentru micro-

Unitate de execuie MMX

Unitate de execuie n

virgul mobil

Staie de

rezervare

Port 0

Unitate de execuie

pentru ntregi

Unitate de execuie MMX

Unitate de execuie n

virgul mobil

Port 1

Unitate de execuie

pentru ntregi

Port 2 Unitate de ncrcare

Port 3 Unitate de stocare

Port 4 Unitate de stocare

Stocri

Stocri

ncrcri

operaii care au toi operanzii disponibili. Acestea i ateapt rndul n Staia de rezervare

pn cnd unitatea de execuie cerut devine liber.

Exist cinci porturi de la Staia de rezervare la unitile de execuie. Unele uniti de

execuie partajeaz un singur port, aa cum s-a artat. Unitile de ncrcare i Memorare

iniiaz informaiile corespunztoare pentru operaiile de ncrcare i respectiv memorare.

Exist dou porturi pentru memorri. Deoarece numai o singur micro-operaie poate fi

lansat per port i per ciclu, dac dou micro-operaii n desfurare trebuie trimise la

acelai port, una din ele trebuie s atepte.

DIN URMATORUL EXTRAGETI VOI SUBIECTUL 9

MIPS R10000, fabricat n 1996, a nlocuit R8000 pe piaa staiilor de lucru destinate

calculului tiinific. Frecvena de lucru a primei versiuni a fost 200 MHz.

Arhitectura simplificat este dat n figura 5.3 i include:

- cinci canale;

- 64 de registre interne de 64 de bii, att pentru unitatea de ntregi, ct i pentru

unitatea de virgul mobil;

Fig. 5.3. Microprocesoare MIPS R10000

- cache de date i cache de cod de 32 K fiecare, incluznd TLB ce admite 64 de intrri;

- cache L2 de 512 K upgradabil la 16M.

Versiunea procesoarelor MIPS a continuat cu R12000, R14000, R16000, R18000 i

R20000.

Setul de instruciuni al procesoarelor MIPS a evoluat foarte mult. n prezent s-a ajuns la

versiunea MIPS V, fiecare versiune reprezentnd un superset al versiunii precedente. CA

toate mainile RISC, maina MIPS utilizeaz instruciuni de aceeai lungime, 32 de bii, i

avmd trei formate posibile: I-type (immediate), J-type (jump) i R-type (register).

Setul de instruciuni de baz cuprinde cinci mari clase de instruciuni:

- instruciuni de citire/scriere -load/store;

- instruciuni logice i aritmetice;

- instruciuni de salt i salt condiionat;

-instruciuni pentru coprocesor: MIPS definete patru tipuri de coprocesoare: CP0, ...,

Cache L1 cod

32K

ncrcare i

decodificare

instruciuni

Redenumire

registre

Unitate de execuie ntregi

64 registre 64 bii

Z

1

Z

2

ncrcare/s

tocare

Cache L1 date 32K TLB

Unitate de virgul mobil

64 registre 64 bii

Adunare

nmulire, mprire,

radical

16 intrri

16 intrri

Date

16

intr

ri

Adrese

Adrese

salt

Interfa cu

memoria intern

Cache L2

512K-16M

CP3. CP0 are sarcina de a gestiona sistemul memoriei virtuale, de tratare a excepiilor i a

tranzaciilor ntre modul supervizor i modul user. CP1 desemneaz. unitatea de calcul n

virgul mobil, iar CP2 i CP3 sunt rezervate implementrilor viitoare;

- instruciuni speciale.

n versiunea MIPS V, introdus n 1996, este urmat tendina general a tuturor

productorilor de procesoare de a introduce instruciuni speciale destinate accelerrii

operaiilor n virgul mobil, cerute n special n grafica 3D i n calculul tiinific. S-a

definit un nou tip de operand paired-single, ce permite memorarea a doi operanzi n virgul

mobil simpl precizie ntr-un registru dubl precizie. Pentru calcul cu numere ntregi a

fost definit, de asemenea, o extensie denumit MDMX care permite accelerarea calculelor

n aplicaii multimedia i care opereaz pe principiul SIMD (Single Instruction-Multiple

Data).

MIPS R10000 este un procesor RISC superscalar cu instruciuni de tip registru la

registru, singurele instruciuni ce pot accesa memoria fiind load i store. Un numr de

patru instruciuni pot fi planificate pentru execuie n fiecare ciclu. Instruciunile

procesorului R10000 au acces la 32 registre generale de 64 bii i 32 registre n virgul

mobil de 64 bii. Acestea din urm pot fi vzute i ca registre simpl precizie pe 32 bii. De

asemenea, mai exist 32 registre de control i de stare. Tipurile de date recunoscute sunt

numerele ntregi de 8, 16, 32 sau 64 bii. precum i numerele n virgul mobil simpl i

dubl precizie. Instruciunile load/store presupun c datele sunt aliniate n memorie. Exist

i posibilitatea accesrii datelor nealiniate, dar cu preul execuiei a dou instruciuni.

Arhitectura general a procesorului MIPS R 10000 este prezentat n figura 5.4. Aceasta

conine 5 uniti funcionale i o memorie cache de nivel 1 separat pentru date i

instruciuni (cte 32 K fiecare). Cele cinci uniti funcionale ale procesorului sunt:

- ALU1 i ALU2 - uniti aritmetice pentru numere ntregi;

- o unitate de calcul a adreselor destinat instruciunilor load/store;

- o unitate de adunare n virgul mobil;

- o unitate de nmulire n virgul mobil.

Fig. 5.4. Arhitectura microprocesorului MIPS R10000

Unitatea de nmulire n virgul mobil poate efectua totodat i mpriri i extragerea

rdcinii ptrate. Unitile ALU1 i ALU2 nu sunt identice. n timp ce ALU1 trateaz, pe

lng operaiile aritmetico-logice simple, i instruciunile de salt, ALU2 trateaz operaiile

de nmulire i mprire. n cursul executrii unei nmuliri, ALU2 poate trata n paralel i

operaii simple ce necesit doar un ciclu. La terminarea nmulirii, ALU 2 va fi ocupat

dou cicluri pentru scrierea rezultatului n registrele destinaie. n cazul tratrii unei

operaii de mprire, ALU2 este ocupat pn la terminrea operaiei.

Execuia instruciunilor este de tip out-of-order: o instruciune al crei operanzi nu sunt

disponibili nu poate bloca de la planificare instruciuni ulterioare, dar care sunt

executabile. Procesoru1 MIPS R10000 utilizeaz o tehnic de planificare a instruciunilor,

utiliznd trei staii de rezervare de grup:

- una pentru instruciuni load/store, numit memory queue,

- una pentru instruciuni cu numere ntregi, numit integer queue

ITLB

8 entry

BHT

5122

Instruction Cache

32k, two-way associative

PC

Unit

Decode,

Map

Dispatch

Active

List

Map

Table

Map

Table

Memory

Queue

16 entries

Integer

Queue

16 entries

Integer Registers

64 64 bits

FP Registers

64 64 bits

FP

Queue

16 entries

Address

Adder

ALU1 ALU2

FP

Mult

FP

Adder

FP /

sqr

Main TLB

64 entries

Data Cache

32k, two-way associative

Predecod

e

Unit

phys addr

virtual addr

64

128

4 instr.

S

y

s

t

e

m

I

n

t

e

r

f

a

c

e

L

2

C

a

c

h

e

I

n

t

e

r

f

a

c

e

128

Tag

SRAM

Data

SRAM

A

v

a

l

a

n

c

h

e

B

u

s

(

6

4

b

i

t

a

d

d

r

s

/

d

a

t

a

)

- una pentru instruciuni n virgul mobil, numit FP queue, fiecare cu cte 16 intrri.

Benzile de asamblare ale procesorului R10000 sunt prezentate n figura 5.5. Se poate

observa c toate benzile de asamblare utilizeaz 2 niveluri comune: extragere i

decodificare.

Figura 5.5. Benzile de asamblare ale procesorului MIPS R10000

n cadrul primului nivel sunt extrase din memoria cache cte patru instruciuni/ciclu. La

nivelul al doilea, cele patru instruciuni extrase sunt decodificate i tot aici are loc i

redenumirea registrelor. Apoi instruciunile sunt trimise ctre staiile de rezervare

corespunztoare. Instruciunile fiind acum plasate n staiile de rezervare, de la nivelul al

treilea al benzii de asamblare se poate ncepe execuia propriu-zis. Sarcina celui de al

treilea nivel din banda de asamblare este aceea de a verifica disponibilitatea operanzilor

instruciunilor din staiile de rezervare i de a trimite ctre unitile funcionale acele

instruciuni care au operanzii disponibili. Tot aici are loc i verificarea prediciei efectutate

asupra unei instruciuni de salt n caz c operandul acestei instruciuni este disponibil. n

urmtoarele niveluri are loc execuia instruciunilor de ctre unitile funcionale

corespunztoare. Fiecare tip de instruciune necesit un numr diferit de niveluri pentru

execuie, dup cum se poate observa i n figura 5.5. Ultimul nivel este acelai pentru toate

benzile de asamblare-scrierea rezultatului n registrul destinaie.

Dependenele false dintre instruciuni sunt rezolvate prin metoda redenumirii

registrelor. Dei utilizatorii au la dispoziie 32 de registre pentru numere ntregi i tot

attea pentru numere n virgul mobil, procesorul are n realitate 64 registre fizice pentru

numere ntregi i 64 registre fizice pentru numere n virgul mobil. Corespondena ntre

registrele arhitecturale i cele fizice este urmrit cu ajutorul unui tabel de mapare -

Mapping Table. Totodat, mai exist nc un tabel denumit Free List care menine o list

cu toate registrele fizic libere, disponibile pentru redenumire.

MIPS Rl0000 are dou niveluri de memorie cache. Memoria cache primar este partajat

Fetch Decode Insue

Insue

Insue

Execute Write

Addr Cache Write

EX1 EX2 EX3 Write

ALU

MEMORY

FPU

n cache de date (32 KB) i cache pentru instruciuni (32 KB) i este integrat pe cipul

procesorului. Memoria cache de nivel 2 este unificat i poate avea o capacitate cuprins

ntre 512 KB i 16 MB. Memoriile cache sunt organizate asociativ pe dou ci i utilizeaz o

politic de nlocuire de tip LRU. La ncarcarea instruciunilor n memoria cache de nivel 1

se adaug cte 4 bii de predecodificare, deci pe lng 32 KB destinai instruciunilor

propriu-zise mai sunt necesari 4 K pentru biii de predecodificare. O linie din cache

memoreaz 16 instruciuni de 36 bii (incluznd biii de precodificare). Pentru fiecare linie

exist cte un bit care ajut la meninerea coerenei cu memoria. Memoria cache de nivel 1

pentru date, ct i cea de nivel 2 utilizeaz o politic de scriere de tip write-back. Pentru o

mai bun nelegere a celor afirmate este necesar parcurgerea capitolului 6.

Procesorul UltraSPARC este un procesor superscalar care poate lansa n execuie patru

instruciuni/ciclu. Instruciunile sunt lansate n ordine, dar se pot termina n alt ordine.

Totui ntreruperile sunt precise, adic se tie exact n ce stare era maina cnd a aprut o

ntrerupere. Exist suport hardware pentru ncrcri speculative sub forma instruciunii

PREFETCH care nu genereaz o eroare la o ratare n memoria intermediar i nici nu sunt

blocate accesele urmtoare la memorie. Setul de instruciuni utilizat n procesorul

UltraSPARC, SPARC V9, grupeaz instruciunile n urmtoarele mari clase:

- instruciuni de acces la memorie: singurele instruciuni care au acces la memorie

sunt load/ store. Exist cteva instruciuni load/store speciale;

- instruciuni de acces atomic la memorie;

- instruciuni de citire care nu provoac excepii;

- instruciuni de prencrcare a datelor.

- instruciuni aritmetico-logice pentru lucrul cu numere ntregi;

- instruciuni n virgul mobil;

- instruciuni de transfer al controlului;

- instruciuni de transfer condiionat: o valoare memorat ntr-un registru este

copiat n alt registru n funcie de valoarea unui al treilea registru;

- instruciuni de acces la registrele de stare;

- instruciuni de gestiune a ferestrelor de registre.

Pe lng instruciunile clasice, a fost definit i o extensie la setul de instruciuni,

numit VIS - Visual Instructions Set, extensie implementat pentru prima dat la

procesorul UltraSparc. Instruciunile VIS sunt destinate, n special, mbuntirii

performanelor grafice i de prelucrare a imaginilor, analog instruciunilor MMX de la

Pentium II. Se definesc noi tipuri de date pentru prelucrarea pixelilor, precum i

instruciuni specifice de prelucrare a acestora (instruciuni ce folosesc principiul de operare

SIMD).

UltraSparc are 32 de registre generale pe 64 de bii (opt pentru execuia normal, opt

pentru rutinele de tratare a ntreruperilor, opt folosite de unitatea de gestiune a memoriei

i opt pentru tratarea excepiilor), 32 de registre pentru numere n virgul mobil pe 64 de

bii, dar care pot fi privite i ca 16 registre pe 128 bii i registre de stare i control.

Originalitatea arhitecturii acestui procesor provine din utilizarea ferestrelor de registre

(opt ferestre a cte 24 de registre). La un moment dat o instruciune poate accesa opt

registre generale (R0 ... R7) i 24 de registre ale ferestrei curente-opt registre de intrare,

opt de ieire i opt registre locale. Ferestrele de registre permit apelul i ntoarcerea din

proceduri, fr a fi nevoie s se salveze date n memorie.

Arhitectura detaliat procesorului UltraSparc este prezentat n figura 5.7. Dup cum se

poate observa, procesorul UltraSparc integreaz pe cip urmtoarele componente:

- o unitate de prencrcare a instruciunilor de predicie a salturilor i de planificare a

instruciunilor (Prefetch and Dispatch Unit);

- o unitate de gestiune a memoriei cu 64 intrri pentru date i 64 intrri pentru

instruciuni MMU;

- o memorie cache de nivel 1 divizat: 16 KB instruciuni i 16 KB pentru date;

- dou uniti de lucru cu numere ntregi ALU;

- o unitate funcional pentru instruciunile load/store;

Figura 5.7. Arhitectura procesorului UltraSparc

- trei uniti de lucru n virgul mobil: una pentru adunare /scdere, una pentru

nmuliri i una pentru mpriri i radcin ptrat;

- dou uniti grafice;

- o unitate de interfa.

Unitatea de prencrcare are rolul de a extrage instruciunile n avans fa de execuia

programului. In fiecare ciclu pot fi extrase patru instruciuni. Instruciunile extrase din

memoria cache i decodificate sunt memorate ntr-o coad de instruciuni cu 12 intrri

unde vor atepta s fie trimise mai departe n banda de asamblare. Din aceast coad de

instruciuni se pot lansa cte patru instruciuni/ciclu, planificarea fiind de tip in-order.

Unitatea de gestiune a memoriei are rolul de a traduce adresele virtuale (pe 44 bii) n

adrese fizice (pe 41 bii). Cele dou TLB, pentru instruciuni i pentru date, au amndou

Instr TLB (64

intrri)

Instruction Cache

(16k plus next field, branch hist)

Predecode

Unit

Decode

Unit

Prefetch

Unit

Dispatch

Unit

Branch

Unit

4 instr.

4 instr.

Instruction

Buffer

(12 intrri 4 instr.

Next field,

Branch hist

taken/not taken

Adresa

virtual

4 instruciuni decodificate

Load/

Store

Unit

Integer

Unit

(includes

Mult, Div)

Integer

Unit

(ALU

only)

FP

Unit

(Add

Sub)

FP

Unit

(Multiply)

FP

Unit (divide

Sq Root)

Graph

Unit

(Add

Sub)

Graph

Unit

(Multiply)

144

64 64 64 64 64 64 64 64

Integer Registrers

(8 windows, 7 read, 3 write

ports)

Floating-Point Registers

(5 read ports, 3 write ports) Completion

Unit

Completion

Unit

Data Cache

(16 k)

Data TLB

(64 intrri)

Cache Control/

System Interface

A

d

r

e

s

a

v

i

r

t

u

a

l

128

128 bits

cte 64 de intrri i sunt total asociative.

Unitatea load/store va genera adresele virtuale pentru toate instruciunile load i store

i va accesa memoria cache de date.

Unitatea de lucru cu numere ntregi este compus de fapt din dou ALU care nu au n

componen i un multiplicator i un divizor pentru numere ntregi.

Unitile de lucru n virgul mobil, n numr de trei, sunt organizate n band de

asamblare, mai puin cea pentru mprire i extragerea rdcinii ptrate. Acestea

acceseaz un banc de 32 registre pe 64 bii care pot fi utilizate i ca 16 registre de 128 bii,

iar la fiecare tact de ceas se pot executa maxim dou instruciuni n virgul mobil.

Unitatea grafic trateaz toate instruciunile destinate special prelucrrilor grafice -

VIS. Aceast unitate, care folosete acelai banc de registre cu unitatea n virgul mobil.

este compus dintr-un sumator i un multiplicator.

Procesorul UltraSparc utilizez o band de asamblare cu nou niveluri sau segmente,

band care este prezentat n figura 5.8, anumite segmente fiind diferite pentru

instruciuni cu intregi i instruciuni n virgul mobil.

Instruciunile cu numere ntregi utilizeaz de fapt numai 6 niveluri din banda de

asamblare, dar nivelul WriteBack, care are rolul de a scrie rezultatele n registrele

destinaie, este ntrziat cu trei niveluri, pentru a permite o gestiune precis a

ntreruperilor.

Nivelul Fetch extrage din memoria cache pentru instruciuni, dac este posibil, patru

instruciuni/ciclu. Acest lucru este posibil doar n condiii perfevte, adic fr ratri n

memoria cache, fr predicii greite, fr instruciuni dificile, combinarea corect a

instruciunilor. Aceste instruciuni sunt decodificate la nivelul urmtor, Decode, i plasate

n coada de instructiuni ce are 12 intrri. Pe lng instruciunile propriu-zise, n aceast

coad mai sunt adugai i bii de decodificare. Aceti bii de decodificare adugai fiecrei

instruciuni fac mai rapid prelucrarea ulterioar, prin direcionare imediat ctre

unitatea de prelucrare adecvat. n segmentul Group sunt citite din coad cte patru

instruciuni valide pe ciclu i sunt trimise spre execuie n ordine. Aici sunt examinate

instruciunile decodificate pentru a detecta dac sunt compatibile pentru lansare

simultan. Instruciunile sunt valide dac operanzii lor sunt disponibili i unitile

funcionale respective sunt libere. Registrele pentru numere ntregi sunt citite tot n acest

nivel. Din acest moment, benzile de asamblare pentru ntregi i pentru virgul mobil se

despart.

Figura 5.8. Banda de asamblare a procesorului UltraSparc

n banda de asamblare pentru ntregi, la nivelul Execute are loc execuia majoritii

instruciunilor direct, ntr-un ciclu. Pentru instruciunile load/store aici are loc calcularea

adresei virtuale. n continuare, se acceseaz memoria cache la nivelul Cache cu adresa

fizic obinut din TLB. Pentru instruciunile aritmetico-logice registru-registru, la

nivelurile N1 i N2 nu se execut nimic, dar acestea au fost introduse pentru a se pstra

sincronizarea celor dou benzi de asamblare. Pentru instruciunile load/store segmentul N1

va verifica ratrile n cache i va scrie adresele de unde vor trebui citite/scrise date ntr-un

tampon de citire, respectiv scriere. Dup nivelul N2, cnd i termin execuia i

majoritatea operaiilor n virgul mobil, rezultatele instruciunilor pot fi direct utilizate

printr-un mecanism de bypass. Terminarea fiecrei instruciuni ntregi cu cteva

nanosecunde mai trziu, prin introducerea segmentelor N1 i N2, este un pre pltit pentru

evitarea perturbrii fluxului benzii de asamblare.

Instruciunile n virgul mobil parcurg o band de asamblare cu patru segmente

proprii. Acestea acceseaz registre la nivelul Register i se execut n urmtoarele trei

cicluri la nivelurile Xl, X2. X3 (excepie fac mpririle - 12 cicluri - i rdcina ptrat - 22

de cicluri). Nivelul N3 este utilizat de procesor pentru detectarea condiiilor de excepie

care pot apare; spre exemplu, la o mprire la zero. Rezultatele instruciunilor sunt scrise

n registrele destinaie n nivelul Write- Back.

UltraSparc dispune de un mecanism de planificare a instruciunilor mai simplu dect

alte procesoare (cum ar fi DEC Alpha 21264, MIPS Rl0000 etc.), care lanseaz

instruciunile n execuie n ordinea programului, maxim patru instruciuni pe ciclu.

Memoria cache pentru instruciuni, care este organizat asociativ pe seturi cu dou ci,

stocheaz instruciunile care sunt precodificate. Din cache spre coada de instruciuni pot

pleca cte 4 instruciuni aliniate pe ciclu. n coada de instruciuni, fiecare intrare are 62 de

bii, biii suplimentari permind s se detecteze rapid dependenele ntre date i resurse.

n vederea planificrii pentru execuie, instruciunile sunt clasificate pe tipuri: instruciuni

Register X1 X2 X3

N3 WriteBack

Execute Cache N1 N2

Fetch Decode Group

Principal pipeline

Floating point pipeline

load/store, instruciuni pentru ntregi, instruciuni de control, instruciuni n virgul

mobil. La nivelul Group din banda de asamblare se formeaz grupuri de patru instruciuni

gata pentru execuie conform unor reguli de selecie. Astfel, n acest grup pot fi cel mult

dou instruciuni pentru ntregi i dou pentru numere n virgul mobil i o singur

instruciune de tip load/store. De asemenea, instruciunile pentru ntregi i cele load/store

trebuie s fie ntre primele trei instruciuni din grup. Trebuie s menionm c dependene

de tipul WAW sau WAR nu pot aprea, deoarece instruciunile sunt executate n ordine.

Predicia salturilor la UltraSparc utilizeaz acelai mecanism cu doi bii de istorie ca i

MIPS R10000. Tabela de predicie este ns integrat n memoria cache: la fiecare dou

instruciuni sunt adugai doi bii de istorie a salturilor. Biii de istorie sunt iniializai

dup un mecanism de predicie static. Predicia adresei de salt este realizat de un

mecanism denumit Branch Following. La fiecare patru instruciuni n cache este adugat

un cmp denumit Next Field de 13 bii. Acest cmp indic din ce poziie a cache-ului

trebuie ncrcate urmtoarele instruciuni.

Memoria cache de nivel 2 poate avea dimensiuni cuprinse ntre 512 KB i 4 MB; este de

tip direct-mapped i utilizeaz o tehnic de scriere write-back. Linia de memorie cache are

dimensiunea de 64 bytes. Fiecare intrare n cache conine 25 de bii de adres fizic, trei

bii de stare pentru protocolul de meninere a coerenei i 8 bii de paritate.

UllraSparc I a utilizat o tehnologie CMOS de 0,5 m cu patru straturi de metal i avea

52 milioane de tranzistori. UltraSparc II este realizat n tehnologie de 0,25 m iar

UltraSparc III, folosete tehnologia de 0,18 m.

Clasificare, memoriile utilizate n calculatoare se clasific n dou categorii :

- ROM (Read Only Memory) acest tip de memorie nu poate fi rescris ori tears.

Avantajul principal pe care aceast memorie l aduce este insensibilitatea fa de

curentul electric. Coninutul memoriei se pstreaz chiar si atunci cnd nu este

alimentat cu energie.

- RAM (Random Access Memory), este memoria care poate fi citit ori scris n mod

aleator; n acest mod se poate accesa o singura celula a memoriei fr ca acest lucru

s implice utilizarea altor celule. n practic, este memoria de lucru a calculatorului

i aceasta este util pentru prelucrarea tempoarar a datelor, dup care este

necesar ca datele s fie stocate (salvate) pe un suport ce nu depinde direct de

alimentarea cu energie pentru a menine informatia.

Memoria ROM este n general utilizat pentru a stoca BIOS-ul (Basic Input Output

System) unui PC. n practic, o dat cu evoluia PC-urilor acest timp de memorie a suferit o

serie de modificri care au ca rezultat rescrierea/arderea "flash" de ctre utilizator a BIOS-

ului. Scopul, evident, este de a actualiza funciile BIOS-ului pentru adaptarea noilor cerine

si realizri hardware, ori chiar pentru a repara unele imperfeciuni de funcionare. Astfel

c in zilele noastre exista o multitudine de astfel de memorii ROM programabile (PROM,

EPROM, etc) prin diverse tehnici, mai mult sau mai puin avantajoase n funcie de gradul

de complexitate al operrii acestora. BIOS-ul este un program de mrime mic (< 2MB)

fr de care computerul nu poate funciona. Acesta reprezint interfaa ntre componentele

din sistem i sistemul de operare instalat (SO).

Memoria RAM se clasifica n SRAM (Static) i DRAM (Dinamic).

- SRAM - acest tip de memorie utilizeaz n structura celulei de memorie 4 tranzistori

i 2 rezistene. Schimbarea strii ntre 0 i 1 se realizeaz prin comutarea strii

tranzistorilor. La citirea unei celule de memorie informaia nu se pierde. Datorit

utilizrii matricei de tranzistori, comutarea ntre cele dou stri este foarte rapid.

- DRAM are ca principiu constructiv celula de memorie format dintr-un tranzistor i

un condensator de capacitate mic. Schimbarea strii se face prin

ncrcarea/descrcarea condensatorului. La fiecare citire a celulei, condensatorul se

descarc. Aceast metod de citire a memoriei este denumit "citire distructiva". Din

aceast cauz celula de memorie trebuie sa fie rencrcat dup fiecare citire. O alt

problem, care micoreaz performanele n ansamblu, este timpul de remprosptare

al memoriei, care este o procedur obligatorie i are loc la fiecare 64 ms.

Remprosptarea memoriei este o consecin a principiului de funcionare al

condensatorilor. Dup o anumit perioad de timp energia nmagazinat scade n

intensitate datorit pierderilor din dielectric. Aceste probleme de ordin tehnic conduc la

creterea timpul de asteptare (latency) pentru folosirea memoriei.

Datorit rspndirii vaste a memoriei de tip DRAM, vom exemplifica modul de

funcionare al celulei de memorie pe baza acestei tehnologii. Celula de memorie, este cea

mai mic unitate fizic a memoriei. Este compus din componente electronice discrete.

Principiul de funcionare este n fapt modificarea strii logice ntre 0 i 1, care la nivel fizic,

n funcie de tehnologia utilizat, corespunde cu nmagazinarea energiei electrice prin

intermediul unui condensator (pentru DRAM), ori cu reconfigurarea matricei de tranzistori

(n cazul SRAM). Celula de memorie, din punct de vedere logic, este tratat ca fiind un bit.

Cea mai mic unitate logica adresabil a memoriei este format din opt bii i se numete

byte. Acesta ofer posibilitatea obinerii a 256 combinaii (caractere). Prin gruparea a opt

bytes se obine un cuvnt (word). Constructiv, din motive ce in de proiectare, celulele de

memorie sunt organizate sub forma unor matrici. Pentru identificarea i accesarea celulelor

de memorie, acestea dispun de o adres unic pentru fiecare celul n parte. Identificarea

celulei de memorie se face prin transmiterea adresei acesteia prin BUS-ul de adrese ctre

decodorul de adres (format din decodoare pentru linie i coloan); acesta identific celula

de memorie care corespunde adresei primite i transmite coninutul acesteia ctre interfaa

de date, iar aceasta, mai departe, ctre BUS-ul de date. Se consider celul de memorie

circuitul elementar care realizeaz memorarea unui bit. Acesta se poate realiza, dup cum

am spus, cu tranzistoare bipolare sau cu tranzistoare MOS. Circuitul de memorie propriu-

zis este aranjat sub forma unei matricii n ale crei noduri se gsesc celulele de memorie.

Structura circuitului de memorie avnd dimensiunile n x m este dat n fig. 6.3.

1

2

m

WL

m

WL

1

WL

2

DL

1

DL

1

DL

2 DL

2 DL

n

DL

n

Fig. 6.3. Structura unei matricii de memorie

Pentru accesul la celula de memorie (i, j) se face selecia liniei WLi i selecia coloanei

DLj,

j

DL . Capacitatea memoriei este dat de produsul m x n.

ASTA NU STIU DACA TREBUIE, VEDETI VOI CAND O CITITI

Deosebiri SRAM/DRAM

Principalul avantaj al memoriei dinamice (DRAM) este preul foarte redus pentru

obinerea unei celule. De altfel, acesta este i singurul plus pe care aceast memorie l are

n comparaie cu SRAM. n schimb performanele sunt cu mult n urma memoriei statice

(SRAM). Datorit modului prin care se comut ntre strile 0 i 1 i a modului n care se

execut citirea celulei de memorie, SRAM nu are nevoie de rescriere a datelor dup ce

acestea au fost citite i nici de remprospatarea celulei de memorie. Atfel c timpii de acces

sunt mult mai mici, iar viteza la care acest tip de memorie lucreaz depete cu mult

performanele memoriei dinamice. Datorit preului de cost mare pentru obinerea unei

celule SRAM, acest tip de memorie este utilizat numai pentru fabricarea memoriei cache ce

se implementeaz n plcile de baz sub denumirea de cache level 2 (L2) ori pentru

memoria cache level 1 (L1) ce este integrat n structura procesoarelor. Memoria cache L1

functioneaz la aceai frecven cu cea a procesorului, n timp ce pentru memoria cache L2

frecvena de lucru este jumtate fa de frecvena procesorului. Memoria cache a fost

introdus ca un artificiu tehnologic, dar de mare utilitate, care trebuie s suplineasc

diferena de frecven de lucru dintre procesor i memorie.

Circuite cu memorii RAM

n figura 6.4 sunt evideniate blocurile componente necesare funcionrii unui circuit

de memorie RAM. Matricea de memorie conine la intersecia unei linii cu o coloan o

celul de un bit. Decodificatoarele activeaz liniile de la selecie cuvnt WL0 WLp (unde p

= 2

n

) i pe de alt parte circuitele de citire pentru fiecare coloan, pe liniile DL0 DLq (unde

q = 2

m

).

Semnalele sunt transmise n exterior prin intermediul unor circuite de I/E. Circuitul de

control activeaz ansamblul de circuite interne ce poate participa la realizarea funciei

(citire sau scriere). n memoriile RAM dinamice circuitul de control este mai complicat

deoarece genereaz secvena de citire a informaiei din celul i revizuirea acesteia. Pentru

stocarea simultan a mai multor bii se multiplic cu numrul de bii toate circuitele n

afar de decodificatoare i circuite de control. n acest caz, un circuit de memorie va avea o

structur ca cea din figura 6.5.

Fig. 6.4. Schema bloc a unui circuit de memorie de 1 bit.

D

E

C

O

D

I

F

I

C

A

T

O

R

MATRICE DE

MEMORIE

2

m

2

n-m

CIRCUITE CITIRE I

SCRIERE

DECODIFICATOR

COLOANE

CIRCUITE

INTRARE

CIRCUITE

IEIRE

CONTROL

A

0

A

1

A

m-1

W

LO

W

L1

W

LP

DL

0 DL

1

DL

n

A

m

A

n-1

CS

R/W

D

1n

D

0

Fig. 6.5. Schema bloc a unui circuit de memorie

cu mai muli bii pe cuvnt.

Trebuie remarcat c citirea i scrierea de date nu se fac simultan i ca urmare pinii de

date de intrare/ieire pot fi comuni, sensul transferului prin circuitele de intrare/ieire fiind

stabilit de circuitul de control n funcie de comanda primit. Rezult posibilitatea

micorrii numrului de legturi externe ale circuitului. Schema bloc a unui circuit de

memorie poate fi redesenat punnd n eviden transferurile de date pe o magistral

intern ca n figura 6.6. Matricea de memorie, amplificatoarele de scriere/citire, circuitele

I/O sunt considerate n acest caz blocuri multiple lucrnd pe mai muli bii.

D0k-1

MATRICE DE

MEMORIE

2

m

2

n-m

A0

Am-1

k circuite

CIRCUITE CITIRE I

SCRIERE

DECODIFICATOR

COLOANE

Am

An-1

CONTROL

CS R/W

CIRCUITE

IEIRE

D00

D1

Dln k-1

CIRCUITE

INTRARE

Dln0

Fig. 6.6. Schema bloc a unei memorii RAM

Matricea de memorie are o structur intern ce se reflect n geometria extern a

memoriei prin numrul de bii din cuvnt (D0 Dk. n cazul nostru). mprirea pe linii i

coloane a acestei matricii nu este sesizabil din exterior, adresele A0 An-1 fiind tratate

nedistinctiv n afar.

Memorie intermediar cu coresponden direct

Cea mai simpl memorie intermiediar este memoria intermediar cu oresponden (direct-

mapped cache). Un exemplu de memorie intermediar cu coresponden direct este artat n figura

6.13.. Aceast memorie intermediar conine 2

14

intrri. Fiecare intrare (rnd) din memorie

intermediar poate conine exact o linie din memoria principal. Cu o dimensiune a liniei memoriei

intermediare de 4 de octei (pentru acest exemplu), memoria intermediar poate conine 64 de KB.

Procedura de mapare este dat de

i = j modulo m

unde

i =numrul liniei din cache,

j = numrul blocului din memoria principal,

D

E

C

O

D

I

F

I

C

A

T

O

R

MATRICE DE

MEMORIE

2

m

2

n-m

DECODIFICATOR

COLOANE

Amplificator

SCRIERE

CONTROL

A

0

A

1

A

m-1

A

m

A

n-1

C

3

R/W

CIRCUITE I/O

D

0

D

k D

1

Amplificator

CITIRE

MAGISTRAL INTERN DATE

m = numrul de linii din cache.

Fig. 6.13. Organizarea memoriei cache cu coresponden direct.

Funcia de mapare este implementat uor folosind adresa. n scopul maprii, fiecare adres din

memoria principal poate fi vzut ca fiind format din trei cmpuri. Cei mai puin semnificativi w bii

identific n mod unic un cuvnt sau byte dintr-un bloc al memoriei principale; s presupunem c

adresarea este la nivel de byte. Poriunea de s bii rmai din adres specific unul din cele 2

s

blocuri din

memoria principal. Logica cache-ului interpreteaz aceti s bii ca un tag de s-r bii i un cmp de linie

de r bii. Acesta din urm identific una din cele 2

r

linii din cache. Efectul acestei mapri este c blocurile

din memoria principal sunt asignate liniilor de cache dup cum urmeaz:

Tag Line Word

Memory Address

-

-

-

-

-

-

Compare

(Hit in Cache)

L

0

L

i

L

m-1

s - r

r

w

s -w

(Miss in Cache)

w

s - r

B

0

-

-

-

B

j

-

-

-

w

s

W0

W1

W2

W3

W4j

W(4j+1)

W(4j+2)

W(4j+3)

Main Memory

Cache

Tag Data

Linia de

cache

Blocuri din memoria principal asignate

0

0, m, 2m, ,2

s

-m

1

1, m+1, 2m+1, ,2

s

-m+1

.

.

.

.

.

.

m-1

m-1, 2m-1, 3m-1, ,2

s

-1

Deci utilizarea unei poriuni de adres ca numr de linie asigur o mapare unic a fiecrui bloc din

memoria principal n cache. Cnd un bloc este efectiv citit n linia asignat acestuia, este necesar s se

marcheze cu tag data pentru a o deosebi de alte blocuri ce pot fi plasate n aceeai linie. Cei mai

semnificativi s-r bii servesc n acest scop.

Figura 6.14 prezint exemplul ales de noi folodind maparea direct. Pentru exemplul considerat

m=16K=2

14

i i=j modulo 2

14

, w=2 i r= 14, s=22. Rezult:

Linia de

cache

Adresa de nceput a blocului din memoria principal

0 000000, 010000 ,FF0000

1 000004, 0100041, ,FF0004

.

.

.

.

.

.

m-1 00FFFC, 01FFFC, ,FFFFFC

Se observ c nu se poate ntmpla ca dou blocuri ce se mapeaz n aceeai linie s aib acelai

tag. Astfel blocurile 000000, 010000,, FF0000 au numerele tag 00, 01, ,FF.

Revenind la figura 6.14, o operaie de citire se desfoar dup cum urmeaz. Memoria cache are

adresa de 24 de bii. Adresa liniei de cache este de 14 bii. Dac tag-ul de 8 bii este identic cu tag-ul

liniei respective, se selecteaz un cuvnt din cele 4 din linia de cache pe baza cmpului Word de 2 bii.

Altfel spus, 22 de bii (Tag+Line) servesc pentru a aduce un bloc din memoria principal n cache. Adresa

aceasta este completat cu 2 bii 0 i este adresa de nceput a unui bloc (linii) din cache de 4 bytes.

Fig. 6.14. Exemplu de mapare cu coresponden direct.

Aceast tehnic de mapare este simpl i are costuri mici de implementare. Principalul dezavantaj

este acela c exist o locaie fix n cache pentru orice bloc. Dac se ntmpl ca un program s necesite

repetat cuvinte din dou blocuri ce se mapeaz n aceeai linie, linia respectiv va fi rencrcat repetat

i efectul folosirii memoriei cache este sczut. De fapt, n cazul cel mai defavorabil, folosirea unei

memorii intermediare este mai ineficient dect n cazul n care aceasta ar lipsi, cci fiecare operaie de

memorie implic citirea unei ntregi linii de memorie intermediar n locul unui singur cuvnt.

n ciuda complexitii deciziei, accesul la un cuvnt necesar poate s fie remarcabil de rapid. De

ndat ce adresa este cunoscut, locaia exact a cuvntului este tiut, dac este prezent n memoria

intermediar. Aceasta nseamn c este posibil s se citeasc cuvntul din memoria intermediar i s se

13579246

Data

0000

0004

FFF8

FFF9

Line+

Word

Tag

00

-

-

-

77777777

11235813

FEDCBA98

12345678

0000

0004

FFFC

16

-

-

-

12345678

24682468

0000

0004

FFF8

FFFC

FF

13579246

11235813

FEDCBA98

11223344

12345678

00

16

16

FF

16

0000

0001

OCE7

3FFE

3FFF

~ ~

~

~

~

~

~

~

~ ~

~

~

Tag Data

Numr

linie

8 Bits 32 Bits

16-K word Cache

32 Bits

16-Mbyte Main Memory

Adresa din mem. principal=

8 14 2

Tag Line Word

livreze procesorului n acelai timp determinndu-se dac este cuvntul corect (prin compararea

etichetelor). Astfel procesorul primete de fapt un cuvnt din memoria intermediar aflnd simultan sau

poate chiar mai trziu dac este cuvntul cerut.

Memoriile intermediare cu coresponden direct reprezint tipul cel mai comun de memorie

intermediar i acestea lucreaz destul de eficient, pentru c interferenele de genul celei descrise mai

nainte pot fi reduse la minim. De exemplu un compilator foarte inteligent poate s in seama de

interferene cnd plaseaz instruciuni i date n memorie. Remarcai c situaia particular descris nu

va aprea ntr-un sistem cu memorii intermediare separate pentru instruciuni i date, deoarece

cererile-interferene vor fi servite de memorii intermediare diferite. Astfel putem observa un al doilea

beneficiu al folosirii a dou memorii memorie intermediar n loc de una singur - mai mult flexibilitate

n tratarea abloanelor conflictuale de memorie.

Memorie intermediar asociativ

Acestea nu au dezavantajul maprii directe, permind fiecrui bloc din memoria principal s fie

ncrcat n orice linie din cache. n acest caz logica de control a memoriei cache interpreteaz o adres

de memorie ca un cmp tag i un cmp word. Cmpul tag identific unic un bloc din memoria principal.

Pentru a determina care bloc este ncrcat n cache, logica de control a cache-ului trebuie s examineze

simultan fiecare linie tag pentru a descoperi coincidena cmpurilor. Figura 6.15 ilustreaz aceast

logic.

Figura 6.16 prezint exemplul anterior utiliznd tehnica maprii asociative. Memoria principal va

avea o adres format din cmpul tag de 22 de bii i cmpul word de 2 bii. Cmpul tag de 22 de bii

trebuie stocat mpreun cu un bloc de 32 de bii n fiecare linie din cache. De remarcat c cei mai

semnificativi 22 de bii formeaz cmpul tag. Deci adresa hexazecimala de 24 de bii 16339C are tag

058CE7. Acest fapt rezult usor din notaia binar:

Adresa de memorie 0001 0110 0011 0011 1001 1100 (binar)

1 6 3 3 9 C (hex)

Tag (most sig. 22bit) 0000 0101 1000 1100 1110 0111 (binar)

0 5 8 C E 7 (hex)

Figura 6.15 Organizarea memoriei cache complet asociativ

Prin mapare asociativ exist o flexibilitate cu privire la care bloc va fi nlocuit cnd un nou bloc este

adus n cache. Algoritmii de nlocuire, care vor fi discutai puin mai trziu n aceast seciune, au rolul

de a maximiza rata de succes. Principalul dezavantaj al memoriilor cache complet asociative este acela

c este necesar un circuit complex pentru a analiza cmpurile Tag ale tuturor liniilor din cache n paralel.

Tag Word

Adresa de memorie

-

-

-

-

-

-

(Hit in Cache)

L

0

L

j

L

m-1

s

w

s -w

(Miss in Cache)

w

B

0

-

-

-

B

j

-

-

-

w

s

W0

W1

W2

W3

W4j

W(4j+1)

W(4j+2)

W(4j+3)

Memoria principal

Cache

Tag Data

Compar

s

- - -

Figura 6.16 Exemplu de mapare asociativ.

Memorii intermediare asociative pe seturi

Aceast variant este un compromis ce beneficiaz de avantajele celor dou abordri anterioare i

care ncearc totodat s le minimizeze dezavantajele. In acest caz, memoria este mprit n v seturi,

fiecare set avnf k linii de cache. Relaiile sunt:

m = v k

i = j modulo m

unde

i = numrul liniei din cache,

j = numrul blocului din memoria principal,

m = numrul de linii din cache.

22 2

13579246

FEDCBA98

33333333

11223344

24682468

11223344

FEDCBA98

33333333

13579246

24682468

3FFFFE

058CE7

3FFFFD

000000

3FFFFF

0000

0001

3FFD

3FFE

3FFF

~

~ ~

Tag Data

Numr

linie

22 Bits 32 Bits

16-K word Cache

Data

~

~

Addresa

00000

163398

16339C

1633A0

FFFF4

FFFF8

FFFFC

~

~ ~

~

~

32 Bits

16-Mbyte Main Memory

Adresa memoriei principale=

Tag Word

Aceasta este referit ca mapare asociativ pe k seturi. Cu o asrfel de mapare asociativa pe seturi,

blocul B

j.

Poate fi mapat n oricare din liniile setului i. Logica de control interpreteaz o adres de

memorie ca trei cmpuri: tag, set i word. Cei d bii din cmpul tag definesc unul din cele v=2

d

seturi. Cei

s bii din cmpurile tag i set definesc unul din cele 2

s

blocuri din memoria principal. Figura 6.17

ilustreaz logica de control a memoriei cache n acest caz. Prin mapare complet asociativ cmpul tag n

adresa memoriei este mare i, dup cum s-a precizat, trebuie comparat cu cmpul tag al fiecrei linii din

cache. Prin mapare asociativ pe k seturi, cmpul tag din adresa memoriei rezult mult mai mic i

trebuie comparat doar cu k taguri ale unui singur set.

Figura 6.17 Organizarea memoriei cache asociativ pe seturi

(Miss in Cache)

Tag Set Word

Adresa de memorie

-

-

-

-

-

(Hit in Cache)

Set 0

Set 1

s-d

w

s +w

s-d

-

-

-

-

-

-

s+w

B0

B1

Memoria

principal

Cache

Tag Data

Compar

s

- - -

F

0

F

1

F

k-1

F

k

-

-

F

k+i

F

2k-1

d

Bj

Figura 6.18 prezint un exemplu de mapare asociativ cu 2 linii n fiecare set referit ca mapare

asociativ pe 2 ci sau seturi. Fiecare numr de set de 13 bii identific 2 linii din cache. De asemenea, d

numrul blocului din memoria principal modulo 2

13

. Acesta determin maparea blocurilor n linii de

cache. Deci blocurile 000000, 00A000,, FF1000 din memoria principal vor fi mapate n setul 0 din

cache. Oricare din aceste blocuri poate fi ncrcat n oricare din cele dou linii ale setului. De remarcat c

nu exist 2 care s se mapeze n acelai set din cache dac nu au acelai numar tag. Pentru operaia de

citire, numrul setului din 13 bii este citit pentru a determina care din cele dou linii va fi examinat.

Amndou liniile din cache sunt examinate pentru a vedea care din ele are numrul tag al adresei ce va

fi accesat.

Figura 6.16 Exemplu de mapare asociativ pe 2 seturi.

9 13 2

13579246

Data

0000

0004

7FF8

7FF9

Set+

Word

Tag

000

-

-

-

77777777

11235813

FEDCBA98

12345678

0000

0004

339C

7FFC

02C

-

-

-

11223344

24682468

0000

0004

7FF8

7FFC

1FF

13579246

11235813

FEDCBA98

11223344

12345678

0000

0001

OCE7

1FFE

1FFF

~ ~

~ ~

~

~

~

~

~ ~

~ ~

Tag Data

Line

Number

9 Bits 32 Bits

16-K word Cache

32 Bits

16-Mbyte Main Memory

Main Memory Address =

Tag Set Word

000

001

02C

1FF

001

77777777

24682468

~ ~

~ ~

Tag Data

9 Bits 32 Bits

001

1FF

O memorie intermediar asociativ pe seturi este inerent mai complicat dect o memorie

intermediar cu coresponden direct, deoarece, dei intrarea n memoria intermediar ce trebuie

examinat se poate calcula din adresa de memorie referit. Un set de n intrri n memoria intermediar

trebuie verificate pentru a vedea dac linia cerut este prezent. Totui, experiena arat c memoriile

intermediare cu dou ci i patru ci lucreaz suficient de bine nct aceste circuite suplimentare s-i

merite costul.

n cazul limit v = m, k =1, tehnica de mapare asociativ pe seturi se reduce la maparea direct, iar n

cazul v =1, k =m, aceast tehnica se reduce la tehnica de mapare complet asociativ. Utilizarea a dou

linii pe set (v = m/2, k=2) este organizarea pe seturi cea mai comun (memorie asociativ pe dou ci).

n cazul utilizrii memoriei asociative pe 4 ci (v = m/4, k =4) mbuntirea fa de cazul precedent este

modest n comparaie cu costurile. Creterea n continuare a numrului de seturi are un efect minor.

6.7. Organizarea memoriei cache la Pentium II

Figura 6.17 prezint elementele eseniale ale memoriri cache L1. Memoria cache L1 este mprit.

Cache L1 pentru instruciuni este plasat intern ntre Fetch and Decode Unit i Bus Interface Unit, iar

cache L1 de date se afl plasat ntre Dispatch and Execute Unit i Retire Unit, pe de o parte, i Bus

Interface Unit. La Bus Interface Unit este conectat i memoria cache L2.

Datele n memoria cache de date L1 constau din 128 de seturi de dou linii fiecare. Aceasta este o

organizare logic de memorie asociativ pe 2 ci, fiecare cale avnd 4Kbytes.Asocierea cu fiecare linie se

face printr-un tag i 2 bii de stare. Aceasta este o organizare logic n dou directoare, astfel nc exist

o intrare n director pentru fiecare linie din cache. Cmpul tag este format din cei mai semnificativi 24 de

bii ai adresei de memorie a datei nceputului de bloc stocat n linia respectiv. Controlerul de cache

utilizeaz algoritmul de nlocuire least recently used (LRU), astfel nct un singur bit LRU este asociat cu

fiecare set format din dou linii.

Memoria cache de date L1 utilizeaz o politic de scriere write-back; data este scris n memoria

principal doar cnd este ndeprtat din cache i doar dac a avut loc o actualizare a datelor n cache.

Procesorul Pentium II poate fi configurat dinamic s suporte i o politic de scriere write-through.

Fig. 6.17. Structura memoriei cache de date la Pentium II

Consistena cache-ului

Pentru a asigura consistena, cache-ul de date suport un protocol cunoscut ca MESI

(modified/exclusive/shared/invalid). MESI este proiectat s suporte cerinele de consisten a cache-ului

n sisteme multiprocesor, dar este util i n sisteme monoprocesor cum este Pentium II.

Datele din cache includ 2 bii de stare per tag, astfel nct fiecare linie poate fi n una din urmtoarele

4 stri:

- Modified linia din cache a fost modificat, este diferit de cea din memoria principal i este

disponibil numai n cache;

- Exclusive linia din cache este identic cu cea din memoria principal i nu este prezent n nici

un alt cache;

- Share - linia din cache este identic cu cea din memoria principal i poate fi prezent i ntr-un

alt cache;

- Invalid - linia din cache nu conine date valide.

Controlul cache-ului

Memoria cache este controlat de doi bii ntr-unul din registrele de

Directoare

LRU Dir 0 Dir 1

4 kbytes

Way 0

Bank 0 Bank 1

32 Bits

4 kbytes

Way 1

Bank 0 Bank 1

32 Bits

Entry 0

Entry 127

Adresa fizic din memoria principal =

page(tag),25-bit, 1of 32 M line (1 of 64) start byte

35 11 10 5 4 0

control, unul numit CD (cache disable), cellalt numit NW ( not write-through). Efectul lor rezult din

Tabelul 6.1.

Control Bits Operating Mode

CD NW Cache Fils Write Throughs Invalidates

0

1

1

0

0

1

Enabled

Disabled

Disabled

Enabled

Enabled

Disabled

Enabled

Enabled

Disabled

Tabelul 6.1. Modurile de operare ale memoriei cache la Pentium II

Exist de asemenea dou instruciuni care pot fi folosite pentru controlul memoriei cache: INVD

invalideaz memoria cache intern i semnalele ctre memoria cache extern i WBINVD scrie napoi i

invalideaz memoria cache intern, apoi scrie napoi i invalideaz memoria cache extern.

7.2. Organizarea i adresarea datelor

Combinaia ntre controlerul HD i soft-ul care l echipeaz determin modul n care

sunt aezate datele pe disc.

Am vzut c discul este divizat n cilindri i piste. Fiecare pist este divizat la rndul

ei n arcuri de cerc numite sectoare, sectorul fiind unitatea de stocare de baz a HD-ului.

Unele sisteme de operare folosesc sectorul ca unitate de baz (de exemplu High

Performance File System al lui OS/2). DOS-ul ns unete mai multe sectoare pentru a

forma unitatea de baz cluster-ul. Sectoarele pot fi marcate soft sau hard. In industria

HD-urilor dimensiunea unui sector este prin convenie 512 bytes. Numrul de sectoare de

pe o pist depinde de construcia discului.

Majoritatea HD-urilor utilizeaz nregistrarea prin zone multiple care permite

existena unui numr variabil de sectoare pe o pist. Un disc cu numr fix de sectoare pe o

pist stocheaz date la densiti mai sczute pe pistele exterioare ale discului dect n cele

dinspre centru, cele mai apropiate de axul discului stocnd datele la cea mai mare densitate

permis de mediul magnetic.

nregistrarea prin zone multiple (MZR Multiple Recording Zone) permite discului s

menin o densitate de nregistrare relativ constant. Drive-urile MZR trebuie s-i

mascheze caracterisricile fizice astfel nct s par c au formate standard piste a cte 17

sectoare, sectoare de cte 512 bytes de date. DOS nu poate opera cu discuri ce i modific

numrul de sectoare de pe o pist: de la 17 la 23, de la 23 la 31.

Nici pistele, nici sectoarele nu sunt marcate fizic pe suprafaa platanelor. Ele sunt

definite magnetic prin intermediul unor abloane bit (informaii de amplasare) codificate,

nregistrate pe disc. Procesul prin care sectoarele sunt definite pe disc se numete

formatare la nivel sczut deoarece are loc la un nivel de control sub cel care opereaz

comenzile DOS normale.

n definirea pistelor exist trei metode:

- prin numrarea lor pist cu pist, operaie ce se realizeaz de ctre mecanismul de

acionare a capetelor,

- prin servo-date permanent nregistrate pe piste, n servo-suprafee speciale,

- prin servo-date ncorporate.

n HD-urile clasice, bii ablon speciali de pe disc servesc drept identificatori. abloanele indic

nceputul sectorului i conin un numr de identificare (ID) care codific sectorul i pista. ID-ul

precede fiecare sector, iar datele pentru corectarea erorilor se afl la sfritul sectorului. La o

operaie normal, servo-sistemul caut o anumit pist, apoi drive-ul citete ID-urile pn gsete

sectorul solicitat. ID-ul de sector poate s consume o parte semnificativ din spaiul disponibil pe

fiecare pist, aa c productorii au cutat modaliti s-l elimine. IBM a dezvoltat un format care

elimin ID-ul prin introducerea unei hri de format n RAM. Harta specific unde este localizat

fiecare sector de pe fiecare pist i care sectoare au fost marcate ca fiind defecte.

Adresarea

HD-urile sunt dispozitive cu acces aleator, dar accesul aleator este la nivel de sector, nu la nivel

de byte. HDD-ul localizeaz i identific fiecare sector cu ajutorul poziiei cilindrului, unde mut

capul, al numrului corepunztor capului i al numrului sectorului n cadrul pistei. Aceste trei

valori cilindru, cap, sector furnizeaz adresa fizic a fiecrui sector de pe disc.

CHS

HD-urile mai vechi necesitau ca sistemul de operare s identifice fiecare sector prin adresa sa fizic

exact. Cele trei valori pentru cilindru, cap i sector au dat numele de adresare CHS (Cylinder-Head-

Sector). Adresarea fizic conferea sistemului de operare stabilitate i posibilitatea de acces direct la

HDD. Dac un sector este defect, sistemul de operare are rspunderea s nu permit folosirea lui.

Sistemul a devenit depit odat cu creterea capacitii discurilor (acest sistem permitea existea a

doar 1024 de cilindri, ceea ce nsemna spaii de adresare CHS de pn la 80-120 MB).

Translatarea sectoarelor

Principala strategie folosit de productori pentru a depi limita de 1024 cilindri

impus de adresarea CHS a fost translatarea sectoarelor. Partea electronic a HD-ului

translateaz valorile CHS, trimise de sistemul de operare, n diferite valori pe care le

folosete pentru adresarea fizic a sectoarelor. Dei un PC trimite valori CHS rmnnd

astfel compatibil cu hardware-ul i software-ul convenional - acestea nu corespund direct

sectoarelor de pe disc. Translatarea sectoarelor permite unui drive de pe disc s par c are

o aranjare a cilindrilor, pistelor i sectoarelor diferit de cea real.

Adresarea n blocuri logice

O dat ce un HD are suficient inteligen pentru a traduce adresarea CHS, nu mai

este nevoie s fie urmat convenia CHS la trimiterea adreselor ctre un disk drive. Drive-

ul poate transforma orice valoare n adres fizic CHS a sectoarelor individuale. Cea mai

popular metod de adresare de pe HD este acum adresarea n blocuri logice (LBA

Logical Block Adressing). n LBA fiecare sector este numerotat, de la primul la ultimul.

Pentru a adresa un sector, UC trimite un numr de sector pe care drive-ul l transform n

adresa fizic CHS pentru a accesa datele solicitate. Adresarea LBA are o flexibilitate mai

mare dect adresarea CHS. LBA poate fi utilizat pentru a adresa i alte dispozitive hard

dect HD. Orice dispozitiv care fragmenteaz datele n blocuri, care pot fi practic de orice

mrime, poate utiliza LBA.

7.3. Detalii de funcionare

7.3.1. Sincronizarea ceasului de citire/scriere

Odat ce capetele de citire/scriere sunt poziionate corect pe cilindrul corespunztor,

urmtoarea operaie este ajustarea ceasului de citire/scriere pentru sincronizarea acestuia

cu rata datelor de pe disc. n acest caz nu exist ns mecanism servo, toate operaiile fiind

efectuate electronic.

Atunci cnd nu exist tranziii de flux pe o anumit distan, delimitarea biilor se

realizeaz prin msurarea timpului. Exist un sistem de eantionare care detecteaz o

tensiune datorit schimbrilor de polaritate ale fluxului, d/dt. Dac n fereastra de timp

corespunztoare unui bit are loc o schimbare, bitul este 1, n caz contrar bitul fiind 0.

Aceste semnale sunt ilustrate n Figura 7.1, mpreun cu ceasul care indic momentele n

care trebuie eantionat d/dt. n exemplul prezentat, ceasul are frecvena corespunztoare

ratei biilor, momentul eantionrii fiind frontul cresctor al ceasului. Sistemul testeaz

dac amplitudinea tensiunii detectate este mai mare dect un anumit prag n momentul

eantionrii. Prin introducerea acestui prag se obine o margine fa de zgomotele

inevitabile provenite de la diferite surse. n Figura 7.1 irul de bii detectat este

1001 0100 0101 0001 0100 0001 0010 0001.

Figura 7.1. Semnalul de tensiune (v) detectat de capul de citire

i semnalul de ceas reconstruit din irul de bii.

n figura 7.1 ceasul este sincronizat corect cu irul de bii. Pentru asigurarea

sincronizrii o posibilitate ar fi prenregistrarea informaiilor de ceas. Nu se procedeaz aa

deoarece canalele de sincronizare ar ocupa spaiu pe disc. Semnalul de ceas este generat cu

ajutorul unui oscilator controlat n tensiune care utilizeaz chiar irul de bii ca un semnal

de comparaie n ceea ce reprezint un sistem servo electronic, i anume bucla cu calare de

faz (PLL - Phase-Locked Loop). PLL compar diferena de timp, At, dintre frontul

cresctor al ceasului i vrful tensiunii induse, comandnd apoi oscilatorul pentru a reduce

aceast diferen. Prin reducerea tensiunii care controleaz oscilatorul frecvena acestuia

va scade, iar prin creterea tensiunii frecvena va crete. Prin utilizarea acestui control,

eroarea de faz i de frecven poate fi redus n mod semnificativ. PLL nu poate asigura

sincronizarea dect pe o perioad scurt de timp, fiind necesare tranziii relativ frecvente

ale fluxului, asigurate de o metod de codificare adecvat.

ir de bii

0,1 m

2m

C

a

p

Bra

Ceas

dt

d

v

|

=

Figura 7.2. Codificarea i decodificarea

datelor transferate pe disc i citite de pe disc

Figura 7.2. indic etapele prin care trec datele iniiale n cursul transferului lor pe disc

i de pe disc. Pentru corectarea erorilor de scriere i de citire care pot apare, datelor li se

adaug coduri corectoare de erori (ECC - Error Correction Code). Se adaug att coduri

ECC lungi (Reed-Solomon) ct i scurte. Dac la o citire se detecteaz o eroare i aceasta nu

poate fi corectat printr-un cod ECC simplu, local, se efectueaz un numr de ncercri

pentru recitirea datelor. Dac nu se poate efectua o citire fr erori, se utilizeaz codul ECC

lung pentru a ncerca corectarea erorii.

7.3.2. Detectarea biilor

Determinarea valorii bitului dintr-o fereastr de timp necesit circuite electronice

complexe. Semnalul va conine zgomote de la canalul nsui, de la canalele adiacente i de

la circuitele electronice. Pentru a avea o anumit imunitate la zgomote i a se putea lua o

decizie asupra valorii bitului, semnalul de intrare este filtrat, i se detecteaz valoarea

maxim, i n final este difereniat. Dac nu este detectat un vrf cu o amplitudine

suficient, bitul are valoarea 0. Dac valoarea de vrf este deasupra valorii de prag, este

detectat poziia trecerii prin zero a semnalului difereniat. Bitul din fereastra n care se

detecteaz trecerea prin zero va avea valoarea 1.

Prelucrarea semnalelor este prezentat n figurile 7.3 i 7.4. O tranziie de flux, fr

zgomote, provine direct de la semnalul de la capul de citire. Acest semnal este trecut printr-

un filtru trece jos care elimin o mare parte din zgomote, dar lrgete de asemenea

Date

utilizator

Adugare

ECC

Codificare

RLL

D

i

s

c

Eliminare

ECC

Decodificare

RLL

Date

utilizator

impusul. Impulsul este apoi redresat pentru ca att tranziiile pozitive ct i cele negative

s fie reprezentate ca pozitive. Dac impulsul rezultat depete pragul de detecie, rezult

c bitul detectat este 1 logic.

Figura 7.3. Diferitele semnale utilizate pentru citirea datelor de pe disc

Figura 7.4. Prelucrarea semnalelor implicate n translatarea semnalului

d/dt ntr-un ir de bii 1 i 0.

Impulsul filtrat este apoi difereniat i trecerea prin zero a semnalului este utilizat pentru a

determina momentul apariiei impulsului. Exist o anumit imprecizie n determinarea momentului

trecerii prin zero. De asemenea, exist o anumit probabilitate de a atribui valoarea 1 sau 0 unei

poziii eronate. Codul RLL trebuie construit astfel nct o astfel de eroare s nu se propage prea

Filtrare i

redresare

dt

d

dt

d|

Prag de

detecie

Trecere

prin zero

Semnal

analogic

Egalizor

Difereniere

amplitudine

dt

d

PLL

Detector

de trecere

prin zero

1 sau 0

departe. Aceast propagare poate apare deoarece interpretarea bitului succesor depinde n mare

parte de interpretarea predecesorului acestuia. Dac propagarea erorii este redus, codul ECC va

permite reconstruirea biilor care nu au fost determinai n mod corect.

7.4.1.1. Metoda FM

Aceast metod de modulaie n frecven este numit i nregistrarea n simpl

densitate (Single Density). Este una din cele mai simple metode de codificare a

informaiilor, fiind utilizat la primele uniti de discuri flexibile utilizate de calculatoarele

personale. Metoda nu mai este folosit n prezent.

n fiecare celul de bit se nregistreaz o tranziie de flux pentru un bit egal cu 1, sau

nu se nregistreaz nici o tranziie pentru un bit egal cu 0. Datele sunt nscrise mpreun

cu un semnal de ceas pentru a pstra sincronizarea ntre controler i unitatea de disc, mai

ales n cazul citirii unei serii lungi de zerouri, cnd nu apare nici o tranziie pe o perioad

mai lung.

Pentru fiecare bit sunt necesare dou celule de tranziii. Un bit de 1 este nregistrat ca

o tranziie de flux de ceas, urmat de o tranziie de flux de date, care apar din punctul de

vedere al unitii ca dou tranziii de flux consecutive. Pentru un bit de 0, numai celula de

ceas conine tranziie de flux. Pentru ambele cazuri, tranziia de flux iniial reprezint

semnalul de ceas, iar a doua celul de bit conine o tranziie numai dac bitul nregistrat

este un bit de 1. Tabelul 7.1 prezint codificarea prin aceast metod, unde:

T - indic existena unei tranziii de flux;

N - indic lipsa unei tranziii de flux.

Bit de informaie Codificarea n tranziii de

flux

1 TT

0 TN

Tabelul 7.1. Metoda de codificare FM

Folosind aceast metod, un octet de zerouri se codific prin

"TNTNTNTNTNTNTNTN", iar un octet care conine doar bii de 1 se codific prin

"TTTTTTTTTTTTTTTT". Rezult c n cazul irului de bii de 1 frecvena tranziiilor de

flux este dubl comparativ cu frecvena tranziiilor n cazul irului biilor de 0, de unde

numele de modulaie n frecven. Dei metoda este simpl, apare dezavantajul c fiecare

bit de informaie necesit dou tranziii de flux, ceea ce duce la njumtirea capacitii

poteniale a discului.

7.4.2.1. Structura pistelor i a sectoarelor

La formatarea fizic sau de nivel sczut a unui disc fix, se creeaz anumite zone de control care sunt

utilizate pentru numerotarea sectoarelor i identificarea nceputului i sfritului fiecrui sector. Aceste

zone preced i urmeaz dup zona de date a fiecrui sector, existena lor explicnd diferena dintre

capacitatea neformatat i cea formatat a unitii. Zonele de control sunt independente de sistemul de

operare i de sistemul de fiiere. Noile uniti de discuri nu utilizeaz asemenea zone de control, astfel

nct la acestea practic ntregul spaiu de pe disc este utilizat pentru memorarea datelor. Fiecare sector

de pe disc are o zon de prefix, sau antet, care identific nceputul sectorului i conine numrul

sectorului. Urmeaz apoi zona de date, care este iniializat la formatarea fizic cu o anumit valoare, iar

apoi o zon de sufix. Structura exact a acestor zone difer n funcie de tipul unitii de discuri. n mod

tipic, zonele de control corespunztoare unui sector ocup 59 de octei, astfel nct un sector va ocupa

n total 512 + 59 = 571 octei. n continuare se prezint structura simplificat a pistelor i a sectoarelor.

nceputul fiecrei piste este indicat de o marc de index, dup care urmeaz un interval

post-index (Post-Index Gap). Acest interval asigur un anumit timp pentru comutarea ntre

capete, astfel nct la trecerea de la o pist la alta sectoarele consecutive pot fi citite fr a

se atepta o rotaie suplimentar a discului. La cele mai multe uniti acest timp nu este

suficient i de aceea se asigur timp suplimentar prin decalarea sectoarelor aflate pe piste

diferite, astfel nct apariia primului sector s fie ntrziat. Dup intervalul post-index,

urmeaz zonele de control i de date ale sectoarelor. Pentru fiecare sector, zona de prefix

conine identificatorul sectorului. Acest identificator este precedat de un octet de

sincronizare, care este utilizat de controler, i o marc de adres, care indic faptul c

urmeaz identificatorul de sector. Identificatorul este format din cmpuri separate pentru

numrul cilindrului, al capului i al sectorului. Exist de asemenea un cmp de control

ciclic redundant (CRC - Cyclic Redundancy Check) pentru verificarea identificatorului de

sector. Controlerele de disc utilizeaz de obicei bitul 7 al cmpului rezervat pentru numrul

capului n scopul marcrii sectorului ca fiind defect, n timpul formatrii fizice sau al

testrii suprafeei discului. Apoi exist un interval pentru separarea identificatorului de

sector de zona de date a sectorului. Urmeaz un octet de sincronizare, utilizat de controler,

o marc de adres, care indic faptul c urmeaz datele din sector, iar apoi zona de date, de

512 octei.

Zona de sufix care urmeaz poate conine un cmp de doi octei pentru controlul ciclic

redundant (CRC), sau un cmp pentru un cod de corecie a erorilor (ECC - Error Correction

Code), care necesit un numr mai mare de octei. Cmpul ECC poate asigura detecia i

corecia erorilor din zona de date a sectorului. Posibilitile de detecie i de corecie a

erorilor depind de codul ECC utilizat i de implementarea controlerului.

ntre dou sectoare consecutive exist un interval (Inter-Record Gap), prevzut pentru

ajustarea diferenelor de lungime a sectoarelor din cauza variaiilor vitezei de rotaie a

motorului. O pist poate fi formatat n timp ce discul se rotete cu o anumit vitez, i

apoi sectorul poate fi nscris n timp ce discul se rotete cu o vitez puin diferit. Acest

interval previne suprascrierea accidental a informaiilor din sectorul urmtor n astfel de

cazuri. La sfritul fiecrei piste exist un interval pre-index (Pre-Index Gap), care permite

o toleran a vitezei de rotaie a motorului pentru ntreaga pist.

7.6. RAID

n ceea ce privete creterea ratei de transfer n dispozitivele de stocare secundar,

aceasta a crescut mult mai puin dect cea a procesoarelor sau a memoriei. Aceasta a fcut

ca sistemul de stocare pe disc magnetic s se afle n centrul preocuprii pentru

mbuntirea performaei calculatoarelor n ansamblu.

Ca i n alte zone ale sistemului de calcul, atunci cnd vorbim de performana,

proiectanii recunosc c dac una din componente nu mai poate aduce un spor de

performan semnificativ, singura posibilitate de a crete performana este de a aduga

mai multe componente n paralel. Acest concept conduce n cazul discurilor fixe la arii de

discuri ce pot opera independent i n paralel.

Prin utilizarea discurilor multiple, rezult o varietate de modaliti n care datele pot fi

organizate i n care redundana poate fi adugat pentru a crete fiabilitatea.

La baza conceptului de RAID st mprirea datelor pe discuri, fiecare dintre ele stocnd

o cantitate prestabilit (stripe). Discurile sunt, astfel, concatenate i apar pentru sistem ca

un singur disc.

Timpul pn la prima defeciune (MTBF) se poate calcula dup formula:

discuri de numarul

MTBF

MTBF

Disc

RAID

=

Astfel acesta are o valoare prea mic pentru a putea face fa aplicaiilor care necesit

acest gen de configuraie. Datele pot fi stocate redundant pentru a obine un sistem

rezistent la erori.

Alt criteriu care definete o arie RAID este viteza de transfer a datelor. Evident,

comparaia trebuie fcut cu performana unui singur hard disc. Mai muli factori

influeneaz comportamentul ariei, dar este important ca discurile s fie identice. Pentru ca

o operaiune de I/O s fie complet, toate discurile trebuie s acceseze datele

corespunztoare, cel mai lent fiind cel care va stabili timpul necesar, n final, pentru

operaiune (dac discurile sunt cu performane diferite).

Iniial au fost definite 5 nivele de RAID, toate avnd ca scop stocarea redundant i

creterea vitezei. Totui, mprirea datelor pe discuri fr a oferi i sigurana acestora a

fost luat n considerare, fiind una din cele mai rapide metode de stocare.

7.7.1. Nivele RAID

Acest mod a fost denumit RAID 0 (striping) i este cel mai des ntlnit n sistemele

moderne pentru jocuri i multimedia. Nu sunt necesare calcule suplimentare pentru sume

de control, deci pentru dou sau 3 hard discuri Paralel ATA sau Serial ATA transferul este

mai mare de 2, respectiv 3 ori. Dezavantajul este c, dac RAID 0 nu ofer nici un fel de

redundan, n cazul defectrii unui disc datele vor fi pierdute, imposibil de recuperat (sunt

mprite pe toate discurile). Poate fi utilizat i n sisteme destinate produciei i editrii

video, aplicaiile pre-press sau oriunde este necesar un transfer foarte bun, fr ca datele s

fie critice.

Figura 7.8. RAID 0

Primul nivel RAID care ofer redundan este RAID 1 (mirroring), bazat pe scrierea

identic a datelor pe dou sau mai multe discuri, n perechi. Acest mod ofer o redundan

100%, n cazul unei defeciuni, reconstrucia fcndu-se automat. n cazul unui RAID 1 cu

Disc 1

Disc 2 Disc 3 Disc 4

Segment 1

Segment 5

Segment 9

Segment 2

Segment 6

Segment 10

Segment 3

Segment 7

Segment 11

Segment 4

Segment 8

Segment 12

mai multe perechi, sistemul poate susine cderea mai multor drive-uri, cu condiia ca

acestea s se gseasc pe mirror-uri diferite. Viteza de scriere este (teoretic) egal cu viteza

unui singur hard disc, oferind o slab performan. n schimb, viteza de citire este de 2 ori

mai mare, dac avem discurile conectate la un controller care permite operaii simultane pe

mai multe discuri.

Figura 7.9. RAID 1

Disc 1 Disc 2

Segment 1

Segment 2

Segment 3

Segment 4

Segment 1 Duplicated

Segment 2 Duplicated

Segment 3 Duplicated

Segment 4 Duplicated

Ideal ar fi s conectm hard discurile dintr-un mirror la controllere separate, pentru

mrirea redundanei (n eventualitatea unei defeciuni la un controller, RAID-ul rmne

"n picioare"), acest mod fiind denumit "duplexing".

Dei costul per GB este destul de ridicat (capacitatea util este jumtate din cea total),