Documente Academic

Documente Profesional

Documente Cultură

SECR 05 Sinteza de Frecventa

Încărcat de

Anonymus_01Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

SECR 05 Sinteza de Frecventa

Încărcat de

Anonymus_01Drepturi de autor:

Formate disponibile

5.

Sinteza de frecven

5.1 Noiuni generale

Realizarea unor sisteme complexe sintetizoarele de frecven cu ajutorul crora

s se poat genera una sau mai multe frecvene (semnale sinusoidale) pornind de la unul

sau mai multe Oscilatoare de Referin (OR). Uzual acestea din urm sunt oscilatoare cu

cuar.

n preistoria sintezei de frecven aceasta consta din:

- alegea ieirea unui OC din mai multe;

- schimba criteriul care controla frecvena unui oscilator.

Au fost apoi concepute i implementate scheme tot mai complexe urmrind:

- generarea ct mai multor frecvene plecnd de la un numr ct mai mic de

oscilatoare de referin;

- semnalul generat s fie ct mai curat din punct de vedere spectral;

- parametrii semnalelor s se stabilizeze ct mai repede dup pornire sau dup o

eventual schimbare a valorii frecvenei (comutare).

Prin prisma acestor obiective pot fi identificai i principalii parametrii specifici

sintetizoarelor:

- gama de frecven n care pot fi generate semnale sinusoidale;

- pasul (sau distana ntre dou valori succesive ale frecvenei);

- puritatea spectral

componente deprtate

zgomotul de faz

- timpul de stabilire a regimului permanent n urma pornirii echipamentului sau

dup modificarea valorii frecvenei;

Sisteme i Echipamente pentru Comunicatii Radio

innd cont de procedeul folosit pentru prelucrarea semnalului de referin se

poate face o prim clasificare a sintetizoarelor de frecven n sintetizoare care folosesc:

a) procedee directe

b) procedee indirecte

a) Procedeele directe constau din combinarea frecvenelor unor semnale sinusoidale

generate de mai multe oscilatoare de referin (OR) sau ale armonicelor acestora prin

multiplicri, mixri, divizri, filtrri.

Se disting dou variante:

- procedee analogice;

- procedee digitale.

Procedeele analogice care se mai aplic n puine sisteme de RC - au de fcut

fa compromisului:

- pentru a realiza puritate spectral bun sunt necesare filtre trece band ct mai

selective;

- pentru a realiza timp de stabilire a regimului permanent redus sunt necesare

filtre mai puin selective.

Despre procedeele digitale se va discuta n continuare ele reprezentnd o soluie

modern i foarte eficient dac frecvena generat nu este prea mare.

- Procedeele indirecte au la baz folosirea circuitelor PLL;

- Circuitele PLL utilizate n acest context pot fi:

analogice;

digitale.

Sisteme i Echipamente pentru Comunicatii Radio

Semnalul livrat la ieire este semnalul produs ce ctre Oscilatorul Controlat n

Tensiune(OCT), deci se elimin problema produselor de intermodulaie.

O alt clasificare a sintetizoarelor ine cont de aplicaia pentru care se folosesc;

din acest punct de vedere se disting:

- sintetizoare folosite la realizarea unor generatoare de semnal de laborator;

- sintetizoare dedicate unor aplicaii din domeniul comunicaiilor sau din alte

domenii.

Sintetizoarele folosite la realizarea generatoarelor de semnal de laborator sunt

relativ complexe i au o structur modular. Fiecare modul genereaz, la un moment

dat, o frecven avnd o valoare aleas dintr-un set restrns de valori, valoarea

frecvenei semnalului de ieire se obine prin combinarea corespunztoare a valorilor

diverselor module.

Un exemplu, din aceast perspectiv, l constituie sintetizoarele decadice. In acest

caz valoarea frecvenelor se exprim zecimal iar modulele sunt dedicate cte unei

decade, fiecare contribuind n valoare final cu un digit.

Frecvena generat de modulul corespunztor unei decade este notat cu:

f 09 n ,

n [1, N ]

Prin convenie se noteaz cu N decada cu ponderea cea mai mic.

Valoarea frecvenei generate de sintertizor este:

N

f f 09 n 10 n 1

n 1

De exemplu un sintetizor care lucreaz cu pasul de 1kHz n gama 1 kHz 9999

kHz are patru decade. Pentru f0=4972:

Sisteme i Echipamente pentru Comunicatii Radio

f 09 1 4MHz f 09 2 9MHz

f 09 3 7MHz f 09 4 2MHz

Se constat c decadele genereaz valori apropiate deci vor avea condiii de lucru

comparabile. Valoarea frecvenei care va corespunde decadei se obine prin divizare iar

semnalul final se obine prin combinarea corespunztoare a semnalelor provenind de la

cele patru (N) decade.

5.2 Sinteza digital direct

Principalele caracteristici care au fcut ca aceast metod de sintez s fie foarte

mult folosit sunt:

- repetabilitatea

- fiabilitatea

- absena circuitelor de acord

- absena circuitelor care s conduc la deriva valorilor generate funcie de

temperatur sau de timp.

Sintetizoarele analogice conin: Oscilatoare Controlate n Tensiune (OCT),

multiplicatoare, circuite PLL, filtre care necesit acord, circuite de compensare a derivei

cu temperatura, componente selectate prin msurtori etc.

Sintetizoarele digitale necesit circuite logice i un oscilator de tact.

Trebuie, totui, precizat c aceste sintetizoare au oarecari limite din punctul de

vedere al frecvenei maxime pe care o pot genera.

Sisteme i Echipamente pentru Comunicatii Radio

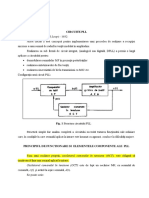

5.2.1 Schema bloc

Oscilator Control numeric (OCN)

Tabel

(memorie)

ROM

Acumulator

de faza

Tact

CDA

FTJ

Date

Acord

Figura 5.2.1 Schema bloc a unui sintetizor digital direct

Pe scurt, principiul de lucru este urmtorul. O perioad a semnalului periodic

care trebuie generat este eantionat cu o frecven de eantionare mare, mult mai

mare dect limita dat de teorema eantionrii. Eantioanele sunt nscrise ntr-o

memorie ROM. Circuitul produce un semnal numeric liniar cresctor n timp care

este folosit pentru a citi eantioanele din memorie. Eantioanele pot fi citite n ordine

sau cu un pas care se poate modifica limita maxim fiind dat de citirea numrului

minim de eantioane care permite refacerea semnalului conform teoremei

eantionrii. n acest fel frecvena semnalului generat depinde de frecvena de tact cu

care se modific semnalul liniar variabil n timp i de pasul cu care se parcurg

adresele memoriei adic de pasul cu care se genereaz semnalul liniar variabil.

Observnd schema bloc dat n figura 5.2.1 se remarc existena a trei blocuri

importante:

- oscilatorul controlat numeric (NCD);

- convertorul Digital-Analog (CDA, DAC);

- filtrul de ieire folosit pentru a suprima componentele de frecvene

superioare.

5

Sisteme i Echipamente pentru Comunicatii Radio

Parametrii de intrare sunt:

frecvena de referin (tactul) care incrementeaz numrtorul i

introduce noua informaie n convertor,

datele de control pentru a specifica valoarea frecvenei i modulaia.

5.2.2. Oscilatorul controlat numeric

Oscilatorul controlat numeric, pe lng logica de interfaare, cuprinde

acumulatorul de faz, care este, de fapt, un numrtor i tabelul (ROM) n care sunt

nscrise eantioanele pentru forma de und care va fi generat.

B1

B2

Acum

(NUM)

Mod.

faza

ROM

Figura 5.2.2 Schema bloc a Oscilatorului Controlat Numeric

n registrul B2 se insereaz un cuvnt care controleaz valoarea frecvenei.

Fiecare impuls de tact incrementeaz numrtorul cu o valoare dat de cuvntul

menionat (pas) notat cu .

Se poate verifica faptul c prin aceast acumulare se realizeaz o cretere liniar a

mrimii de ieire (expresia binar care exprim starea numrtorului la un moment dat)

care controleaz extragerea datelor din memorie; Aceast mrime reprezint faza

semnalului generat; dac valorile memorate sunt eantioanele corespunztor alese ale

unui semnal sinusoidal la ieire rezult un semnal sinusoidal.

6

Sisteme i Echipamente pentru Comunicatii Radio

Observnd atent logica de lucru se poate constata c frecvena creia i

corespunde faza liniar cresctoare depinde de:

frecvena tactului aplicat acumulatorului de faz;

valoarea pasului de faz adic valoarea cuvntului cu care se

incrementeaz numrtorul (acumulatorul de faz);

valoarea maxim pn la care se poate incrementa numrtorul;

O limit a valoarea frecvenei este dat de numrul de pai nainte de resetare.

Se poate verifica faptul c valoarea frecvenei semnalului generat este dat de

expresia:

f out

f t

2m

(5.2.1)

n expresia (5.2.1) m reprezint numrul de bii ai numrtorului (acumulatorul

de faz);

Avnd n vedere c frecvena ft i numrul de bii m sunt mrimi constante

parametrul cu care se poate controla valoarea frecvenei semnalului generat este pasul

.

Liniaritatea variaiei fazei, deci puritatea spectral a semnalului generat, depinde,

n primul rnd, de puritatea spectral a semnalului de tact. La o analiz mai atent se

observ c acest sintetizor este de fapt un divizor de frecven, deci zgomotul de faz al

semnalului generat va fi mai mic dect zgomotul de faz al oscilatorului de tact.

Aa cum s-a menionat mai sus mrimile

ft i m sunt constante pentru un

sintetizor. Valorile acestor mrimi sunt alese funcie de gama de frecven care trebuie

acoperit i de pasul cu care trebuie explorat aceast gam.

Se deduce c:

f max 0,4f t

f

(5.5.2)

ft

pasul (5.5.3)

2m

Sisteme i Echipamente pentru Comunicatii Radio

Prima valoare limit rezult din teorema eantionrii (semnalul de ieire trebuie

eantionat cel puin cu frecven dubl).

Din a doua relaie rezult c este posibil s se realizeze pai foarte mici dac

acumulatorul de faz asigur o rezoluie suficient (m suficient de mare).

O observaie interesant se refer la faptul c din momentul n care acumulatorul

este ncrcat cu un nou pas, faza ncepe s fie determinat de aceast valoare, deci un

astfel de sintetizor poate genera cu uurin semnale modulate n frecven iar procesul

de modulaie n frecven este cu faz continu.

n ncheierea acestei seciuni vom reaminti c faza este convertit n amplitudine

prin citirea unor valori nscrise ntr-o memorie (ROM); adresa va fi dat de cuvntul

binar obinut la ieirea cumulatorului de faz.

5.2.3 Memoria

Din analiza de mai sus rezult c memoria reprezint convertorul faz

amplitudine.

Orice semnal periodic are o coresponden biunivoc ntre amplitudine i faz.

Conversia se poate face simplu prin memorarea eantioanelor amplitudinii semnalului

sinusoidal (sau ale unui semnal cu o lege de variaie oarecare) care trebuie generat.

Rmnnd la semnale sinusoidale se poate afirma c avnd n vedere modul de

variaie al amplitudinii acestui tip de semnale nu este necesar memorarea valorilor

pentru o perioad ntreag ci numai pentru un sfert de perioad figura 5.2.3.

111111

Figura 5.2.3 Eantioanele unui semnal

sinusoidal care trebuie memorate

00000

Adresa

0000

11111

8

Sisteme i Echipamente pentru Comunicatii Radio

Deducerea valorilor pentru celelalte cadrane se poate face simplu prin logica de

control (numrare napoi sau schimbare de semn). Evident va trebui decis dac este mai

important s se fac economie de memorie sau s se simplifice logica de control.

O alt observaie este foarte important: numrtoarele folosite n aceste

sintetizoare lucreaz cu pn al 48 bii pentru a se obine un pas mic. Pentru controlul

celorlalte blocuri se rein numai cei mai semnificativi bii (10-12), rezoluia fiind

suficient. Dac se renun la un numr oarecare de bii dintre cei mai puin

semnificativi nu se modific dect faptul c orice eantion va fi citit pentru un numr

mai mare de impulsuri de tact dect dac ar fi folosii toi biii.

Se mai poate remarca faptul c aceste sintetizoare pot fi, foarte uor, modulate n

faz; n acest scop cuvntul de control care corespunde modulaiei de faz va fi adunat

cu cuvntul de ieire al acumulatorului de faz care este folosit pentru a citi memoria. n

acest mod eantioanele sunt citite mai devreme sau mai trziu.

De asemenea modulaia de amplitudine se poate realiza prin controlul valorii

citite din memorie (aduna, nmuli).

Performanele sintetizoarelor realizate prin metoda digital direct sunt limitate n

primul rnd de viteza cu care se pot prelucra datele de ctre convertoarele digital

analogice (DAC) i de frecvenele limit ale circuitelor logice folosite.

Se pot genera semnale pn la o frecven de tact de aproximativ

1GHz deci

f0400MHz.

Dac se dorete generarea unor frecvene cu valori mai mari se pot combina mai

multe metode de sintez.

Pentru a exemplifica vom considera sintetizorul cu schema bloc dat n figura

5.2.4. Aceasta schem corespunde unui sintetizor n gama de 150..152 MHz cu o

rezoluie de 1 Hz, timp de stabilizare 1 microsecund, componente nedorite sub -65

dBc;

Sisteme i Echipamente pentru Comunicatii Radio

Figura 5.2.4 Sintetizor bazat pe metoda digital direct lucrnd n gama 150-152 MHz

5.2.5Concluzii:

Sintetiznd se pot remarca urmtoarele aspecte specifice pentru sintetizoarele DDS:

au rezoluie fin sau foarte fin (< 1 Hz) ;

au timp de stabilizare a regimului de lucru mic (sub 1s);

pot genera semnale peste mai multe octave;

modificarea frecvenei este realizat cu faz continu;

pot realiza modulaie analogic/de date cu o foarte bun liniaritate (tipic 16 bii);

pot genera semnale defazate, n cuadratur, peste mai multe octave.

Cu privire la puritatea spectral se poate constata c zgomotul de faz nu reprezint

o problem avnd n vedere comportarea ca un divizor de frecven; n schimb apar

componente parazite datorate zgomotului de cuantizare i imperfeciunii convertoarelor.

Locul, n spectru, unde apar aceste componente este predictibil dar nu i amplitudinea

acestora;

Dintre aplicaiile n care pot fi utilizate pot fi menionate:

realizarea unor echipamentele radio cu spectru mprtiat (DS sau FH);

10

Sisteme i Echipamente pentru Comunicatii Radio

producerea semnalelor cu modulaie numeric de frecven (FSK) sau de faz

(PSK) de vitez mare sau cu rezoluie fin;

realizarea radarelor Doppler;

realizarea echipamentelor de radiodifuziune sau radioteleviziune (DAB, DVB,

HDTV);

realizarea echipamentelor pentru explorare prin rezonan magnetic;

realizarea unor echipamente de msur i control de laborator.

11

Sisteme i Echipamente pentru Comunicatii Radio

5.3 Sinteza de frecven realizat cu circuite PLL

5.3.1 Sintetizoare de frecven realizate cu circuite PLL analogice

Dup modul n care se combin semnalele generate de cele N decade:

a) sintetizoare cu injecie serie;

b) sintetizoare cu injecie paralel.

a) Funcionarea sintetizoarelor cu injecie serie

Fig. 5.3.1 Sinteza de frecven prin "injecie" serie;

de la semnalul generat de OR de mare stabilitate se alege un set de 10 componente,

s1 (t) = An cos[(io + ( 09) )t ]

9

(5.3.1)

n=0

unde io corespunde frecvenei care este generat la selectarea valorii (o)1.

s2(t) este un semnal de corecie

s2 (t) = A cos(

Structura unei decade (excepie decada N)

12

io t)

10

(5.3.1)

Sisteme i Echipamente pentru Comunicatii Radio

Fig. 5.3.2 Sinteza de frecven prin injecie serie. Schema bloc a decadei n(nn').

Se obine un semnal avnd frecvena:

f

= f io +

o,n

f o,n+1

+ ( f o-9 )n

10

Prin mixarea cu semnalul s2(t) se va elimina

(5.3.2)

f io

.

10

Rezult:

f o,N = f io + ( f 0 -9 )N

f o,N -1 = f io + ( f 0 -9 )N -1 +

( f 0 - 9 )N

10

...............................

f o,3 = f io + ( f 0-9 )3 +

f o,2 = f io + ( f 0-9 )2 +

( f 0 -9 ) 4

10

( f o-9 )3

+ ... +

( f 0 -9 ) N

N-3

10

( f o-9 ) N

(5.3.3)

+ ... +

N-2

10

10

( f o-9 ) N

( f o-9 )2

+ ... +

f o,1 = f o = f io + ( f 0-9 )1 +

N-1

10

10

Concluzie: aceste sintetizoare sunt uor de adaptat pentru a genera un numr foarte

mare de frecvene.

13

Sisteme i Echipamente pentru Comunicatii Radio

b) Funcionarea sintetizoarelor cu injecie paralel

OR - semnalul de referin propriu-zis:

Fig. 5.3.3 Sintetizor de frecven cu "injecie" paralel;

Semnalele de intrare sunt semnalul de referin

s2 (t) = U r cos n r t

(5.3.4)

i semnalele aplicate celor N decade (cte zece componente) care pot fi diferite:

k2

s1(t) =

Ak cos(k r t) + r(t)

k=k 1

unde r(t) reprezint suma celorlalte componente.

14

(5.3.5)

Sisteme i Echipamente pentru Comunicatii Radio

Fig. 5.3.4 Sinteza de frecven prin "injecie" paralel; schemele bloc pentru:

a) decada n; b) generatorul de digit n.

Semnalul livrat de primul generator de digit este mixat prin scdere fr divizare cu

semnalul de la ieirea OCT; deci, dac este ndeplinit condiia

f o > f i1 + ( f 0 - 9 )1

(5.3.6)

n care, ca i n relaiile urmtoare, fin, n= 0,..N, reprezint frecvena generat la alegerea

valorii (fo)n, rezult un semnal cu frecvena

f o1 = f o - [ f i1 + ( f 0-9 )1 ] ;

(5.3.8)

Dup mixerul asociat celei de a doua decade rezult:

f o,2 = f o,1 - [f i 2 +

( f 0-9 )2

( f 0-9 )2

], f o,1 > f i 2 +

10

10

(5.3.9)

Respectiv

f o = f o,2 + f i1 + f i 2 + ( f 0-9 )1 +

15

( f 0-9 )2

10

(5.3.10)

Sisteme i Echipamente pentru Comunicatii Radio

In final, la sincronism, rezult:

f r = f o,N -1 - [ f iN +

( f 0-9 )N

10

N -1

] ; f o,N -1 > f iN +

( f 0-9 )N

10

(5.3.11)

N -1

i se deduce:

f o = (f i1 + f i2 + f i3 + ... + f iN + f r ) +

( f 0 -9 ) N

( f 0 -9 ) 2

+ [( f 0-9 )1 +

+ ... +

]

N -1

10

10

(5.3.12)

Frecvenele fi1,fi2...fr, vor fi alese n aa fel nct s permit sinteza limitei inferioare a

gamei de frecven impus.

Pentru a ilustra modul cum se aplic relaiile (5.3.9)-(5.3.12) se presupune c trebuie

sintetizate frecvene n gama (200-209,99)MHz cu pasul de 10 kHz. Evident, sunt

necesare 3 decade; cunoscnd pasul se determin:

( f 1 )N

( f 1 )3

= 10 kHz

2

10

adica

f 1 = 1 M Hz si f r = 1 MHz

10

N -1

(5.3.13)

Deci, se va folosi un oscilator cu cuar cu frecvena de 1 MHz i se vor selecta 10

armonici astfel nct s se poat genera:

( f o )1 = 0; ( f 1 )1 = 1 MHz; ( f 2 )1 = 2 MHz...( f 9 )1 = 9 MHz. (5.3.14)

Pentru a preciza armonicele care trebuie utilizate se ine cont c

f omin = f i1 + f i2 + f i3 + f r

(5.3.15)

In scopul unei exprimri zecimale convenabile se aleg cele zece armonici pentru digiii

2 i 3 n domeniul:

f[100,..,109] MHz;

deci, tinnd cont de coeficienii de divizare corespunztori, rezult:

f2=10 MHz i f1=1 MHz

16

Sisteme i Echipamente pentru Comunicatii Radio

respectiv

fi1=188 MHz

deci decada 1 selecteaz una dintre armonicele avnd k[188,..,197].

Se testeaz acoperirea gamei impuse:

( f 0-9 )2 ( f 0-9 )3

+

=

2

10

10

= 188 + 10 + 1 + 1 + 9 + 0,9 + 0,09 = 209,99MHz

f omax = f i1 + f i2 + f i3 + f r + ( f 0-9 )1 +

Lund n consideraie generarea unui semnal cu frecvena fo=203,65 rezult

- (f3)1=3MHz ; fi1+(f3)1=191MHz

- (f6)2=6MHz ; [fi2+(f6)2]:10=10,6MHz

- (f5)3=5MHz ; [fi3+(f5)3]:100=1,05MHz

Se constat c sinteza prin injecie paralel implic o serie ntreag de mixri care au

loc n interiorul buclei; aceste operaii au efecte negative asupra stabilitii.

Au fost imaginate soluii cum ar fi: realizarea unor mixri n afara buclei; divizorul de

frecven plasat naintea generatorului de digit etc. care urmreau ameliorarea

parametrilor buclei din acest punct de vedere. Oricum, sinteza prin injecie paralel nu

este indicat atunci cnd numrul de frecvene care trebuie sintetizate este foarte

mare.

17

Sisteme i Echipamente pentru Comunicatii Radio

5.3.2 Sinteza cu circuite PLL digitale (DPLL)

5.3.2.1 Aspecte specifice DPLL

Pentru a evidenia diferenele existente ntre circuitele PLL digitale i analogice se

va pleca de schemele bloc corespunztoare (figura 5.3.5). Circuitele PLL analogice su

fost studiate la disciplina Comunicaii Analogice i Digitale.

CP

CP

OCT

FTJ

DP

OCT

FTJ

a)

b)

Figura 5.3.5 Schemele bloc pentru circuite PLL i DPLL

ntre cele dou variante se pot evidenia o serie de diferene:

Schema bloc PLL i DPLL

a) de natur constructiv;

b) de natur funcional;

c) din punctul de vedere al performanelor.

a) Diferene de natur constructiv:

- semnalele prelucrate la circuitele DPLL sunt semnale logice;

- Blocul specific DPLL este detectorul de faz care este digital;

- n bucl este introdus un divizor programabil.

Detectorul de faz

- Varianta analogic este realizat cu un Operator de Produs i realizeaz o

caracteristic de detecie a erorilor de faz sinusoidal;

18

Sisteme i Echipamente pentru Comunicatii Radio

u e (t ) k sin 2 1 k sin e (t )

- Realizarea unor DP cu alte performane este uor de realizat n tehnic

digital;

- Astfel de detectoare pot fi folosite i n structura circuitelor PLL analogice dar

numai dac se adug circuite de limitare.

Schema bloc simplificat a circuitelor PLL digitale (figura 5.3.5) evideniaz i o alt

deosebire constructiv fa de circuitele PLL analogice: folosirea divizorului de

frecven (programabil) n bucl, pe calea de reacie;

- Un astfel de divizor extinde n mod considerabil aria de aplicabilitate a

circuitelor DPLL.

- Este interesant de menionat c, la fel ca n cazul detectoarelor de faz, i un

asemenea divizor poate fi introdus n schema circuitelor PLL analogice dac

este precedat de un limitator i urmat de un filtru;

- Evident, n acest caz, soluia este complicat i restrnge gama de frecven

n care circuitul rezultat funcioneaz.

b. Diferenele n ceea ce privete funcionarea sunt, practic, consecine ale

diferenelor menionate mai sus.

De exemplu, un circuit PLL cu un comparator de faz sinusoidal, aflat n

faza de cutare a sincronismului (achiziie), se comport n mod diferit faa

de unul cu caracteristic triunghiular.

Diferena menionat se diminueaz pe msur ce circuitul PLL se apropie de

sincronism; la erori de faz mai mici toate comparatoarele prezint o regiune

liniar.

19

Sisteme i Echipamente pentru Comunicatii Radio

Conform celor menionate mai sus comparatoarele de faz digitale pot fi

utilizate i n structura circuitelor PLL analogice dac, aa cum se preciza mai

sus, sunt precedate de limitatoare, deci acest aspect nu este specific circuitelor

DPLL.

Cu aceste considerente s-a ajuns la concluzia c pentru circuitele DPLL este

valabil schema bloc liniarizat dat n figura 5.3.6-b.

a.

b.

Figura 5.3.6 Schema bloc liniarizat a unui circuit PLL: a. analogic, b. digital

20

Sisteme i Echipamente pentru Comunicatii Radio

Comparnd cele dou scheme echivalente se constat c pe calea de reacie exist un

atenuator cu factorul 1/N care provine de la divizorul programabil.

Dac se analizeaz bucla considernd tandemul oscilator controlat n tensiune

divizor programabil ca un oscilator echivalent caracterizat prin constanta

K'3=K3/N se obin funciile de transfer:

-

pe bucl deschis

G(s) =

K 1 K 2 K 3 F(s)

F(s)

r (s)

= K

|BD =

N

s

s

i (s)

(5.3.16)

unde s-a folosit notaia K'=K1K2K3/N;

- pe bucl nchis

F(s)

r (s)

K

H(s) =

|BI =

s + K F(s)

i (s)

(5.3.17)

Funciile obinute sunt identice, ca form, cu funciile corespunztoare deduse

pentru circuitele analogice. Deosebirea dintre ele const n aceea c, la circuitele PLL

digitale, ctigul K' depinde de frecvena de lucru a OCT prin intermediul factorului de

divizare N.

In cele mai multe situaii, de exemplu n sinteza de frecven, ieirea buclei este

ieirea OCT. In acest caz, funcia de transfer pe bucl deschis rmne ca mai sus iar

funcia pe bucl nchis, de la intrare la ieire, capt expresia

N K F(s)

o (s)

H(s) =

| =

i (s) BI s + K F(s)

(5.3.18)

In concluzie, trebuie s se aib n vedere faptul c la aceste circuite comparatorul

analizeaz semnale a cror frecven este de N ori mai mic dect frecvena OCT. Ca

urmare componentele nefiltrate rezultate n cursul operaiei de comparare de faz, pot

modula OCT. Din acest motiv se impune condiia ca frecven de tiere a filtrului trece

jos din bucl s fie mult mai mic dect frecvena la care lucreaz comparatorul de faz.

21

Sisteme i Echipamente pentru Comunicatii Radio

5.3.2.2

Comparatoare de faz folosite la realizarea circuitelor DPLL

Echivalentul digital al comparatorului de faz analogic de tip operator de produs

este realizat cu un circuit sau-exclusiv. Un asemenea comparator prezint o caracteristic

triunghiular. Soluia, dei foarte economic, nu este folosit, prea mult, deoarece

semnalul proportional cu eroarea de faz are forma unor impulsuri dreptunghiulare

periodice, cu amplitudine mare.

Acest semnal depinde de factorul de umplere al semnalelor comparate i alturi de

componenta medie, folosit pentru controlul OCT, conine componente nedorite care nu

pot fi eliminate, n condiii satisfctoare, de ctre filtrul de bucl al circuitului DPLL.

Dintre nenumratele comparatoare de faz digitale perfecionate existente, a fost

ales pentru a fi prezentat, n acest paragraf, comparatorul a crui schem este dat n figura

5.3.7 i care este folosit n unele circuite PLL realizate n tehnologie CMOS ;

Fig. 5.3.7 Comparator de faz digital

Se observ c este un comparator de faz cu memorie, controlat de fronturile

cresctoare ale semnalelor de intrare. El este realizat cu patru bistabili RS, logica de

control asociat i doi tranzistori MOS, unul cu canal p i cellalt cu canal n, conectai pe

post de comutatoare pe ieire.

22

Sisteme i Echipamente pentru Comunicatii Radio

Cei doi tranzistori pot fi:

unul n stare de conducie i cellalt n stare de blocare;

amndoi n stare de blocare (ieirea n stare de impedan mare).

Cnd tranzistorul cu canal p este n conducie condensatorul de filtrare C se ncarc

prin rezistena R; cnd conduce tranzistorul cu canal n, condensatorul, C, se descarc cu

aceeasi constant de timp; cnd ambele sunt n stare de blocare tensiunea pe condensator

rmne constant.

Presupunnd c semnalul sv are frecvena mai mare dect sr atunci, n cea mai mare

parte a timpului, este deschis tranzistorul cu canal p i condensatorul se ncarc. Dac

frecvenele au devenit egale dar exist un defazaj ntre cele dou semnale se deschide unul

din cei doi tranzistori, funcie de semnul defazajului, pe o durat proporional cu valoarea

absolut a defazajului. Deci, pe msur ce circuitul PLL se apropie de condiia de

sincronism, care n acest caz se exprim prin frecvene egale i defazaj nul, impulsurile

aplicate condensatorului sunt tot mai scurte. In acest mod la sincronism componentele care

trebuie filtrate au o pondere redus n semnalul de ieire. Funcionarea este similar dac

relaia ntre frecvenele semnalelor comparate este invers.

Pentru circuitele PLL folosite n sinteza de frecven, cu aplicaie n sistemele de

comunicaie, se cere, adeseori, o puritate spectral mai bun dect cea care poate fi

realizat cu comparatorul de faz descris. Pentru asemenea situaii au fost concepute

comparatoare de faz cu eantionare i memorare (S&H).

Schema unui astfel de comparator este dat n figura 5.3.8. Se constat c schema

dat poate fi mprit n trei seciuni:

blocul digital de control, care formeaz semnalul ntrziat sv' i care genereaz

semnalele de comand pentru ntreruptoare;

comparatorul analogic;

23

Sisteme i Echipamente pentru Comunicatii Radio

blocul care sesizeaz ieirea comparatorului din zona de funcionare corect i o

semnalizeaz.

Fig. 5.3.8 Schema simplificat a unui comparator analogic S&H.

Funcionarea comparatorului de faz S&H poate fi urmrit cu ajutorul diagramelor

date n figura 5.3.9-a. Semnalele analizate sunt sv i sr.

Fig. 5.3.9 Comparatorul analogic S&H; a) formele de und ale principalelor

semnale, b) variaia tensiunii de ieire funcie de eroarea de faz.

24

Sisteme i Echipamente pentru Comunicatii Radio

Blocul logic de control genereaz semnalul sv' printr-o ntrziere a semnalului t a

semnalului sv (vezi i figura 5.3.13). Frontul scztor al semnalului sv' (sau frontul

cresctor al semnalului sv) comand nchiderea comutatorului k2, producnd descrcarea

condensatorului CA. Frontul pozitiv deschide comutatorul k2 i nchide comutatorul k1.

Condensatorul CA se ncarc, sub curent constant, pn la apariia frontului cresctor al

semnalului sr.

In acest mod tensiunea UCA este proporional cu defazajul existent ntre cele dou

semnale. Frontul cresctor a semnalului sr deschide comutatorul k1, nchide comutatorul k3

i tensiunea UCA se transfer pe condensatorul de memorare CC.

Din cele prezentate rezult c tensiunea de comand variaz n trepte mici; deci

componentele nedorite sunt mult reduse n comparaie cu comparatoarele digitale. De

asemenea se constat c panta comparatorului depinde de condensatorul CA i de rezistena

care controleaz generatorul de curent.

Valoarea pantei poate fi foarte mare, rezultnd o caracteristic trapezoidal (figura

5.3.9-b). Dac eroarea de faz este prea mare, tensiunea pe condensatorul CA depete

tensiunea VEOR (EOR de la End Of Ramp = sfrit de ramp) comparatorul realizat cu

amplificatorul operaional A1 comut i blocul de semnalizare avertizeaz circuitul PLL c

s-a ieit din zona de funcionare corect (semnalul EOR).

5.3.2.3 Sintetizoare de frecven realizate cu circuite PLL digitale

Observnd schema bloc din figura 5.3.5, se constat c prin simpla adugare a unui

oscilator de referin circuitul PLL digital devine cel mai simplu sintetizor.

Aceasta simplitate explic interesul strnit de posibilitatea folosirii circuitelor PLL

digitale pentru sinteza de frecven i nenumratele studii care i-au fost dedicate n

decursul timpului.

25

Sisteme i Echipamente pentru Comunicatii Radio

Fig. 5.3.10 Schema bloc a celui mai simplu sintetizor cu circuite DPLL.

Divizorul N1 nu este strict necesar; el poate lipsi dac este disponibil un oscilator de

referin cu frecvena necesar. Aa cum a rezultat n paragraful precedent, la sincronism:

fv=

fo

= f r; f o= N f r

N

(5.3.19)

Deci prin modificarea coeficientului de divizare, se pot obine semnale cu frecvene

care s acopere o gam oarecare cu pasul fr. Limitele gamei acoperite pe aceast cale

depind de parametrii buclei (OCT, comparator de faz) i de performanele impuse

semnalului generat.

Este evident c un astfel de sintetizor poate fi caracterizat prin dimensiuni reduse i

consum mic. Totui este util de precizat c soluia prezentat mai sus este rareori folosit

ca atare.

Un prim motiv const n limitele care caracterizeaz divizoarele programabile.

Astfel, divizoarele programabile cu circuite CMOS se pot realiza pn la zeci de MHz;

divizoarele cu circuite rapide pot merge pn la sute de MHz; exist i divizoare cu

circuite de mare vitez care pot funciona la frecvene mai mari de 1 GHz. Domeniul de

26

Sisteme i Echipamente pentru Comunicatii Radio

interes pentru sintez se ntinde la zeci de GHz iar preul de cost i consumul de energie

care caracterizeaz divizorul cresc la fel de rapid ca limita care trebuie atins.

In consecin o schem bloc a unui circuit DPLL cu performane convenabile

pentru sinteza de frecven este cea dat n figura 5.3.11.

Se

observ

au

fost

introduse, n plus, un divizor cu factor de divizare fix N2 (cunoscut sub denumirea de

divizor de prescalare, sau prescaler), i un mixer. Divizoarele fixe pot fi realizate

convenabil pn la frecvene foarte ridicate; mixerul permite realizarea unor sisteme cu

mai multe circuite PLL.

Fig. 5.3.11 Folosirea circuitelor DPLL pentru sinteza de frecven; o schem bloc perfecionat.

Pentru noua structur cu notaiile de pe figura 5.3.11 se constat c la sincronism

sunt valabile relaiile:

fv =

1 fo

( - f); f o = (N f r + f) N 2

N N2

(5.3.20)

Cu alte cuvinte, prin mixare se poate realiza o deplasare a domeniului sintetizat cu

un ecart (N2 fr), iar prin divizarea cu N2 pasul cu care se face sinteza devine N2 fr. Creterea

pasului nu poate fi acceptat totdeauna. Pentru a menine vechea valoare trebuie redus

corespunztor frecvena de referin. La rndul ei, reducerea frecvenei de referin fr nu

este convenabil deoarece o valoare mic a ei implic o band de trecere tot mai redus

pentru filtrul de bucl pentru a evita modulaia nedorit a OCT. Banda ngust a filtrului

de bucl implic timp de achiziie (timp de intrare n sincronism) mare etc.

27

Sisteme i Echipamente pentru Comunicatii Radio

Pentru a mpca aceste cerine contradictorii s-a apelat la o soluie care const n

realizarea unor divizoare de prescalare cu factor de divizare fix dar avnd cteva valori

comutabile printr-o comand aplicat din exterior.

Pentru a exemplifica aceast soluie se consider cazul divizoarelor programabile cu

10; un divizor de prescalare utilizabil n acest caz are coeficientul N2=10/11. Schema bloc

a tandemului divizor programabil-divizor de prescalare este dat n figura 5.3.12.

Fig. 5.3.12 Divizoare programabile cu divizor de prescalare cu factor de divizare

controlabil

Divizoarele N i N' sunt programabile i lucreaz prin decrementare. Se consider

c au fost alei coeficienii de divizare:

M

N = Am 10 M -m ; N < 9

(5.3.21)

m=1

unde

Am , {0,1,..,9}

(5.3.22)

Dac divizorul de prescalare are factorul de divizare fix i egal cu 10 se obine:

M

M - m +1

f o = N f r N 2 = f r A m10

(5.3.23)

m =1

deci pasul minim este 10fr.

Divizorul cu pas controlabil 10/11 lucreaz cu N2=11 ct timp numrtorul auxiliar

nu a atins valoarea programat i cu N2=10 n rest; se deduce

28

Sisteme i Echipamente pentru Comunicatii Radio

M

m=1

m=1

N = 11 N + 10[ Am 10 M -m - N ] = Am 10 M -m+1 + N (5.3.24)

Deci prin factorul de divizare N', al numrtorului auxiliar se controleaz digitul

care este mascat de divizorul de prescalare i, pe ansamblu, se realizeaz un pas egal cu fr.

De menionat c exist divizoare de prescalare decadice cu mai muli indici ( de

exemplu DP111 care are N2=100/110/111) precum i divizoare de prescalare binare (de

exemplu N2=30/32).

Un al doilea motiv pentru care structura sintetizorului analizat nu este, totdeauna,

satisfctoare const n necesitatea evitrii modulaiei parazite care se realizeaz cu

componente provenite de la comparatorul de faz, deci componente avnd frecvena

semnalului de referin sau frecvena unei armonici a acestuia. Aa cum am mai

menionat, aceste componente avnd frecvene mult mai mici dect frecvena OCT pot

produce, chiar la amplitudini foarte mici, indici de modulaie n frecven semnificativi.

Pentru a reduce acest efect se pot folosi dou procedee:

introducerea unui filtru de rejecie, n cascad cu filtrul de bucl, axat pe frecvena

componentei corespunztoare;

folosirea unor comparatoare de faz perfecionate.

In cele ce urmeaz se va prezenta cel de al doilea procedeu. Aa cum s-a artat n

paragraful 5.3.2.2 prelucrarea unor semnale logice a permis realizarea unei mari varieti

de comparatoare de faz.

Sinteza de frecvena implic acoperirea unor game largi de frecven cu timpi de

achiziie redui i cu puritate spectral ct mai ridicat. Avnd n vedere contradicia

existent ntre aceste cerine se ajunge la concluzia c trebuie combinate calitile mai

multor comparatoare de faz:

un comparator cu panta redus care s permit realizarea benzii de prindere

impuse cu timp de achiziie bun;

29

Sisteme i Echipamente pentru Comunicatii Radio

un comparator cu panta mare i ondulaii mici ale tensiunii de ieire, care s

menin bucla n sincronism cu modulaie parazit redus.

Fig. 5.3.13 Comparator de faz complex: a) schema bloc;

b)formele de und care evideniaz funcionarea modulatorului de faz.

O astfel de soluie se poate implementa folosind dou comparatoare dintre cele

prezentate anterior cu o logic adecvat de control (figura 5.3.13-a). Atunci cnd bucla

este in afara sincronismului, acioneaz comparatorul digital cu panta relativ mic dar care

acoper domeniul (-2,2) i permite realizarea sigur a sincronizrii.

Apropierea buclei de sincronism este sesizat de comparatorul analogic cu

eantionare i meninere (S&H) care prin logica de control comand blocarea

comparatorului digital i preia controlul. Panta acestuia fiind foarte mare rezult o bun

stabilitate a sincronismului; de asemenea, aa cum s-a artat n paragraful 5.3 semnalul de

comand livrat de acesta const din tensiunea de pe condensatorul de memorare Cc,

tensiune a crei valoare se modific n trepte corespunztoare erorii de faz; de aici rezult

ondulaii mici ale tensiunii de comand a OCT i modulaie parazit redus. Semnalele de

30

Sisteme i Echipamente pentru Comunicatii Radio

la ieierile celor dou comparatoare de faz sunt nsumate prin intermediul filtrului de

bucl.

Schema bloc dat n figura 5.3.13 pune n eviden o alt caracteristic specific

acestor sintetizoare: posibilitatea realizrii modulaiei de faz n bucl. Aceast

posibilitate este extrem de interesant atunci cnd sintetizorul este folosit n sisteme de

comunicaie MF, oferind o modalitate performant de producere indirect a modulaiei n

frecven. Se poate realiza i modulaie direct a OCT cu condiia ca toate componentele

semnalului modulator s se afle la frecvene suficient de ridicate ca s nu se afle n banda

de lucru a circuitului PLL.

Pentru a permite realizarea modulaiei de faz semnalul comparat nu este cel

original ci o replic a sa, ntrziat, creat de ctre modulatorul de faz. Modulatorul

de

faz este un circuit logic care, aa cum se observ din diagramele date n figura 5.3.13-b,

la frontul pozitiv al semnalului sv comut n starea "0": simultan condensatorul CM ncepe

s se ncarce: ncrcarea se realizeaz sub curent constant, pn cnd tensiunea pe

condensator devine egal cu tensiunea Um aplicat pe intrarea de modulaie. In acel

moment apare frontul pozitiv al semnalului aplicat comparatoarelor de faz sv'. Cum aceste

comparatoare lucreaz pe fronturile pozitive, ntre semnalul generat de OCT i semnalul

comparat apare o ntrziere controlabil prin tensiunea Um.

Din punctul de vedere al semnalului generat de OCT aceasta se traduce printr-o

modulaie de faz realizat cu semnalul aplicat pe intrarea modulatorului.

Dac performanele care se obin folosind sintetizoare cu un circuit PLL nu satisfac

cerinele impuse, se poate folosi soluia cu mai multe circuite. O schem bloc care

ilustreaz modul de lucru al unui astfel de sintetizor este dat n figura 5.3.14.

31

Sisteme i Echipamente pentru Comunicatii Radio

Fig. 5.3.14 Sintetizor de frecven realizat cu dou circuite DPLL.

Circuitul PLL din ramura superioar reprezint circuitul principal i este

caracterizat prin valoarea ridicat a frecvenei de referin. In acest fel se pot filtra

corespunztor componentele care ar putea conduce la modulaia de faz nedorit. Circuitul

din ramura inferioar lucreaz la frecvene mult mai coborte i are rolul de a asigura

explorarea domeniului de frecven cu pasul impus.

La sincronismul celor dou circuite sunt valabile relaiile:

f o2 = N02 f r2 ;

f o1 = ( N01f r1 + f o2) N21

(5.3.25)

adic

f o1 = N 21( N 01 f r1 + N 02 f r2 )

unde

32

(5.3.26)

Sisteme i Echipamente pentru Comunicatii Radio

f r1 =

f ro

N 11

f r2 =

f ro

(5.3.27)

N 12

iar foi reprezint frecvena semnalului generat de ctre oscilatorului de referin.

Se constata c pasul cu care se face sinteza este (N21 fr2) i c circuitul auxiliar

trebuie s asigure acoperirea unui interval de frecven egal cu pasul buclei principale.

Pentru a exemplifica acest procedeu se consider cazul unui sintetizor care trebuie

s acopere gama de frecvene cuprins ntre 4GHz i 5GHz, rezoluie de 1 MHz, timp de

stabilizare 1ms, componente nedorite -80 dBc, zgomot de faz -80 dBc;

Se opteaz pentru utilizarea unui oscilator cu cuar lucrnd pe frecvena de 1MHz.

De asemenea se va folosi un divizor de prescalare care s permit folosirea unor divizoare

programabile convenabile (f<40 MHz); rezult N21=100; In sfrit, se alege pasul de

explorare care trebuie asigurat de bucla principal de 100MHz. Aceti parametri precum i

alii determinai prin calcule simple sunt concentrai n tabelul 1.

In condiiile precizate ambele bucle trebuie s acopere domenii relativ nguste, cu

pai care nu sunt foarte mici n comparaie cu frecvena OCT; se poate astfel asigura

filtrarea foarte bun a semnalelor de comand; n orice caz mult mai bun dect dac se

folosea un sintetizor cu un singur circuit.

Tabelul 13.1

N1

fr (kHz)

Nomin

Nomax

N2

Bucla principal

1000

28

37

100

Bucla auxiliar

100

10

1200

1300

33

Sisteme i Echipamente pentru Comunicatii Radio

ncheiem aceast prezentare cu un sintetizor care este proiectat s lucreze n gama

100MHz..1000MHz, cu o rezoluie de 1 Hz, timp de stabilizare 10 microsecunde,

componente nedorite -70 dBc, zgomot de faz -80 dBc.

Avnd n vedere performanele se ajunge uor la concluzia c se va folosi o

soluie mixt: DDS i DPLL. O schem bloc este dat n figura 5.3.15. Schema este

comentat n timpul prelegerii asociate acestui capitol.

34

S-ar putea să vă placă și

- Anexa 5 Declaratie Confirmare Cunoastere Conditii RecrutareDocument1 paginăAnexa 5 Declaratie Confirmare Cunoastere Conditii RecrutareAnonymus_01Încă nu există evaluări

- Secr 05 Circuite PLLDocument24 paginiSecr 05 Circuite PLLAnonymus_01Încă nu există evaluări

- Procedura TETRA Ro v3Document22 paginiProcedura TETRA Ro v3Anonymus_01Încă nu există evaluări

- Toate LaboratoareleDocument141 paginiToate LaboratoareleAnonymus_01Încă nu există evaluări

- Curs DEPI 2009 INGE GAVATDocument86 paginiCurs DEPI 2009 INGE GAVATAnonymus_01Încă nu există evaluări

- Lab 3 - Tranzistorul Cu Efect de CampDocument21 paginiLab 3 - Tranzistorul Cu Efect de CampAnonymus_01Încă nu există evaluări

- Mitropolitul Augustin de Florina Despre Vechi Calendar Is TiDocument4 paginiMitropolitul Augustin de Florina Despre Vechi Calendar Is TiAnonymus_01Încă nu există evaluări