Documente Academic

Documente Profesional

Documente Cultură

Organizare Interna

Încărcat de

Alex AwzTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Organizare Interna

Încărcat de

Alex AwzDrepturi de autor:

Formate disponibile

Cap.

5 Organizarea memoriei unui MC

5.1 Organizarea memoriei de program

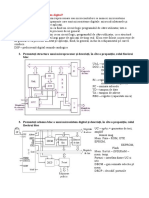

Un exemplu se poate observa în Figura 5.1.

Indexul de program - PC, este organizat pe 13 biţi şi poate accesa un spaţiu de memorie de 8K x

14 însă, în exemplu, doar 1K x 14 (0000h - 03FFh) este implementat.

Vectorul Reset se află la adresa 0000h iar vectorul de înteruperi la adresa 0004h.

În Figura 5.1 se pot observa şi cele 8 nivele ale stivei (Stack).

Fig. 5.1 Exemplu de organizare a memoriei de program

Fig. 5.2 Exemplu de organizare a memoriei de date

5.2 Organizarea memoriei de date

Un exemplu se poate observa în Figura 5.2. Aceasta poate fi împărţită în 2 bancuri,

ambele conţinând registre de uz general (GPR - General Purpose registers) şi registre cu funcţii

speciale (SFR - Special Function registers)

SFR ocupă primele 32 de locuri ale fiecarui banc, 00h-1Fh si 80h-9Fh.

(1Fh = 31d, 1Fh reprezintă notaţia pentru numarul hexazecimal 1F iar

31d reprezintă notaţia pentru numarul zecimal 31)

GPR ocupă părţile de memorie cuprinse între 20h-5Fh (la bancul 0) şi

A0h-DFh (la bancul 1) şi reprezintă memoria RAM a MC.

Restul memoriei care se observă în figură este neimplementat.

Registrele cu funcţii speciale sunt folosite de ALU şi de funcţiile periferice pentru

controlul operaţiilor efectuate de MC (a se vedea un exemplu în Anexa 3). Aceste registre sunt

de tip SRAM.

În cele ce urmează vor fi prezentate detalii de organizare ale câtorva registre de tip SFR.

Registrul STATUS conţine (Figura 5.3):

• starea aritmetică a ALU

• biţii de selectie al bancului memoriei de date (SRAM)

• starea MC la RESET

Fig. 5.3 Registrul Status (exemplu)

Pentru o înţelegere intuitivă, fiecare bit al registrului are o abreviere iar în programul

utilizatorului el poate fi adresat direct sau prin

denumirea sa.

Câteva explicaţii asupra registrului:

- bit 0 = C, Carry/borrow - transport/împrumut este influenţat de utilizarea instrucţiunilor

ADDWF, ADDLW, SUBLW, SUBWF

Cand C = 1, înseamnă că a avut loc un transport de la bitul cel mai semnificativ (Most

Significant bit - MSB).

Cand C = 0, înseamnă că nu a avut loc transport de la MSB.

- bit 2 = Z, zero

Cand Z = 1, înseamnă că rezultatul unei operaţii aritmetice sau logice este zero.

- bit 3 = PD, Power-down - indicator de stare MC

PD = 1 imediat dupa alimentarea MC sau după execuţia instrucţiunii CLRWDT.

PD = 0 dupa execuţia instrucţiunii SLEEP.

- bit 4 = TO, Time-out - indicator de stare MC

TO = 1 după ce s-a alimentat MC, sau după execuţia instrucţiunilor CLRWDT sau SLEEP.

TO = 0 după ce a avut loc intrarea în funcţia WDT.

- bit 5 = RP0, pentru selectarea bancului de memorie

RP0 = 1, se lucrează cu bancul 1 (80h - FFh)

RP0 = 0, se lucrează cu bancul 0 (00h - 7Fh)

- deasupra fiecarui bit apar coduri ce reprezintă tipul sau (R = citire, W = scriere) şi valoarea sa

după alimentarea cu tensiune (0 sau 1; x înseamnă că valoarea este necunoscută)

Registrul OPTION este de tip citire/scriere (Figura 5.4) şi conţine biţi de control

pentru:

• factorii de divizare ai modulelor TMR0 si WDT

• sursa externă de întreruperi la pinul RA2/INT

• modulul TMR0

• legarea cu rezistenţe la VDD a pinilor PORTA

Fig. 5.4 Registrul Option (exemplu)

Iată câteva explicaţii:

- biţii 2-0 = PS2:PS0, Prescaler Select - selectează factorii de divizare conform Tabelului 5.1

Tab. 5.1 Stabilirea factorului de divizare

- bit 3 = PSA, Prescaler Assignment - alocarea factorului de divizare

Când PSA = 1, factorul este alocat modulului WDT.

Când PSA = 0, factorul este alocat modulului Timer0 (TMR0).

- bit 4 = T0SE, TMR0 Source Edge Select - selectează tipul tranziţiei unui semnal aplicat la

pinul RA2/T0CKI, pentru care se va realiza incrementarea unui registru al modulului TMR0

Când T0SE = 1, incrementarea se va face la tranziţia semnalului de

pe 1 pe 0.

Când T0SE = 0, incrementarea se va face la tranziţia semnalului de

pe 0 pe 1.

- bit 6 = INTEDG, Interrupt Edge Select - selectează tipul tranziţiei unui semnal aplicat la

pinul RA2/INT, pentru care se va genera o întrerupere

Când INTEDG = 1, întreruperea va fi generată la detecţia unui front crescător.

Când INTEDG = 0, întreruperea va fi generată la detecţia unui front descrescător.

S-ar putea să vă placă și

- Intel 8051Document32 paginiIntel 8051radyghezÎncă nu există evaluări

- Observaţii Schema Bloc MCDocument3 paginiObservaţii Schema Bloc MCGavril AndraÎncă nu există evaluări

- Probleme MicroDocument30 paginiProbleme MicroCojocaru IonutÎncă nu există evaluări

- Multiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaDocument2 paginiMultiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaCirnaROÎncă nu există evaluări

- Intel 8051Document61 paginiIntel 8051Vuşcan OvidiuÎncă nu există evaluări

- RaspunsuriDocument11 paginiRaspunsuriPan De LaÎncă nu există evaluări

- Referat ICA - Microcontrolerul AT89C52Document10 paginiReferat ICA - Microcontrolerul AT89C52tasseluÎncă nu există evaluări

- ASC 5 Nivelul MicroprogramatDocument22 paginiASC 5 Nivelul MicroprogramatAlis Madalina EneÎncă nu există evaluări

- MICROC - Curs 4 - 2021Document20 paginiMICROC - Curs 4 - 2021Dragoș AndreiÎncă nu există evaluări

- Lab-01 08Document16 paginiLab-01 08Alexandra-Maria AstefanaoieiÎncă nu există evaluări

- ArhitecturiDocument9 paginiArhitecturiLucia NegruÎncă nu există evaluări

- Intel 8080Document15 paginiIntel 8080Maxim MirzencoÎncă nu există evaluări

- Lab 80871Document20 paginiLab 80871Trifut CiprianÎncă nu există evaluări

- Proiectarea Unui Sistem Pe Baza Microprocesorului Intel 8080Document19 paginiProiectarea Unui Sistem Pe Baza Microprocesorului Intel 8080ionÎncă nu există evaluări

- SI Lucrarea1Document30 paginiSI Lucrarea1unknown studentÎncă nu există evaluări

- 1) Consideratii Asupra Unui Sistem DSP. Conversia Digital AnalogicaDocument3 pagini1) Consideratii Asupra Unui Sistem DSP. Conversia Digital AnalogicaCirnaROÎncă nu există evaluări

- Curs 2 - Microprocesorul 8085A - Structura Interna Si FunctionareDocument19 paginiCurs 2 - Microprocesorul 8085A - Structura Interna Si FunctionareManolache NarcisÎncă nu există evaluări

- Curs 2 - PrezentareDocument43 paginiCurs 2 - PrezentareCosti AndreiÎncă nu există evaluări

- Microcontrolere - Laborator 1 - 2020Document17 paginiMicrocontrolere - Laborator 1 - 2020Alina FilipÎncă nu există evaluări

- Circuitele TIMER Ale MicrocontroleruluiDocument16 paginiCircuitele TIMER Ale MicrocontroleruluiAlexandra DumitruÎncă nu există evaluări

- Microcontrolerul 80C51Document28 paginiMicrocontrolerul 80C51Lacatus ValentinÎncă nu există evaluări

- Arhitectura CalculatoarelorDocument13 paginiArhitectura CalculatoarelorMihai GraurÎncă nu există evaluări

- SEP - TMS320C10 - Cap13Document21 paginiSEP - TMS320C10 - Cap13Mops LightÎncă nu există evaluări

- Lab.1 MPDocument10 paginiLab.1 MPCristinaÎncă nu există evaluări

- Laborator 1Document12 paginiLaborator 1Ceban VladislavÎncă nu există evaluări

- Curs 3 - Conectarea Memoriei Si A Dispozitivelor de I-EDocument19 paginiCurs 3 - Conectarea Memoriei Si A Dispozitivelor de I-EDHM1305Încă nu există evaluări

- Teorie ExamenDocument26 paginiTeorie ExamenRazvy RăzvanuÎncă nu există evaluări

- Examen ACDocument47 paginiExamen ACAgafitei AndreiÎncă nu există evaluări

- 5 Book30 Capitolul 5Document8 pagini5 Book30 Capitolul 5Aurelian RaducuÎncă nu există evaluări

- L6a Masina Microprogramata Tanenbaum Mic-1Document10 paginiL6a Masina Microprogramata Tanenbaum Mic-1Bianca PopescuÎncă nu există evaluări

- ProblemeDocument13 paginiProblemeRexy RexÎncă nu există evaluări

- Microcontrolerul 80C51Document28 paginiMicrocontrolerul 80C51Vlad VesaÎncă nu există evaluări

- Curs 3 Arhitectura ADSP 2181Document19 paginiCurs 3 Arhitectura ADSP 2181Sanda RuxandraÎncă nu există evaluări

- LaboratorSM 1 2 3Document28 paginiLaboratorSM 1 2 3Felice LazarÎncă nu există evaluări

- MC Lab2 RomDocument21 paginiMC Lab2 RomAdriana CarmenÎncă nu există evaluări

- Rezolvari PSMDocument15 paginiRezolvari PSMCretz CristiÎncă nu există evaluări

- Cheatsheet CN2Document2 paginiCheatsheet CN2Vlad PopescuÎncă nu există evaluări

- Lab5 2 PDFDocument15 paginiLab5 2 PDFRd FgtÎncă nu există evaluări

- Proiect 2 FINAL2Document20 paginiProiect 2 FINAL2Faryda IuseimÎncă nu există evaluări

- 2 Magistrale PDFDocument14 pagini2 Magistrale PDFAndrei VieruÎncă nu există evaluări

- 03 Porturile Universale de Intrare Iesire Si Afisarea Cu LED-UriDocument39 pagini03 Porturile Universale de Intrare Iesire Si Afisarea Cu LED-Urisuspekt_no1Încă nu există evaluări

- Curs 5.12 UCC PDFDocument13 paginiCurs 5.12 UCC PDFBezmanGeorgeÎncă nu există evaluări

- LaaaaaaaaaalalaaaaaaaaalalaaaaaDocument6 paginiLaaaaaaaaaalalaaaaaaaaalalaaaaaMădălina StănășelÎncă nu există evaluări

- SMC Subiecte RezolvateDocument30 paginiSMC Subiecte Rezolvateandy tudoreanuÎncă nu există evaluări

- Microcontrolere PIC de La A La ZDocument165 paginiMicrocontrolere PIC de La A La ZMihai BrindusoiuÎncă nu există evaluări

- Lab03 - Interrupts On Atmega32Document6 paginiLab03 - Interrupts On Atmega32Marian VladianuÎncă nu există evaluări

- 4 - Familia MCS-51. MC 80512 - Verificare 1 PDFDocument7 pagini4 - Familia MCS-51. MC 80512 - Verificare 1 PDFMath199Încă nu există evaluări

- Microcontrolerul 8051Document19 paginiMicrocontrolerul 8051Dana Vrabii100% (1)

- Arhitectura Calculatoarelor: Capitolul 3 Unitatea Centrală de PrelucrareDocument28 paginiArhitectura Calculatoarelor: Capitolul 3 Unitatea Centrală de PrelucrareMindhunter GamerÎncă nu există evaluări

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- TimerDocument15 paginiTimerGabriel BraşoveanuÎncă nu există evaluări

- CristianAxenie Assembly Programming Course LabDocument403 paginiCristianAxenie Assembly Programming Course LabMu sicÎncă nu există evaluări

- Arhitectura MicroprocesoarelorDocument78 paginiArhitectura MicroprocesoarelorDaniel Anton0% (1)

- Ars Tsac Sem-Probleme st1+2 2014Document17 paginiArs Tsac Sem-Probleme st1+2 2014Ionut PiticasÎncă nu există evaluări

- Curs 7 MAP2014Document28 paginiCurs 7 MAP2014Dark1337Încă nu există evaluări

- Unitatea de Comanda Si Control PDFDocument20 paginiUnitatea de Comanda Si Control PDFNatalia MadanÎncă nu există evaluări