1.Scopul lucrrii: Studierea semnalelor externe, arhitectura intern, i componentele de baz a MP I8080, definirea semnalelor de intrare/ieire.

Proiectarea registrului universal. 2. Noiuni teoretice I8080 Aprut n 1971, a fost cel mai rspndit microprocesor de 8 bii. Realizat n tehnologie NMOS, cu 40 de terminale, utilizeaz 3 tensiuni de alimentare: +5 Vcc, -5 Vcc, +12 Vcc i dou semnale de tact de aceeai frecven (tipic 2 MHz), dar defazate. Toate intrrile i ieirile sunt compatibile TTL; Magistrala de date este de 8 bii (D0 - D7) iar cea de adrese este de 16 bii (A0 - A15), ceea ce permite adresarea unei memorii de maxim 64 kB; Poate adresa 512 dispozitive de intrare/ieire (porturi) distincte; Proceseaz cuvinte de date de 8 bii i adrese de 16 bii; Formeaz memoria stiv n exterior, n spaiul de memorie adresabil; Setul de instruciuni conine 72 de tipuri, n total poate executa 244 de instruciuni distincte. 2.1 Arhitectura extern

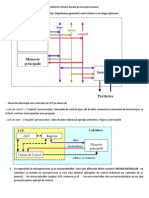

Fig.1.1 Intel 8080 Configuraia semnalelor la pini

�Semnificaie i funciile semnalelor: Magistrala de date: D0 - D7 - linii bidirecionale cu trei stri, prin care se realizeaz schimbul de informaie dintre procesor i memorie sau porturi de intrare / ieire. Magistrala de adrese: A0 - A15 - linii unidirecionale cu trei stri (three state), prin care se transmite o adres de 16 bii ctre memorie sau de 8 bii ctre porturi. Este orientat de la microprocesor spre exterior. HOLD: intrare pentru cereri de cedare magistrale. Un dispozitiv inteligent extern solicit controlul total asupra magistralelor n vederea accesului direct la memorie (tehnic DMA - Direct Access Memory). HLDA: ieire, rspuns la cererea HOLD, confirmnd acceptarea acestei cereri, dup trecerea magistralelor de adrese, date i control n starea SIR (starea nalt impedan sau starea ''a treia''). WR: ieire cu trei stri (Write) activ n 0 logic; determin o operaie de scriere n memorie sau n porturi. INT: (Interrupt request) cerere de ntrerupere emis de un dispozitiv extern pentru tratare prioritar (procesorul trece la execuia unei subrutine de tratare ntrerupere, dup terminarea instruciunii n execuie). INTE: ieire cu trei stri (Interrupt Enable), activ n 1 logic, cnd microprocesorul execut un ciclu main de acceptare ntrerupere. DBIN: ieire cu trei stri (Data Bus Input), care indic sensul transferului pe magistrala de date. Dac este 1 logic, magistrala de date este orientat ctre microprocesor (intrare date). WAIT: semnal generat de microprocesor prin care informeaz dispozitivele externe c se afl n starea de ateptare date. n aceast stare, procesorul nu execut operaii interne. READY: semnal generat extern, activ n 1; informeaz procesorul c o dat de 8 bii este disponibil i stabil pe magistrala de date. Este confirmarea ateptat de procesor n starea WAIT pentru a transfera data de pe magistral n registrele interne. Perechea de semnale WAIT-READY permite schimbul de informaie cu memorii sau porturi ''lente'', care necesit mai mult de o perioad de tact pentru ncrcarea unui octet pe magistrala de date. RESET: semnal de iniializare, generat din exterior, activ n 1. Are ca efect principal iniializarea registrului PC cu 0000 H, ceea ce duce la reluarea execuiei de la adresa 0000 H. De regul, la aceast adres ncepe un program de iniializare a sistemului de calcul. Semnalul RESET este generat automat la apariia tensiunilor de alimentare (la pornirea sistemului) dar poate fi generat n orice moment prin apsarea unui buton, deci la intervenia operatorului.

�2.2 Arhitectura intern Arhitectura intern a microprocesorului I8080 const din urmtoarele uniti funcionale (Fig.1.2): Zona registrelor de date i adrese; Registre de instruciuni; Unitate aritmetic logic (UAL); Unitatea de comanda i temporizare; Magistrala intern de date bidirecional.

Fig.1.2 Arhitectura intern a MP I8080

�2.2.1 Registrele interne Constituie memoria intern de tip SRAM - MOS, format din 6 registre de 16 bii, dintre care 4 pot fi utilizate i ca 8 registre de 8 bii. a) Registrele de uz general sunt: A (Acumulatorul), B, C, D, E, H, L, ca registre de 8 bii sau B, D, H ca registre de 16 bii. Sunt la dispoziia utilizatorului prin intermediul setului de instruciuni. Acumulatorul are i rol de registru de deplasare. b) Registre de manevr: Fiind invizibile pentru programator, sunt folosite de ctre procesor ca locaii de memorie temporar: W, Z - registre de cte 8 bii care se pot accesa i c un registru dublu de 16 bii numit WZ, utilizat de ctre procesor pentru memorarea adreselor salturilor necondiionate; T - Temporar Register utilizat de ctre procesor pentru diverse instruciuni; DB - Data Buffer registru tampon bidirecional de 8 bii utilizat la interfaa dintre procesor i lumea exterioar; AB - Address Buffer registru de 16 bii care izoleaz magistrala de adrese intern de cea extern. c) Registrele de adres: PC (Program Counter) conine adresa de 16 bii a instruciunii urmtoare din program; pentru extragerea instruciunii, coninutul registrului PC se ncarc pe magistrala extern de adrese. Dup transferul fiecrui octet, coninutul lui PC creste cu o unitate, pentru adresarea octetului urmtor. SP (Stack Pointer) - indicator de stiv, conine adresa ultimului operand introdus n memoria stiv, organizat n memoria RAM extern; operaiile de scriere/citire cu stiva se realizeaz prin intermediul registrului SP. Un operand de 8 bii poate fi transferat ntre registrele interne prin intermediul magistralei interne de date de 8 bii, sub controlul unei instruciuni de transfer. Registrul surs (care conine operandul), specificat n instruciune, se conecteaz la magistrala intern prin intermediul unui multiplexor de 8 bii; apoi se selecteaz registrul destinaie n care se transfer operandul de pe magistral. Tot prin magistrala intern se realizeaz transferuri ntre un registru i o locaie de memorie. Adresele sunt operanzi de 16 bii care se transfer magistralei externe de adrese prin intermediu unui registru special de incrementare / decrementare i unui registru tampon, de memorare temporar, conectat direct cu magistrala extern. Registrul tampon are rolul de a menine adresa pe magistral un interval de timp suficient ca aceasta s fie recepionat de memorie sau porturi.

�d) Registrul i decodorul de instruciuni Instruciunile microprocesorului Intel 8080 conin 1, 2 sau 3 octei, dintre care primul octet reprezint codul operaiei ce se efectueaz la execuia instruciunii i este transferat din memorie n registrul IR (Instruction Register). Codul operaiei este interpretat de decodor (Instruction Decoder) ale crui ieiri, sincronizate cu impulsurile de tact, genereaz sub controlul UCC toate comenzile interne i externe necesare efecturii operaiei. Semnificaia biilor din cuvntul de stare este urmtoarea: S - Sign este setat dac rezultatul unei operaii aritmetice este negativ; Z - Zero este setat dac rezultatul unei operaii aritmetice este zero; H - Half Carry este setat dac exist semi-transport, de la bitul 3 la bitul 4 (se folosete la corecia zecimal DAA); P/V - Parity/Overflow este setat dac numrul de bii de valoare 1 din cuvnt este par (pentru paritate), sau dac exist o depire de domeniu (pentru operaii aritmetice); N - Name of the last operation este setat dac ultima operaie a fost adunare (indicator folosit pentru instruciunea DAA); C - Carry este setat dac exist transport de la bitul cel mai semnificativ (MSB); X - bit a crui valoare nu conteaz. Semnale generate i primise de microprocesor Semnalele de tact: 1,2, sunt generate de un circuit specializat din familia Intel, 8224 - generator de tact. Sunt semnale cu amplitudinea de 12 V i frecvena de 2MHz, defazate (fig.1.3). Perioada T, adic intervalul de timp dintre dou treceri succesive din 0 n 1 este numit stare i determin durata unei operaii elementare (T = 1/(2106) = 0,5ms). Semnalul SYNC delimiteaz durata unui ciclu main (o singur referire la memorie sau la dispozitive I/O), fiind generat de fronturile semnalului de tact 2, sub controlul UCC.

�Fig.1.3 Diagramele semnalelor de tact i SYNC Un ciclu main are o durat variabil de 3 - 5 stri n funcie de tipul operaiei ce se efectueaz; o instruciune se execut n 1 - 5 cicluri main. 2.2.3 Unitatea aritmetic i logic (ALU - Arithmetic and Logic Unit) Este o structur format din circuite logice combinaionale, care realizeaz sub controlul UCC operaii aritmetice (adunri, scderi) i operaii logice (Si, Sau, Sau Exclusiv) bit cu bit, ntre doi operanzi de 8 bii. Pentru memorarea celor doi operanzi, sunt necesare dou registre de stocare temporar (pe durata operaiei); acestea sunt T i Acc. Latch. Registrul Acc. este utilizat iniial pentru unul din operanzi, care trece n Acc. Latch i n final pentru rezultatul operaiei. Pentru operaii aritmetice n cod BCD sunt necesare corecii ale rezultatelor, care sunt realizate de un bloc special DAj. (Decimal Adjust), iar pentru informaii referitoare la rezultatul operaiei este necesar registrul F (Flags) al indicatorilor de condiii sau registrul de stare al UAL (fig.1.4).

Fig.1.4 Registrul indicatorilor de condiii (F) al microprocesorului I8080 3.Mersul lucrrii 1.Proiectarea registrului serie/paralel de 8 bii cu deplasare dreapta.

�0V 0V

0V

0V

0V

5V

D CP Q _ Q D CP Q _ Q D CP Q _ Q D CP Q _ Q

0V

0V

0V

0V

0V

D CP

Q _ Q

D CP

Q _ Q

D CP

Q _ Q

D CP

Q _ Q

Fig.1Registrul serie/paralel cu deplasare spre dreapta 2.Proiectarea registrului serie de 8 bii cu deplasare n ambele direcii.

5V

0V

D CP Q _ Q D CP Q _ Q D CP Q _ Q D CP Q _ Q

0V

5V

D CP

Q _ Q

D CP

Q _ Q

D CP

Q _ Q

D CP

Q _ Q

Fig.2Registrul serie cu deplasare in ambele directii 3.Proiectarea registrului universal de 8 bii.

�0V 0V 0V

0V

0V

0V

0V

0V

0 V

0V

0 V

D Q _ CPQ D Q _ CPQ

D Q _ CPQ

D Q _ CPQ

D Q _ CPQ

D Q _ CPQ

D Q _ CPQ

D Q _ CPQ

0V

5 V

Fig.3 Registrul universal Concluzii: n aceast lucrare de laborator am fcut cunotin cu studiul structurii externe i interne a microprocesorului I8080.De asemenea am studiat arhitectura intern i componentele de baz a acestui microprocesor definind semnalele de intrare-ieire.Am proiectat registrul universal care poate fi utilizat ca registru serie ct i paralel,destinat memorrii (nscrierii informaiei) i transformrii codului paralel n cod serie i invers,cu deplasare dreapta spre stnga i invers.

�MINISTERUL EDUCAIEI AL REPUBLICII MOLDOVA UNIVERSITATEA TEHNIC A MOLDOVEI FACULTATEA RADIOELECTRONIC I TELECOMUNICAII CATEDRA SISTEME OPTOELECTRONICE

DAREA DE SEAM

la laboratorul nr.1 Tema:Studiul structurii externe i interne a microprocesorului I8080

�La disciplina: Structuri microprocesorale

A efectuat st. gr. IMTC-091 A verificat lect.univ. Zubco Alexandru

Chiinu 2010