Documente Academic

Documente Profesional

Documente Cultură

SEP - TMS320C10 - Cap13

Încărcat de

Mops LightTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

SEP - TMS320C10 - Cap13

Încărcat de

Mops LightDrepturi de autor:

Formate disponibile

TMS 32010

Introducere Procesorul pentru prelucrarea digitala a semnalelor TMS 32010 (Texas Instruments) a fost creeat pentru a acoperi o gama larga de aplicatii care implica un volum mare de calcule numerice si o viteza mare de operare. Prin caracteristicile sale, TMS 32010 intruneste capabilitatile numerice ale procesoarelor matriciale cu flexibilitatea microcontrolerelor de viteza ridicata, constituind o alternativa avantajoasa din punct de vedere a pretului de cost la procesoarele bit-slice de tip multicip si la dispozitivele VLSI realizate la cerere (custom). Citeva din domeniile de utilizare ale acestui dispozitiv sint prezentate in tabelul 1.

1.

Caracteristici generale

Circuitul DSP TMS 32010 a fost realizat initial in doua variante constructive: TMS 32010 si TMS 320M10, care prezinta urmatoarele caracteristici constructive si functionale: - ciclul instructiune: - memorie RAM interna: - memorie ROM interna: 200 ns 288 octeti (144 x 16 biti) TMS 32010- fara, TMS 320M10 - 3 Ko

- extensie posibila a memoriei de program externa pina la 8 Ko, cu posibilitate de operare la viteza completa - unitatea de executie contine: ALU/ acumulator de 32 biti, multiplicator de 16 x 16 biti in 200 ns, registru pentru deplasare binara (barrel shifter) cu 0-15 ranguri binare, circuit de scalare cu 0, 1 sau 4 ranguri (shifter) - bus pentru transfer bidirectional pe 16 biti cu rata de transfer de 40 Mo/sec - bus pentru transfer I/O cu 8 linii - sistem de intreruperi vectorizat care asigura salvarea automata si integrala a contextului - codarea instructiunilor si a datelor pe 16 biti - mod de operare in virgula fixa cu operanzi reprezentati in cod complement fata de 2 - alimentarea circuitului de la o singura sursa de alimentare, +5V - circuitul a fost realizat initial intr-o capsula DIL cu 40 pini

Tabelul 1

2.

Arhitectura interna

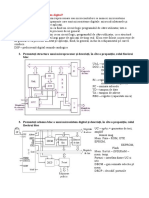

Procesorul TMS 32010 utilizeaza o aritectura de tip Harvard modificata care asigura o viteza sporita de executie a programelor si o flexibilitate sporita in manipularea datelor. In cazul arhitecturii Harvard "clasice", sint folosite spatii separate de memorie pentru programe, respectiv pentru date, ceea ce permite suprapunerea completa a operatilor de extragere a codurilor instructiunilor cu cele de executie. Procesoarele familiei TMS 3201x folosesc o structura modificata in sensul ca exista posibilitatea realizarii de transferuri intre spatiile de coduri si cele de date. Aceasta modificare permite citirea coeficientilor unui algoritm stocat in memoria pentru programe, eliminind necesitatea prevederii unei memorii ROM separate pentru date. De asemenea, sint disponibile instructiuni cu operanzi imediati precum si subrutine bazate pe valorile calculate. TMS 32010 are facilitati hardware pentru a realiza functiuni pe care alte procesoare le realizeaza curent prin software. Exemple: Folosirea multiplicatorului hard care executa o inmultire intr-un singur ciclu de 200 ns., circuitul de deplasare binara de la intrarea ALU, registrele auxiliare pentru adresarea indirecta a memoriei RAM- date, care pot fi configurate in mod de lucru cu incrementare sau decrementare, s.a. Schema bloc a procesoarelor TMS 320C1x este data in Fig. 1, iar structura interna a procesorului TMS 320M10 este prezentata in Fig. 2.

Fig. 1

2.1.

Particularitati functionale

Procesorul combina avantajele arhitecturii Harvard cu executia pipe-line a instructiunilor. Procesorul poate avea memorie pentru programe interna (numai TMS 320M10, respectiv 1536 x 16 biti memorie ROM) si externa. Memoria externa direct adresabila poate avea capacitatea maxima de 4Kcuvinte x 16 biti. Extragerea instructiunilor din memoria externa se executa cu viteza maxima, de aceea sint necesare circuite cu timpi de acces de max. 100 ns. Memoria interna pentru date are capacitatea de 144 x 16 biti. Operanzii instructiunilor sint extrasi din acest RAM. Nu exista posibilitatea extragerii directe a operanzilor din exteriorul microprocesorului. In schimb, pot fi transferate date in RAM de la un periferic cu instructiuni IN, sau pot fi citite din memoria de program cu instructiunea TBLR (Table Read). Folosind instructiuni OUT pot fi transferate date din RAM catre un periferic, iar cu instructiunea TBLW (Table Write) pot fi inscrise date din RAM in memoria de program (evident, numai in RAM- ul extern). Procesorul foloseste un pipe-line cu doua etaje care permite ca tratarea simultana a doua instructiuni, dupa cum este ilustrat in Fig. 3. Se observa suprapunerea operatiei de extargere a codului cu executia instructiunii extrase anterior. Paralelismul, datorat imbinarii arhitecturii Harvard cu executia pipe-line a operatiilor asigura un ciclu de executie a instructiunilor de max. 200 ns.

Fig. 2

Fig. 3

2.2.

Elementele aritmetice

Procesorul poseda 4 elemente aritmetice de baza: ALU, acumulatorul, multiplicatorul si circuitele pentru deplasari binare. Toate operatiile aritmetice sint executate in cod complement fata de 2. Multe din instructiunile aritmetice adreseaza date din RAM, direct sau indirect pe care le transfera prin circuitul barrel shifter (BS). BS poate deplasa cuvintele binare la stinga cu 0 - 15 ranguri, numarul fiind specificat in codul instructiunilor. Apoi datele sint transmise catre ALU unde sint stocate sau adunate/scazute din acumulator. Rezultatul obtinut in acumulator poate fi stocat in RAM- date. Intrucit acumulatorul are 32 de biti, cele doua cuvinte de 16 biti trebuie stocate separat. Shifterul paralel de la iesirea acumulatorului executa deplasarea la stinga cu 0, 1 sau 4 ranguri, pentru a realiza scalarea rezultatului inainte de a fi transferat in RAM. ALU lucreaza cu cuvinte de 32 de biti si poate executa adunari, scaderi, operatii logice. Acumulatorul este sursa primului operand si destinatia rezultatului. Exemple de operatii executate de ALU:

----------------------------------------------------------------------------------------------------------------------------- ----------

Functia

Rezultatul din ALU bitii 31- 16 bitii 15- 0

================================================================== XOR AND OR (zero) + (bitii 31-16) (zero) + ( (zero) + ( " " ) ) XOR AND OR (data din mem.) + (bitii 15-0) ( " ( " " )+( ) +( " " ) )

---------------------------------------------------------------------------------------------------------------

Obs. Operatia logica se executa cu data zero pentru bitii 31-16 din acumulator, respectiv cu data din memorie pentru bitii 15-0 ai acumulatorului.

2.3.

Modul saturat

Procesorul poseda un mod de functionare distinct, programat prin setarea registrului de 1 bit OVM (OVerflow Mode). Operatia se executa cu ajutorul instructiunilor SOVM (setare), respectiv ROVM (resetare). Cind registrul OVM este setat microprocesorul functioneaza in modul saturat, respectiv, la aparitia unei depasiri de scala incarca automat in acumulator cea mai pozitiva sau cea mai negativa valoare a rezultatului din ALU. Semnul depasirii determina ce valoare va fi incarcata. Daca procesorul lucreaza in modul nesaturat, in acumulator se incarca valoarea nemodificata de la iesirea ALU. In prelucrarea semnalelor depasirea scalei provoaca erori grave, manifestate prin tranzitia semnalelor intre gama valorilor foarte mari si cea a valorilor foarte mici. Facilitatea OVM cu care este dotat TMS 32010 compenseaza acest efect folosind o aritmetica cu "saturatie". Cind procesorul lucreaza in modul saturat, o depasire de scala va determina incarcarea in acumulator a celei mai mici sau a celei mai mari valori reprezentabile in locul valorii eronate. In regim nesaturat, procesorul incarca in acumulator rezultatul nemodificat chiar daca este afectat de o depasire de scala.

2.4.

Acumulatorul

Are capacitatea de 32 de biti. Procesorul poseda doua instructiuni pentru transferul continutului sau in memoria pentru date: SACH- pentru cuvintul de ordin superior constituit din bitii 31-16, respectiv SACL- pentru cuvintul de ordin inferior. Starea acumulatorului este reflectata de bistabilul de stare (flag-ul) OV (OVerflow) care este setat atunci cind a existat o depasire a scalei. OV este o parte a registrului de stare a procesorului care poate fi salvat in memoria pentru date. Dupa ce indicatorul OV a fost setat, doar executia unor instructiuni de ramificare, de verificare a depasirii scalei sau de modificare directa a registrului de stare poate sa-l reseteze. Exista unele stari ale acumulatorului care pot fi testate in cadrul executiei instructiunilor de ramificare: ---------------------------------------------------------------------------------------------------------------Instructiunea Conditia testata

================================================================== BLZ BLEZ BGZ BGEZ BNZ BZ <0

0

>0

0

<>0 =0

6

2.5.

Multiplicatorul

Multiplicatorul 16 x 16 este constituit din 3 unitati: matricea de multiplicare, registrul T si registrul P. Registrul T pastreaza deinmultitul, care trebuie incarcat prinul, din memoria RAM- date, cu una din urmatoarele instructiuni: LT, LTA sau LTD, dupa care se executa inmultirea cu instructiunile MPYK (inmultire cu operand imediat) sau MPY. Instructiunea MPY foloseste operand de 16 biti din memorie, iar MPYK operand de 13 biti continut in codul instructiunii. Rezultatul inmultirii este depus in registrul P. Rezultatul poate fi incarcat in acumulator (PAC), adunat la acumulator (APAC) sau scazut din acesta (SPAC). Operatia complexa de multiplicare si acumulare, la o rata de 400 ns. poate fi realizata cu secventa de instructiuni LTA/ LTD si MPY/ MPYK.

2.6.

Registrele de deplasare

Procesorul contine 2 registre pentru deplasari (shift register): - registrul BS situat la intrarea ALU; - registrul shifter de la iesirea acumulatorului. BS executa numai deplasari la stinga cu 0- 15 ranguri asupra datelor incarcate, adunate sau scazute din ALU cu una din instructiunile LAC, ADD sau SUB. Dupa deplasare bitii de ordin inferior ramasi liberi sint inlocuiti cu 0, iar semnul este extins la stinga pina la completarea celor 32 de biti ai cuvintului (operatia este denumita deplasare aritmetica la stinga). Exemplu: Locatia de adresa 20H contine numarul in cod complement fata de 2, 7EBCH. In urma executiei instructiunii LAC 20,4 (incarcarea acumulatorului cu data de la adresa 20H cu deplasarea continutului cu 4 ranguri la stinga) rezulta: LAC 20,4 7FEBH 0007FEB0H Daca data este 8000H cuvintul rezultat se completeaza la stinga cu 1 pina la 32 de biti, iar daca este <8000H se completeaza cu zerouri. Exista si instructiuni pentru executia de operatii numai cu jumatatea inferioara a acumulatorului fara extensia semnului (acestea au extensia S; de exemplu: ADDS, SUBS). Registrul pentru deplasare paralel de la iesirea acumulatorului este activat cu instructiunea SACH (Stocheaza jumatatea de ordin superior a acumulatorului). Instructiunea deplaseaza la stinga cuvintul de 32 de biti din acumulator care este apoi transferat in RAM- date, operatie care conduce la pierderea bitilor de ordin superior. Deplasarea se executa cu 0, 1 sau 4 ranguri binare. Deplasarea directa la dreapta nu este posibila. Exemplu: SACH 40,4 A34B78CDH 34B7H (continutul RAM de adresa 40H)

2.7.

Memoria pentru date

Este constituita din 144 locatii de cite 16 biti si contine operanzii care nu sint adresati imediat. Uneori este necesar ca operanzii sa fie stocati in memoria externa de unde sa fie transferati in/din memoria RAM interna. Pentru aceasta operatie sint disponibile doua posibilitati: - instructiunile TBLR si TBLW; - instructiunile de lucru cu dispozitivele I/O, IN/OUT. Adresarea memoriei de date se poate face in doua moduri:

a) Adresare indirecta. Adresa este constituita din cei 8 biti de ordin inferior ai registrelor auxiliare AR0 sau AR1, suficienti pentru accesarea celor 144 locatii RAM intern. Registrul auxiliar curent este selectat de registrul pointer, ARP. In plus, registrul auxiliar curent poate fi autoincrementat/ autodecrementat, operatie care are loc dupa executia instructiunii. Exemplu: LARP LARK AR0,5 ADD * ;Incarca 0 in ARP (Registrul auxiliar curent va fi AR0) ;Incarca data 5H in AR0 ;Aduna la acumulator data din locatia de adresa data de AR0 apoi ;comuta AR0 cu AR1 b) Adresare directa. 7 biti ai cuvintului instructiune sint concatenati cu pointerul de pagina (DP- Data Page Pointer) pentru a obtine adresa operandului din memorie. DP= 0 DP= 1 - este selectata pagina 0, respectiv locatiile 0- 127 - este selectata pagina 1, respectiv locatiile 128-144

In mod curent pagina 1 de memorie contine variabilele de sistem accesate mai rar, ca de exemplu cele folosite pentru rutinele de intreruperi.

2.8.

Registrele interne

Procesorul contine 2 registre auxiliare de 16 biti care indeplinesc urmatoarele functiuni: adresarea indirecta a memoriei, stocarea operanzilor si controlul buclelor. Pentru adresarea indirecta sint folositi bitii 7- 0 ai celor 2 registre. Instructiunea de ramificare BANZ foloseste registrul auxiliar curent drept contor pentru operatiile executate in bucla. Exemplu: LARP 0 LARK AR0,5 LOOP: ADD * ;Incarca 0 in ARP (AR0 devine registrul auxiliar curent) ;Incarca 5H in AR0 ;Aduna la acumulator data de la adresa 5H apoi comuta ;AR0 cu AR1 BANZ LOOP ;Repeta bucla de 6 ori

8

La operatia de incrementare/ decrementare sint modificati doar bitii 8- 0 ai registrelor auxiliare. Continutul acestor registre poate fi transferat in RAM- date cu instructiunile SAR si LAR.

2.9.

Memoria pentru programe

Memoria pentru programe poate avea capacitatea de max. 4 K x 16 biti. Varianta TMS 320M10 poseda o arie de memorie ROM interna de 1536 cuvinte de 16 biti. Modul de functionare a memoriei ROM interne este controlat de linia de comanda MC/MP. Procesorul are 2 moduri de lucru: modul microcomputer (MC/ MP = 1) si modul microprocesor (MC/ MP = 0). a) Modul microcomputer (numai pentru TMS 320M10)

Din cele 1536 locatii ROM intern doar 1523 sint la dispozitia utilizatorului. Locatiile de adrese 1524 1536 sint rezervate de firma pentru operatii de testare. Arhitectura microprocesorului permite folosirea a inca 2560 de locatii externe pentru stocarea programelor (in total procesorul poate lucra cu 1536+ 2560= 4096 locatii memorie de program). b) Modul microprocesor

In acest mod procesorul accepta o memorie externa de max. 4 Ko. Locatiile 0 si 1 ale memoriei pentru program contin vectorul de initializare. Dupa initializare (RESET) procesorul acceseaza instructiunea de la adresa 0. In mod curent la adresele 0 si 1 se introduce codul unei instructiuni de ramificare. Locatiile de adresa 2 si 3 contin vectorul de intrerupere. Organizarea memoriei in cele 2 moduri de functionare este prezentata in Fig. 4.

Fig. 4

9

Pentru folosirea memoriei externe procesorul are 12 linii pentru adresare (A11- A0) care transfera continutul contorului de program, PC sau adresa unui port I/O. Cind este executata operatia de extragere a codului unei instructiuni din memoria externa procesorul activeaza linia MEN (Memory ENable). Codul instructiunii este citit pe magistrala de date. Durata unui ciclu de transfer cu memoria externa este de 200 ns. ceea ce implica folosirea unor memorii cu timp de acces de max. 100 ns. Modul de conectare a memoriei externe este prezentat in fig. 5. Semnalul MEN nu este activ niciodata simultan cu WE si DEN. MEN este 0 in orice ciclu, cu exceptia operatiilor I/O cerute de instructiunile IN, OUT sau TBLW. In aceste instructiuni multiciclu, MEN = 0 pe durata ciclurilor in care WE sau DEN nu sint 0.

Fig. 5

2.10.

Contorul de program

Contorul de program (PC) si stiva permit utilizatorului sa execute salturi in program, intreruperi si se execute instructiunile TBLR si TBLW. Registrul PC are capacitatea de 12 biti si contine adresa urmatoarei instructiuni din memoria de program care va fi executata de microprocesor. Dupa accesarea unui cod PC este incrementat cu 1. Dupa initializare PC = 0. PC este transferat pe magistrala de adrese in toate modurile de functionare. Liniile A11- A3 sint folosite numai pentru adresele memoriei, in timp ce liniile A2- A0 sint multiplexate cu adresele porturilor I/O. Memoria de program este intotdeauna adresata de continutul lui PC. Acesta poate fi modificat prin executia instructiunilor de ramificare (toate adresele de ramificare sint specificate cu adresa absoluta).

2.11.

Stiva

Stiva are dimensiunea de 12 biti si contine 4 nivele (4 x 12). Instructiunea PUSH salveaza 12 biti, cei mai putin semnificativi in virful stivei, TOS (Top of Stack), iar instructiunea POP executa operatia inversa. Dupa executia instructiunii POP TOS poate fi mutat in memoria de date,

10

prin stocarea cuvintului de ordin inferior al acumulatorului (cu instr. SACL). Aceasta permite extinderea stivei in memoria RAM- date. Intrucit continutul RAM- date poate fi copiat in RAMprogram extern cu instructiunea TBLW stiva poate fi extinsa cu un numar mare de nivele. Circuitul accepta pina la 4 nivele de subrutine sau intreruperi fara ca stiva sa se satureze, daca nu sint executate instructiunile TBLR sau TBLW. Intrucit acestea folosesc un nivel al stivei, procesorul poate utiliza efectiv doar 3 nivele ale stivei pentru subrutine/intreruperi fara sa se satureze. La saturarea stivei continutul ei se deterioreaza. Pentru a manipula un numar mai mare de subrutine/intreruperi se foloseste o parte din RAM- date. In acest caz TOS este salvat chiar la inceputul programului de intrerupere, iar la sfirsit aceasta valoare este transferata inapoi in TOS.

2.12.

Registrul de stare

Registrul de stare (SR-StatusRegister) contine 5 biti(indicatori) de stare care pot fi modificati individual cu instructiuni specifice. SR poate fi salavat in memoria RAM- date cu instructiunea SST, iar o valoare noua poate fi incarcata cu LST (cu exceptia bitului INTM). Acest bit poate fi modificat cu ajutorul instructiunilor EINT/DINT. Structura SR este:

unde: DP -(Data Memory Page Pointer). DP= 0- Selectia primelor 128 cuvinte din RAM- date.

Indicatorul poate fi modificat cu instructiunile LDP sau LDPK; ARP -(Auxiliary Register Pointer). ARP= 0- este selectat AR0, iar ARP= 1- este selectat

AR1. Poate fi modificat cu instructiunile MAR LARP sau cu instructiunile care permit optiunea de adresare indirecta. INTM -(INTerrupt Mask Bit). INTM= 0- sistemul de intreruperi este activ. Acest indicator este setat/resetat cu EINT/ DINT. Cind este executata instructiunea INTM acest bit este resetat. OVM -(OVerflow Mode Bit). OVM= 0- este dezactivat modul saturat de functionare. Indicatorul poate fi incarcat cu SOVM (1), respectiv ROVM (0). OV -(Accumulator OVerflow Flag Register). OV= 0- acumulatorul nu s-a saturat, iar

OV= 1- acumulatorul saturat. Indicatorul poate fi resetat cu instructiunea BV care provoaca o ramificare daca bitul OV este setat. Continutul SR poate fi stocat in RAM- date cu instructiunea SST, in pagina 1, la o locatie specificata de instructiune, sub forma unui cuvint.

11

2.13.

Functiuni I/O

Transferul datelor cu perifericele se executa cu instructiunile IN si OUT, prin intermediul magistralei de date, folosind 2 semnale de comanda: DEN si WE . Structura sistemului I/O este data in Fig. 6.

Fig. 6

Circuitul poate accesa 8 porturi I/O de intrare si 8 de iesire de cite 16 biti fiecare. Cind se executa o instructiune IN este generat semnalul DEN pentru transferul datelor periferic RAMdate. Instructiunea OUT activeaza semnalul WE pentru transfer memorie periferic.

2.14.

Linia BIO

Linia BIO este folosita pentru operatii de testare si de salt. Cind BIO = 0 executia instructiunii BIOZ va produce o ramificare a programului. Linia BIO este utila si pentru urmarirea starii dispozitivelor I/O. Ea poate fi utilizata ca alternativa la sistemul de intreruperi, atunci cind o anumita sectiune critica din program nu trebuie perturbata.

12

2.15.

Intreruperile

Cererea de intrerupere este activa pe tranzitia 1 0 sau pe nivelul 0 aplicat liniei de comanda INT . Cind sistemul de intreruperi este activ cererea este memorata intr-un bistabil de intrerupere. Intreruperile sint activate/ dezactivate cu EINT/ DINT si dezactivate prin reset.

3.

Setul de instructiuni

TMS 32010 poseda un set cuprinzator de instructiuni, inclusiv instructiuni pentru operatii numerice specifice algoritmilor DSP. Majoritatea instructiunilor sint codificate cu 16 biti si sint executabile intr-un singur ciclu. Numai instructiunile de ramificare si cele pentru transfer I/O sint de tip multiciclu. Procesorul este capabil sa execute pina la 5 mil. instr./sec.

3.1.

Caracteristici ale setului de instructiuni

Asupra setului de instructiuni pot fi facute urmatoarele observatii: Procesorul poseda un set complet de instructiuni de ramificare care, combinate cu

instructiuni logice si cu operatii de deplasare, permit prelucrari pe bit si de testare a bitilor pentru operatii rapide de control; TMS 32010 executa si operatii in dubla precizie (de exemplu: ADDH, ADDS); Pentru executarea multiplicarii intr-un ciclu este disponibila instructiunea MPY; Procesorul poate executa transferuri intre cele 2 spatii de memorie ( cu instructiunile

TBLR si TBLW); Cind trebuie extinsa memoria (>4 Ko.) instructiunile TBLR/TBLW servesc pentru

extinderea RAM- date. In acest caz RAM-ul de date este adresat ca un periferic I/O si accesat cu instructiunile IN si OUT. Procesorul utilizeaza 3 moduri de adresare a datelor: directa, indirecta si imediata

3.2.

Formatul instructiunilor

Procesorul foloseste urmatoarele formate de instructiuni:

13

Exemple: *) ADD 9,5 - aduna la acumulator continutul locatiei de adresa 9H deplasat cu 5

ranguri: 0000010100001001 **) ADD *+,8 - aduna la acumulator continutul definit de registrul auxiliar curent,

deplasat cu 8 ranguri la stinga: 0000100010101000. Dupa folosire, continutul registrului auxiliar este incrementat cu o unitate.

Procesorul poseda urmatoarele tipuri de instructiuni care sint listate in Tabelul 2.: instructiuni de lucru cu acumulatorul; instructiuni de lucru cu registrele auxiliare si cu pointerul de date; instructiuni de ramificare; instructiuni de lucru cu registrele T, P si de inmultire; instructiunio pentru operatii I/O si de lucru cu memoria de date instructiuni de control

4.

Facilitati de dezvoltare ale procesoarelor TMS 3201

Familia TMS 32010 contine 5 instrumente HW si SW pentru a usura dezvoltarea aplicatiilor. Fiecare rezolva o etapa specifica in procesul de implementare a aplicatiei.

4.1.

Modulul de evaluare

Modulul de evaluare- EVM TMS 32010 este un sistem "single board" care permite utilizatorului sa estimeze daca TMS 32010 satisface performantele de viteza si de timming cerute de aplicatie. EVM poate comunica cu un calculator gazda si cu un terminal cu care pot fi transferate programe catre modul, in limbaj de asamblare. EVM asambleaza si ruleaza acest cod. De asemenea EVM accepta fie cod sursa, fie cod obiect de la calculatorul gazda. Modulul este prevazut cu posibilitatea de salvare a codului intr-o memorie EPROM.

4.2.

Modulul macroasamblor/editor de legaturi

Acest modul, translateaza codul din limbaj de asamblare TMS 32010 in cod masina executabil. El permite programatorului sa foloseasca mnemonice in locul codului hexazecimal si adrese simbolice ale memoriei. Accepta macroinstructiuni si definitii in timpul asamblarilor conditionate. El permite utilizatorului sa diagnosticheze un set extins de erori. Genereaza un listing ,

14

fisierul obiect si optional, lista de referinte incrucisate. Permite realizarea modulara a programelor care pot fi ulterior legate pentru a forma programul complet. Editorul de legaturi genereaza cod relocalizabil care poate fi rulat pe simulator sau pe emulator.

4.3.

Biblioteca

Codurile obiect pot fi stocate in biblioteci si apelate la nevoie. Astfel, rutinele comune pot fi accesate de diferite programe, scurtind astfel timpul de realizare a programelor. Biblioteca de macroinstructiuni contine contine in mod curent macrodefinitiile utilizatorului si pe cele realizate de firma.

4.4.

Simulatorul

Este un pachet de programe care permite utilizatorului sa simuleze functionarea procesorului TMS 32010 pentru verificarea programelor. Modul depanare ofera posibilitatea monitorizarii starii masinii simulate in timp ce executa programul. El utilizeaza codul masina generat de macroasamblor/editor de legaturi. Fisierele I/O pot fi asociate cu adresele porturilor din instructiunile I/O pentru a simula dispozitivele I/O care vor fi cuplate la sistem. Indicatorul pentru intreruperi este setat periodic pentru a simula intreruperi. Inainte de executia programului se fixeaza puncte de intrerupere (breakpoints). In timpul executiei programului registrele interne si memoria procesorului simulat sint modificate de instructiuni si interpretate de calculatorul gazda. Executia este stopata cind apare o eroare sau la o intrerupere. Astfel pot fi examinate/modificate registrele si/sau memoria.

4.5.

Emulatorul

Este un sistem care are toate facilitatile de emulare in timp real. El permite integrarea HW/SW in mod interactiv.

5.

Exemplu de utilizare a TMS32010

Ca exemplu de dezvoltare a unei aplicatii cu procesorul TMS 32010 vom prezenta implementarea unui filtru numeric trece-jos de tip RFI cu faza liniara, realizat prin convolutie directa. Filtrul are urmatorii parametri:

frecventa de esantionare: freccenta de taiere: atenuarea la fc: atenuarea la frecventa 1.2fc:

fs= 10 kHz fc= 2 kHz -2 dB -15 dB

ondulatia in banda de trecere: 1,5 dB

15

Folosind metodele de proiectare specifice filtrelor FIR s-au calculat coeficientii filtrului, pentru N=16 coeficienti:

h(0)= -0,2302699 = h(16) h(1)= +0,1559117= h(15) h(2)= +0,2211667= h(14) h(3)= +0,1119031= h(13)

h(4)= -0,1124507= h(12) h(5)= -0,1485743= h(11) h(6)= +0,2046856= h(10) h(7)= +0,7409326= h(9) h(8)= +1,0

Ecuatia cu diferente finite corespunzatoare este:

y(n)= -0,2302699x(n) + 0,1559177x(n-1) + 0,2211667x(n-2) +.. .......- 0,2302699x(n-16)

unde x(i) sint exantioanele de intrare, iar y(i) sint cele de la iesirea filtrului. In Fig. 7 este data caracteristica filtrului, iar in Fig. 8 structura realizata cu procesorul TMS32010 folosita pentru implementare.

Fig. 7

Pentru implemenatre coeficientii filtrului sint convertiti in numere intregi, inmultindu-i cu 2(exp-15). Coeficientii sint pastrati in memoria pentru program de unde sint cititi si transferati in memoria pentru date. Structura filtrului este data in Fig. 8. Linia BIO este activata de semnalul EOC (End Of Conversion) al CAD. Pentru sincronizarea cu intrarea este folosita instructiunea BIOZ. Cit timp

16

semnalul EOC este inactiv procesorul "asteapta". Dupa citirea esantionului curent, x(n), preocesorul calculeaza valoarea iesirii, y(n), pe care o transfera la intarea CDA. Intrucit ecuatia este implementata sub forma de bucla, registrele auxiliare pot fi folosite atit ca registre de adresare cit si drept contoare. Initializind unul dintre ele cu adresa 0 a memoriei de date, el poate fi utilizat si ca contor. Pe masura ce se executa calculul datele sint rotite in memorie. La incheierea calculului se efectueaza scalarea rezultatului adunind 0,5. Programul de calcul este dat in Anexa 2.

Anexa 2 ====================================================================== WAIT: BIOZ ;Daca linia BIO =0 se executa saltul la WAIT. BIO este cuplata la linia EOC a

IN X1,PA0 ;CAD ;PA0 eate adresa portului de intrare de la CAD, iar X1este adresa la care este ;depus esantionul curent LARK AR0,CX17 LARK AR1,X17 ZAC LT *-,AR1 ;Se incarca AR0 cu adresa coeficientului CX17 (h(16)) ;Se incarca AR1 cu adresa esantionului X(17) (x(n-16)) ;Se initializeaza acumulatorul (0 acumulator) ;Transfera in T coeficientul filtrului, decrementeaza AR1 si comuta ; registrul auxiliar MPY *-,AR0 ;Inmulteste continutul lui T cu data de la adresa AR0 apoi depune rezultatul ;in P. Decrementeaza AR0 si comuta registrul auxiliar LOOP: LTD*- ,AR1 ;Transfera in T data de la adresa (AR1), aduna la acumulator continutul lui P, muta ;data de la adresa (AR1) la adresa urmatoare, decrementeaza (AR1) si schimba ;registrul auxiliar curent MPY*-,AR0 ;Inmulteste continutul lui T cu data de la adresa AR0 apoi depune rezultatul in P, ;decrementeaza AR0 si schimba registrul auxiliar BANZ LOOP APAC ;Salt daca continutul registrului auxiliar este 0 ;Aduna P la acumulator. 17

ADD ALFA,14

;ALFA este o locatie de memorie care contine data (0000...01). Deplaseaza ;constanta cu 14 ranguri la stinga si aduna la acumulator. Echivalent cu adunarea la ;acumulator a constantei de scalare 0,5

SACH Y,1

;Y este adresa locatiei care contine valoarea esantionului de iesire (cuvintul de ordin ;superior)

OUT

Y,PA1

;PA1 este adresa portului de iesire catre CDA

B WAIT

======================================================================

Tabelul 2 Setul de instructiuni al procesorului TMS32010

18

Tabelul 2 - continuare

19

20

Tabelul 2 continuare

21

S-ar putea să vă placă și

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- Carte AMP (93pag)Document93 paginiCarte AMP (93pag)Alex VladÎncă nu există evaluări

- ArhitecturiDocument9 paginiArhitecturiLucia NegruÎncă nu există evaluări

- Curs z80 NouDocument23 paginiCurs z80 NouBarbieru BarbalataÎncă nu există evaluări

- Despre PLCDocument26 paginiDespre PLCGabi100% (1)

- Recenzie La Emile Durkheim - Regulile Metodei SociologiceDocument7 paginiRecenzie La Emile Durkheim - Regulile Metodei SociologiceLavinia Benedic100% (1)

- Lucrarea de An Amperimetru DigitalDocument24 paginiLucrarea de An Amperimetru DigitalZgherea MihaiÎncă nu există evaluări

- S7 300Document0 paginiS7 300expertcontabilÎncă nu există evaluări

- PMP c01Document30 paginiPMP c01Raluca RaluÎncă nu există evaluări

- Micro ProiectDocument31 paginiMicro ProiectIustina Andreea GavriluțăÎncă nu există evaluări

- Automate ProgramabileDocument135 paginiAutomate Programabilerazvanpapadie100% (1)

- Sisteme Cu Microprocesoare ExempleDocument91 paginiSisteme Cu Microprocesoare ExempleBuzoianu StefanÎncă nu există evaluări

- Laborator Si Curs APDocument26 paginiLaborator Si Curs APBeatrice FiranÎncă nu există evaluări

- Microcontrolerul 80C51Document28 paginiMicrocontrolerul 80C51Lacatus ValentinÎncă nu există evaluări

- Sisteme Cu MicroprocesoareDocument11 paginiSisteme Cu MicroprocesoareAlecz AlexÎncă nu există evaluări

- Definirea Notiunii PLCDocument30 paginiDefinirea Notiunii PLCLoredana Loka100% (2)

- Automate ProgramabileDocument6 paginiAutomate ProgramabileEnis Muratcea100% (2)

- Proiect MincrocontrolerDocument8 paginiProiect MincrocontrolerDan CrețuÎncă nu există evaluări

- Microcontrolere PIC de La A La ZDocument165 paginiMicrocontrolere PIC de La A La ZMihai BrindusoiuÎncă nu există evaluări

- PLC OmronDocument26 paginiPLC OmronGeta IvanÎncă nu există evaluări

- ProiectDocument13 paginiProiectalin_hedesanÎncă nu există evaluări

- PMD SubiecteDocument22 paginiPMD SubiecteAdriana PadureÎncă nu există evaluări

- Teorie PMDDocument44 paginiTeorie PMDNico100% (3)

- Multiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaDocument2 paginiMultiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaCirnaROÎncă nu există evaluări

- Curs 3 Arhitectura ADSP 2181Document19 paginiCurs 3 Arhitectura ADSP 2181Sanda RuxandraÎncă nu există evaluări

- 1) Consideratii Asupra Unui Sistem DSP. Conversia Digital AnalogicaDocument3 pagini1) Consideratii Asupra Unui Sistem DSP. Conversia Digital AnalogicaCirnaROÎncă nu există evaluări

- Teorie ExamenDocument26 paginiTeorie ExamenRazvy RăzvanuÎncă nu există evaluări

- Caracteristici RISC, UltraSPARC II Si MagistraleDocument9 paginiCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoÎncă nu există evaluări

- ASC 5 Nivelul MicroprogramatDocument22 paginiASC 5 Nivelul MicroprogramatAlis Madalina EneÎncă nu există evaluări

- Arhitectura MicroprocesoarelorDocument78 paginiArhitectura MicroprocesoarelorDaniel Anton0% (1)

- Sisteme Cu MicroprocesoareDocument4 paginiSisteme Cu MicroprocesoareDiana NichiforÎncă nu există evaluări

- Sisteme Numerice de Conducere AutomataDocument16 paginiSisteme Numerice de Conducere AutomataGogea Alexandru IacobÎncă nu există evaluări

- MCT LaboratorDocument78 paginiMCT Laboratorfrankyro100% (1)

- Informatica IndustrialaDocument32 paginiInformatica Industrialajean4444Încă nu există evaluări

- Curs 8 - Micro Control Ere PIC de 8 Biti - Structura Interna Si Function AreDocument25 paginiCurs 8 - Micro Control Ere PIC de 8 Biti - Structura Interna Si Function AreDHM1305Încă nu există evaluări

- MC Lab2 RomDocument21 paginiMC Lab2 RomAdriana CarmenÎncă nu există evaluări

- Proiect 2 FINAL2Document20 paginiProiect 2 FINAL2Faryda IuseimÎncă nu există evaluări

- UPUS ExamenDocument17 paginiUPUS ExamenAlexandru PiscaÎncă nu există evaluări

- Intel 8051Document61 paginiIntel 8051Vuşcan OvidiuÎncă nu există evaluări

- Arhitectura Calculatorului DidacticDocument13 paginiArhitectura Calculatorului DidacticMădălina HapciuÎncă nu există evaluări

- Lab 1 MDocument24 paginiLab 1 Mviorica88Încă nu există evaluări

- Cobra ManualDocument10 paginiCobra ManualAlina StanciuÎncă nu există evaluări

- Proiect de Curs MIDocument17 paginiProiect de Curs MIZgherea MihaiÎncă nu există evaluări

- Laborator 1Document12 paginiLaborator 1Ceban VladislavÎncă nu există evaluări

- Microprocesoare 13Document17 paginiMicroprocesoare 13neacsu92Încă nu există evaluări

- Lab.1 MPDocument10 paginiLab.1 MPCristinaÎncă nu există evaluări

- CristianAxenie Assembly Programming Course LabDocument403 paginiCristianAxenie Assembly Programming Course LabMu sicÎncă nu există evaluări

- Microcontrolere - Laborator 1 - 2020Document17 paginiMicrocontrolere - Laborator 1 - 2020Alina FilipÎncă nu există evaluări

- Proiect: Proiectarea Unui Microprocesor RISCDocument24 paginiProiect: Proiectarea Unui Microprocesor RISCCristian PlescaÎncă nu există evaluări

- Curs SM 4Document27 paginiCurs SM 4Lavro IonutÎncă nu există evaluări

- Subiecte SMP Modificate de MineDocument7 paginiSubiecte SMP Modificate de MineGabriel VasileÎncă nu există evaluări

- 2 Magistrale PDFDocument14 pagini2 Magistrale PDFAndrei VieruÎncă nu există evaluări

- Curs ICDocument7 paginiCurs ICVanya BadanÎncă nu există evaluări

- Controller UlDocument16 paginiController UlnicuboyÎncă nu există evaluări

- SEP - Procesoare Digitale de Semnal in Virgula Mobila-Cap15Document5 paginiSEP - Procesoare Digitale de Semnal in Virgula Mobila-Cap15Mops LightÎncă nu există evaluări

- ASC 4 Nivelul Fizic SublDocument51 paginiASC 4 Nivelul Fizic SublMops LightÎncă nu există evaluări

- ASC 2 Tipuri de Arhitecturi SUBLINIATDocument47 paginiASC 2 Tipuri de Arhitecturi SUBLINIATMops LightÎncă nu există evaluări