Documente Academic

Documente Profesional

Documente Cultură

ASC 2 Tipuri de Arhitecturi SUBLINIAT

Încărcat de

Mops LightDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

ASC 2 Tipuri de Arhitecturi SUBLINIAT

Încărcat de

Mops LightDrepturi de autor:

Formate disponibile

2.

TIPURI DE ARHITECTURI

2.1. Clasificarea arhitecturii sistemelor de calcul

2.1.1. Clasificarea Flynn

Clasificarea Flynn se face dup gradul de multiplicitate al sirurilor formate

din secvente de instructiuni si secvente de date care pot fi tratate simultan din punct

de vedere hardware. Prin secven de date se ntelege un sir de date de intrare,

rezultate partiale sau rezultate temporare care sunt apelate de ctre o secven de

instruciuni.

Conform acestei clasificri exist patru tipuri de arhitecturi:

SISD (Single Instruction Stream Single Data Stream);

SIMD (Single Instruction Stream Multiple Data Stream);

MISD (Multiple Instruction Stream Single Data Stream);

MIMD (Multiple Instruction Stream Multiple Data Stream).

Pentru aceste arhitecturi exist trei tipuri de componente de sistem: UC

(unitatea central), UP (unitatea de prelucrare) si MM (modulul de memorie).

Desi sunt diferite ntre ele, toate schemele urmtoare respect succesiunea

evenimentelor din arhitectura Von Neumann: instructiunile si datele sunt extrase

din memorie, instructiunile sunt decodate de UC care trimite secventa de

instructiuni ctre UP pentru executie, datele circul ntre memorie si procesor pe o

cale bidirectional.

n continuare se va nota sirul de date cu SD si cel de instructiuni cu SI.

2.1.1.1. Arhitectura SISD

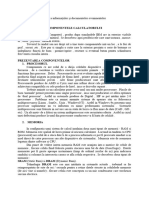

Fig. 2.1. Structura arhitecturii SISD.

Caracteristici:

instructiunile sunt executate serial, ns pot exista suprapuneri n

executie (pipeline). Majoritatea structurilor SISD rmase astzi n uz

folosesc structuri pipeline.

ARHITECTURA SISTEMELOR DE CALCUL

20

un calculator cu structur SISD poate avea mai multe elemente de

prelucrare (funcii definite), toate gsindu-se sub supervizarea aceleiasi

unice UC.

Exemple: IBM 7090, VAX 11/780, CDC 6600, IBM 360/91, CRAY.

Limitrile arhitecturii SI SD

La acest tip de arhitecturi, viteza calculatorului este determinat de perioada

ceasului. Dac perioada ceasului scade, calculatorul devine n consecint mai rapid.

Pentru a obtine un ceas mai rapid exist dou posibilitti:

calea de semnal s fie mai scurt;

tranzistorii folositi s fie mai rapizi.

Din nefericire, se pare c ambele au atins o anumit limitare din punct de

vedere tehnologic.

Scurtarea cii de semnal ar costa foarte mult. Cresterea numrului de

tranzistori pe unitatea de arie ar duce la cresterea dramatic a cldurii disipate n

exterior. Sistemele suplimentare de rcire ar costa si ele foarte mult.

Se lucreaz n prezent la fabricarea unor cipuri de joas putere (Low Power

Chips) care ar duce la scderea cldurii generate. Aceasta se poate realiza prin

mentinerea constant a densittii de energie n timp ce numrul de tranzistori pe

unitatea de arie a cipurilor ar creste.

Realizarea de tranzistori mai rapizi este, de asemenea, foarte costisitoare. n

acest scop se lucreaz la scderea rezistentei firelor prin care trece curentul.

Aluminiul este elementul folosit n 1998, dar recent s-a reusit constructia unui cip

cu fire din cupru. Concomitent cu scderea rezistentei firelor se lucreaz si la

mbunttirea izolatiei dintre fire.

Este evident c perioada ceasului nu poate fi fcut egal cu 0. n consecint,

modul secvential de tratare a operatiilor impus de arhitectura von Neumann

distruge orice sperant ntr-o viitoare crestere a vitezei calculatoarelor. Aceast

situatie este cunoscut sub denumirea de gtul sticlei lui Neumann (Neumann

Bottleneck). Pentru a sparge aceast limitare, trebuie introdus o arhitectur de tip

neserial. Alternativa este reprezentat de arhitecturile de calcul paralele.

2.1.1.2. Arhitectura SIMD

Caracteristici:

exist mai multe UP datorit sirului de date multiplu, preluat din memoria

partajat (memoria mprtit n mai multe memorii);

corespunde matricelor de microprocesoare: UP identice si supervizate de

o singur UC;

toate UP primesc instructiunile (setul unic de instructiuni) care actioneaz

asupra unor seturi de date diferite, provenite din siruri diferite de date

SD1, ..., SDn;

masinile SIMD pot efectua dou tipuri de prelucrri: pe cuvnt (word-

slice) si pe bit (bit-slice).

Tipuri de arhitecturi

21

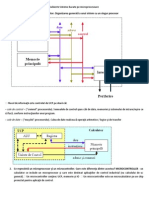

Fig. 2.2. Structura arhitecturii SIMD.

Aceste tipuri de masini lucreaz foarte bine pe seturi de date formate de

matrice de dimensiuni foarte mari atunci cnd este necesar s se execute asupra lor

aceeasi operatie. Masinile SIMD sunt eficiente si n cazul procesrii retelelor neurale.

Exemplu: CM (Connection Machine) fabricat de Thinking Machines

Company din Cambridge (Massachusetts).

Limitrile arhitecturii SI MD

Aceste tipuri de masini sunt destul de scumpe n ceea ce priveste costurile de

productie, deoarece bancurile de procesoare nu sunt componente standard. Chiar

dac numrul celor care au nevoie de astfel de masini este n continu crestere,

acestia nu sunt destul de numerosi pentru a justifica existenta unor fabrici dedicate

exclusiv productiei de SIMD-uri. n consecint, aceste masini sunt n general

Icute la comand si cost foarte mult.

1.4.1.3. Arhitectura MISD

Desi aceast masin este posibil de realizat din punct de vedere teoretic, nu a

fost niciodat fabricat n scop comercial. A fost construit n laboratoare de

cercetare, dar nu au existat clienti dornici s investeasc ntr-o astfel de arhitectur,

deoarece nu se adreseaz nici uneia dintre aplicatiile de baz.

Fig. 2.3. Structura arhitecturii MISD.

Caracteristici:

fiecare UC lucreaz cu sirul de instructiuni propriu SI1, ..., SIn;

fiecare UP lucreaz cu acelasi sir de date, care suport mai multe prelucrri;

partajare pe orizontal (un singur sir de date, mai multe siruri de instructiuni);

ARHITECTURA SISTEMELOR DE CALCUL

22

iesirea de la UP1 devine intrare pentru UP2 s.a.m.d.

Structura se numeste macro-pipeline (are doar o valoare teoretic).

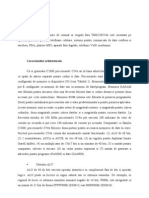

2.1.1.3. Arhitectura MIMD

Aceste tipuri de calculatoare sunt cunoscute sub denumirea de

multiprocesoare, chiar dac si masinile SIMD sunt tot multiprocesor. n

calculatoarele MIMD paralelismul este realizat prin lansarea n executie a mai

multor instructiuni n acelasi timp pe diferite seturi de date. Este evident c sunt

necesare elemente aditionale de control pentru a trimite instructiunea corect si

data care trebuie la procesorul ales, toate n acelasi timp. Cele mai multe sisteme

multiprocesor intr n aceast clas.

Fig. 2.4. Structura arhitecturii MIMD.

Avantajele arhitecturii MIMD sunt:

vitez mare de prelucrare, dac prelucrarea poate fi descompus n fire

paralele, toate procesoarele prelucrnd simultan;

ntruct procesoarele si blocurile de memorie sunt resurse de tip general,

defectarea unei unitti se poate compensa prin alocarea sarcinii de

prelucrare altei unitti (grad ridicat de tolerant la defectri);

se poate utiliza reconfigurarea dinamic pentru a face fat gradelor

variabile de ncrcare a procesoarelor.

Exemple de sisteme MIMD: C.mmp, Cm* (Carnegie Mellon University),

Ultracomputer (New York University), Cedar (University of Illinois), BBN

Butterfly, Alliant FX, CM-5 (Thinking Machine Corporation), seria Intel iPSc etc.

Sistemele MIMD se mai numesc intrinseci (propriu-zise) dac au UP

interactive: toate sirurile de date provin din acelasi spatiu de memorie adresat de

cele n procesoare (dac nu se ntmpl acest lucru spatii disjuncte ale memoriei

se spune c exist un set de n sisteme SISD independente).

Cele dou tipuri de sisteme prezentate mai sus se mai numesc shared

memory (memoria este accesat de toate procesoarele) si shared nothing (fiecare

procesor are propria memorie, propriul disc si propriul sistem de comunicatii).

Dac la un sistem MIMD intrinsec interactiunea ntre microprocesoare este

puternic, sistemul se numeste cu cuplaj strns. Legtura procesor memorie se

face prin intermediul unor magistrale de interconectare. Comunicatia si sincronizarea

ntre procesoare se realizeaz prin zone comune de memorie. Avantaj: comoditate

de programare oferit de spatiul comun de adrese (shared address space).

Tipuri de arhitecturi

23

n caz contrar, sistemul se numeste cu cuplaj slab. Legtura procesor

memorie se face prin conexiuni seriale punct-la-punct (de tip retea). Comunicatia

ntre procesoare se face prin mesaje (message passing). Fiecare procesor dispune

de memorie proprie (private memory). Avantaj: scalabilitate (posibilitate comod

de expandare). Cele mai multe sisteme comerciale sunt cu cuplaj slab.

Exemple: IBM 370/168 cuplaj slab, CRAY 2 cuplaj strns.

2.1.1.4. Sisteme cu memorie partajat (shared memory)

n cazul masinilor cu memorie partajat, masina original von Neumann a

fost extins prin includerea a ceea ce se numeste memorie cache. Aceasta este o

memorie local atasat fiecrui procesor n parte, care i permite procesorului s

aib acces rapid la propriile seturi de instructiuni si date, dar s poat accesa n

continuare memoria principal prin magistrala de memorie. Acest tip de masin se

mai numeste arhitectur cu multiprocesare simetric si este prezentat n figura 2.5.

Fig. 2.5. Arhitectura sistemelor shared memory.

Dintre sistemele mai vechi, n aceast categorie se nscrie seria IBM

RS/6000: J40, J50, R40 si R50. Modelul J40 are dou nivele de cache n loc de

unul singur. n loc s foloseasc o magistral pentru a lega diferitele procesoare cu

memoria principal, IBM a dezvoltat un asa-numit crossbar care, spre deosebire de

magistrala conventional, permite pn la patru transferuri simultane cu memoria.

Limitrile arhitecturilor MI MD cu memorie partajat

Fig. 2.6. Limitrile calculatoarelor cu memorie partajat.

ARHITECTURA SISTEMELOR DE CALCUL

24

La aceste arhitecturi, gtul sticlei (bottleneck) l reprezint magistrala de

memorie. Toate instructiunile si datele fiecrui procesor trebuie s treac prin

aceast magistral. Cnd procesoarele care folosesc aceeasi memorie sunt putine,

performantele depind liniar de numrul procesoarelor. Pe msur ce acesta creste,

mrirea performantelor este din ce n ce mai slab, asa cum rezult din figura 2.6.

Exist dou tipuri de sisteme MIMD cu memorie partajat:

cu resurse globale (Global Shared Memory):

o arhitectura UMA (Uniform Memory Access);

o arhitectura UMA cu memorii cache locale;

cu resurse distribuite (Distributed Shared Memory):

o arhitectura NUMA (Non-Uniform Memory Access);

o arhitectura COMA (Cache-Only Memory Access);

o arhitectura CC-NUMA (Cache Coherent Non-Uniform Memory Access).

A. Arhitecturile GSM (Global Shared Memory)

Calculatoarele MIMD cu spatiu unic de memorie au un cost relativ sczut si din

acest motiv se bucur de o popularitate ridicat. Acestea sunt considerate a fi sisteme

cu cuplaj strns, datorit gradului ridicat de partajare a resurselor. Functionarea

ntregului sistem paralel este coordonat de ctre un singur sistem de operare, care

se ocup de planificarea n executie a proceselor pe procesoarele disponibile n

sistem, n conditiile n care se doreste o ncrcare ct mai echilibrat a acestora.

Arhitectura UMA (Uniform Memory Access)

Memoria fizic a calculatoarelor de tip UMA este compus din mai multe

blocuri care formeaz un spatiu unic de adresare. Procesoarele acceseaz blocurile

de memorie prin intermediul retelei de interconectare (vezi figura 2.7), care poate fi

static (format din conexiuni fixe, punct-la-punct, ntre nodurile retelei) sau

dinamic (format din conexiuni variabile n timp, de tip crossbar).

Fig. 2.7. Arhitectura UMA.

Principala caracteristic a calculatoarelor UMA este c toate procesoarele au

timp de acces egal la memoria partajat. ns, tocmai de aceea, numrul

procesoarelor utilizate n cadrul sistemului paralel nu poate fi foarte mare, deoarece

cresterea numrului de procesoare din sistem atrage dup sine o probabilitate mai

mare de conflict n ceea ce priveste accesarea concurent a aceleiasi zone de

memorie. ntr-un astfel de caz, se vor nregistra timpi de asteptare care vor conduce

la o utilizare ineficient a procesoarelor si la o ncrcare neechilibrat a acestora.

Tipuri de arhitecturi

25

n plus, pentru obtinerea unor performante deosebite, reteaua de comunicatie

va trebui s ofere o lrgime de band suficient de mare, deoarece fiecare procesor

poate necesita accesul la memoria partajat, ceea ce presupune transportul datelor

solicitate din memoria comun ctre procesorul care a formulat cererea.

Arhitectura UMA cu memorii cache locale

O mbunttire adus modelului UMA o reprezint utilizarea memoriilor

cache la nivelul elementelor de procesare (vezi figura 2.8). Fiecare procesor va

avea asociat o astfel de memorie. Atunci cnd un procesor solicit date, mai nti

se verific dac aceste date se gsesc deja n memoria cache local. n caz

afirmativ, acestea se transfer foarte rapid procesorului, fr a accesa memoria

partajat. Astfel, problema conflictelor de acces concurent la spatiul unic de

memorie se rezolv, cel putin, partial. Mult mai putine cereri vor ajunge s

acceseze memoria partajat si, din acest motiv, probabilitatea de aparitie a

conflictelor devine mult mai mic.

Fig. 2.8. Arhitectura UMA cu memorii cache locale.

Utilizarea memoriilor cache presupune ns si asigurarea consistentei

acestora. n momentul n care anumite date stocate n memoria global se modific,

aceste modificri trebuie s fie semnalate tuturor memoriilor cache care stocheaz

cpii ale datelor respective. Mai mult chiar, atunci cnd se schimb continutul

datelor de la nivelul unei memorii cache este nevoie ca modificrile s fie efectuate

n toate memoriile cache care contin cpii ale datelor actualizate. Mentinerea

coerentei memoriei cache se poate realiza att prin mecanisme software, ct si prin

mecanisme hardware. Modelele cu acces neuniform la memorie ncearc s evite

dezavantajele ntlnite la calculatoarele de tip UMA.

B. Arhitecturile DSM (Distributed Shared Memory)

Reprezint sisteme cu memorie partajat, dar care este distribuit din punct

de vedere fizic. Astfel, procesoarele au asociate memorii locale care formeaz

mpreun o memorie global care poate fi accesat direct de ctre toate elementele

de procesare. Timpul de acces la locatiile de memorie nu mai este uniform, el

depinznd de localizarea fizic a datelor care se doresc a fi transferate.

ARHITECTURA SISTEMELOR DE CALCUL

26

Arhitectura NUMA (Non-Uniform Memory Access)

n cazul acestui model, memoria partajat este distribuit fizic procesoarelor

din sistem (vezi figura 2.9). Astfel, fiecare element de procesare are asociat o

memorie local. Toate aceste memorii locale formeaz un spatiu unic de adres.

Din acest motiv, timpul de acces la memorie este neuniform, deoarece accesul la

datele aflate n memoria local este foarte rapid n timp ce accesul la datele aflate

n memoria local a altor elemente de procesare va fi mult mai lent, datorit

faptului c datele respective vor fi transportate prin reteaua de comunicatie.

Fig. 2.9. Arhitectura NUMA.

Observaie. Sistemele NUMA sunt foarte asemntoare sistemelor distribuite,

din moment ce fiecare procesor dispune de o memorie local, iar toate aceste

module locale formeaz un spatiu unic de adresare.

O caracteristic important pentru masinile NUMA este factorul NUMA.

Acest factor arat diferentele de latent pentru accesarea datelor din memoria

local comparativ cu accesarea dintr-o zon care nu este local. n functie de

conexiunile sistemului, factorul NUMA poate diferi pentru diverse prti ale

masinii: accesarea datelor dintr-un nod vecin este mai rapid dect accesarea

datelor dintr-un nod mai ndeprtat pentru care este necesar traversarea unui

numr mai mare de etaje crossbar. Asadar, atunci cnd este mentionat, factorul

NUMA se refer de obicei la cele mai ndeprtate dou procesoare ale unei retele.

Arhitectura COMA (Cache-Only Memory Access)

n cazul modelului COMA, spatiul global de adrese este format din memorii

cache locale fiecrui procesor. Atunci cnd un procesor are nevoie de anumite date,

acestea sunt mai nti aduse n memoria cache de ctre controlerul de memorie,

dup care acestea vor fi accesate foarte rapid (vezi figura 2.10).

Fig. 2.10. Arhitectura COMA.

Tipuri de arhitecturi

27

Observaie. Dispare conceptul de memorie global, controlerul de memorie

avnd responsabilitatea de a ncrca n memoriile cache locale datele ce urmeaz a

fi accesate de ctre procesoare. ncrcarea datelor presupune localizarea si

transportul acestora prin intermediul retelei de interconectare. Prin folosirea

memoriilor cache locale, probabilitatea ca un procesor s acceseze majoritar date

numai din memoria local creste foarte mult.

Totusi, folosirea memoriilor cache pe post de memorii locale atrage dup

sine si o serie de probleme. Atunci cnd se ncearc aducerea unui bloc de date

ntr-o memorie cache integral ocupat, apare necesitatea mutrii unui alt bloc de

date pentru a se crea spatiul necesar memorrii noului bloc care va fi accesat de

ctre procesor. ns, datorit faptului c nu mai exist o memorie global n care s

se scrie acest bloc, va fi nevoie ca datele continute s fie mutate n memoria cache

a unui alt procesor. Aceste date ns nu vor fi niciodat accesate de ctre procesorul

care foloseste memoria respectiv, ceea ce conduce la o scdere a eficientei de

utilizare a sistemului.

n plus, operatia de transfer a blocului de date dintr-o memorie cache n alta

este si ea consumatoare de timpi de procesare, din moment ce datele trebuie s

circule prin reteaua de interconectare. Acesti timpi morti atrag dup sine o utilizare

ineficient si o ncrcare neechilibrat a procesoarelor.

O alt problem o reprezint asigurarea coerentei memoriilor cache, n

contextul n care operatiile de mutare a blocurilor devin din ce n ce mai

complicate, atunci cnd numrul de procesoare din sistem este din ce n ce mai

mare. Controlerul de memorie trebuie s asigure gestiunea nu numai a datelor care

vor fi aduse n memoriile cache, ci si a blocurilor care au fost mutate dintr-o memorie

local n alta. Din aceste motive, arhitectura COMA este tot mai rar folosit.

Arhitectura CC-NUMA (Coherent Cache NUMA)

Modelul CC-NUMA combin modul n care este construit spatiul unic de

adres la calculatoarele de tip NUMA si la cele de tip COMA. Fiecare element de

procesare al unui calculator de tip CC-NUMA dispune att de o memorie local.

ct si de o memorie cache asociat (vezi figura 2.11).

Fig. 2.11. Arhitectura CC-NUMA.

ARHITECTURA SISTEMELOR DE CALCUL

28

Ca si n cazul modelului NUMA, accesul la datele stocate n memoria local

proprie este foarte rapid. Accesarea unor date aflate n memoria local a unui alt

procesor implic aducerea acestora n memoria local proprie. Transferul de date

folosind reteaua de comunicatie atrage dup sine ntrzieri, deoarece nu este la fel

de rapid precum accesarea memoriilor locale.

Existenta memoriilor cache are ca efect reducerea traficului prin reteaua de

comunicatie. Datele solicitate de ctre un procesor sunt mai nti cutate n

memoriile locale, dup care sunt aduse n memoria cache, n cazul n care acestea

se gsesc n memoria local a unui alt procesor. La accesrile ulterioare, se va

folosi copia datelor respective stocat n memoria cache, deci nu va mai fi nevoie

ca datele s fie din nou transferate prin reteaua de interconectare.

Utilizarea memoriile cache implic necesitatea implementrii unor

mecanisme software sau hardware care s asigure consistenta memoriilor cache. La

modificarea unor date aflate n memoria local a unui procesor, este nevoie s se

actualizeze toate copiile acestor date aflate n memoriile cache. Aceste mecanisme

care asigur coerenta memoriilor cache contribuie la cresterea traficului efectuat n

cadrul retelei de interconectare.

Arhitectura CC-NUMA este utilizat de o serie de supercalculatoare foarte

cunoscute: Bull NovaScale, HP Superdome si SGI Altix.

Dezavantajele arhitecturilor DSM

Principalul dezavantaj al arhitecturilor MIMD cu memorie distribuit si cu

spatiu individual de adresare (NUMA, COMA, CC-NUMA) l reprezint

ntrzierile care pot s apar atunci cnd un procesor doreste s acceseze date aflate

n memoria local a unui alt element de procesare. Aceste ntrzieri se datoreaz

faptului c procesorul respectiv va astepta ca datele solicitate s fie transportate n

memoria sa local. Pentru minimizarea timpilor de inactivitate, procesorul n cauz

poate efectua o comutare de procese, atunci cnd procesul activ este blocat n

asteptarea datelor solicitate. n general comutarea proceselor este o operatiune

complex, implicnd costuri importante, ce pot influenta performantele sistemului.

Eficienta operatiei de comutare poate fi substantial mbunttit prin

utilizarea firelor de executie (thread-uri). Un proces poate fi mprtit n mai multe

fire de executie, care comunic ntre ele prin accesul la spatiul de adres alocat

procesului, pe care l partajeaz. Din acest motiv, firele de executie reprezint un

mecanism eficient de exploatare a concurentei programelor.

Un fir de executie reprezint cea mai mic entitate de planificare n sistemele

bazate pe thread-uri. Comutarea ntre dou fire de executie care apartin aceluiasi

proces este o operatie foarte rapid, care nu atrage dup sine costuri suplimentare

semnificative. Astfel, procesul activ este suspendat pn n momentul n care datele

solicitate au fost aduse n memoria local. n acest timp, este executat un alt fir de

executie al aceluiasi proces. Aceast comutare ntre fire de executie apartinnd

aceluiasi proces conduce la scderea timpilor de inactivitate si, implicit, la cresterea

eficientei cu care este utilizat sistemul paralel.

Calculatoarele MIMD cu memorie distribuit se numesc multicalculatoare si

reprezint sisteme cu cuplaj slab, datorit gradului redus de partajare a resurselor.

Tipuri de arhitecturi

29

Principalul avantaj al acestor sisteme l reprezint scalabilitatea, adic,

posibilitatea extinderii prin conectarea unor noi procesoare. Cresterea numrului de

procesoare nu atrage dup sine probleme legate de accesul concurent la memorie,

deoarece majoritatea apelurilor sunt ctre memoria local. ns transferul de mesaje

presupune schimburi de date care pot aglomera reteaua. Transferul de date ntre

dou procesoare este o operatie mare consumatoare de timp. Din acest motiv,

performantele retelei de interconectare pot influenta n mod hotrtor eficienta cu

care este utilizat sistemul paralel. n plus, este foarte greu ca sarcina de calcul

distribuit procesoarelor s fie echilibrat. Sistemul de operare ruleaz n fiecare

nod si, din acest motiv, ntregul sistem poate fi vzut ca fiind format din statii de

lucru care comunic prin transfer de mesaje. Complexitatea acestor sisteme este

foarte mare, datorit faptului c ntr-un nod de procesare individual se poate gsi

un simplu procesor sau un ntreg sistem de tip UMA.

Exemple de arhitecturi MI MD cu memorie partajat

Din perspectiv istoric, masinile paralele cu memorie partajat sunt de trei

categorii: bazate pe magistral (Pentium SMP, nodul IBM SP), bazate pe directoare

de tip CC-NUMA (Origin 2000) si cu spatiu de adresare global (Cray T3D, T3E).

Masinile multiprocesor din anii '60 ai secolului trecut aveau structura din

figura 2.12.a. Capacitatea de memorare sau posibilitatea de comunicare I/O se

puteau ameliora prin adugarea de module de memorie si de dispozitive I/O.

Fig. 2.12. a. Arhitectura sistemelor multiprocesor. b. Arhitectura retelei crossbar (multistage).

Cresterea capacittii de procesare se putea realiza prin adugarea de

procesoare. Aprea deja necesitatea unei interconectri a modulelor de memorie, a

procesoarelor si a legturilor cu canalele I/O. Se foloseau retele multietajate de tip

crossbar sau multistage (vezi figura 2.12.b). Memoriile cache, marea lovitur a

anilor '70, au fost de natur a influenta puternic structurile de memorare. Sistemele

de memorie scalate prin adugarea de module suplimentare aveau nevoie de

capacitate, dar si de vitez ridicat. Memoria era o surs de strangulri (bottleneck).

Introducerea memoriilor cache a schimbat aproape radical datele problemei.

2.1.1.5. Sisteme f memorie partajat (shared nothing)

n acest caz, fiecare procesor are propria lui memorie. Aceste masini sunt

practic calculatoare independente legate ntr-o retea. Fiecare calculator se mai

numeste si nod (al retelei). Arhitectura shared nothing se mai numeste cu

multiprocesare asimetric si este prezentat n figura 2.13.

ARHITECTURA SISTEMELOR DE CALCUL

30

Fig. 2.13. Arhitectura sistemelor shared nothing.

Pentru ca aceste calculatoare s lucreze bine trebuie s existe un protocol

bun de transmitere a mesajelor ntre ele. Acest protocol trebuie s fie foarte rapid si

Ir erori. IBM foloseste n acest scop protocolul Message Passing Interface (MPI)

si mai multe ci redundante care formeaz un switch de mare vitez.

Aceste noduri sunt conectate si printr-o retea conventional Ethernet din

motive de management al sistemului.

2.1.2. Clasificarea Wang

Criteriul de clasificare este n acest caz gradul de paralelism n procesarea

cuvintelor, respectiv bitilor de date. Datele pot fi configurate ntr-o matrice (vezi

figura 2.14).

Se noteaz cu n lungimea unui cuvnt si cu m numrul de cuvinte procesate

la un moment dat.

Fig. 2.14. Organizarea datelor ntr-o matrice.

Conform acestei clasificri, exist patru tipuri de arhitecturi:

WSBS (Word Serial Bit Serial). Se lucreaz pe un singur cuvnt,

fiecare cuvnt fiind prelucrat bit cu bit: n = 1, m = 1;

WSBP (Word Serial Bit Parallel): n > 1, m = 1;

WPBS (Word Parallel Bit Serial): n = 1, m > 1;

WPBP (Word Parallel Bit Parallel): n > 1, m > 1.

n cazul tipului WPBP, structura paralel este complet, corespunztoare

prelucrrii pe matrice m n.

n cazul tipului WSBP, prelucrarea este pe orizontal, iar n cazul tipului

WPBS, prelucrarea este pe vertical.

Tipuri de arhitecturi

31

2.2. Structura fizic a unui calculator secvenial

Calculatorul numeric sistem fizic, care prelucreaz automat informatia

codificat sub form de valori discrete, conform unui program, ce indic o

succesiune determinat de operatii aritmetice si logice. Sistemul de calcul este

compus din dou subsisteme principale:

subsistemul hardware (echipamente fizice componente);

subsistemul software (programele si structurile de date).

Structura de baz a calculatorului secvential, cu program memorat, stabilit

de von Neumann n 1945, este reprezentat n figura 2.15 si cuprinde cinci unitti

functionale: unitatea de intrare (UI), unitatea de memorare (M), unitatea de iesire

(UE), unitatea aritmetico-logic (UAL) si unitatea de comand (UCd).

Fig. 2.15. Masina von Neumann.

Linia continu reprezint fluxul de date si instructiuni, iar linia ntrerupt,

fluxul de comenzi si stri.

Unitatea de comand (UCda) controleaz activitatea tuturor componentelor

din sistem pe baza unei secvente de instructiuni, reprezentnd programul memorat.

Caracterul secvential al calculatorului rezult din modul de executie al

programului. Sunt necesare urmtoarele etape majore (vezi figura 2.16):

ncrcarea instructiunii IF (instruction fetch);

decodificarea instructiunii ID (instruction decoding);

ncrcarea (din memorie) a operanzilor OF (operand fetch);

executia operatiilor impuse de instructiune EX (execution).

Dup terminarea unei instructiuni, se trece la urmtoarea instructiune. Astfel,

programul este executat secvential, instructiune cu instructiune.

ARHITECTURA SISTEMELOR DE CALCUL

32

Fig. 2.16. Etapele executiei secventiale a unei instructiuni.

Unitatea aritmetico-logic (ALU) realizeaz prelucrarea informatiei preluate

din memorie, iar rezultatele se depun din nou n memorie sau sunt furnizate n

exterior. ALU realizeaz dou categorii de operatii:

aritmetice: adunare, scdere, nmultire, mprtire;

logice: SI, SAU, SAU-EXCLUSIV, NEGATIE.

Unitatea de comand, si cea aritmetico-logic, mpreun cu memoria,

formeaz unitatea central (UC sau CPU) a calculatorului.

Datele si programele sunt introduse n calculator prin intermediul unittii de

intrare, fiind apoi depuse n memorie.

2.2.1. Structuri de calculatoare paralele

Calculatoarele paralele se clasific n trei configuratii arhitecturale:

calculatoare pipeline (CPL);

calculatoare (procesoare) matriceale (CM);

calculatoare (sisteme) multiprocesor (CMP).

Un calculator pipeline utilizeaz paralelismul temporar. Procesoarele

matriceale se bazeaz pe mai multe unitti ALU sincronizate pentru a atinge

paralelismul spaial. Un sistem multiprocesor este caracterizat de paralelism

asincron, n sensul c setul de procesoare din structura sa interactioneaz si si

mpart resursele (memorii, baze de date). n acelasi timp, procesoarele matriceale

apeleaz la paralelism sincron (blocuri comandate printr-un unic semnal de ceas).

Cele patru tipuri de paralelism enuntate nu se exclud reciproc. Cele mai

multe dintre procesoarele actuale au structura intern bazat pe tehnologia pipeline

si multe dintre acestea pot fi organizate n sisteme matriceale sau multiprocesor.

Diferenta de baz dintre un procesor matriceal si un sistem multiprocesor este

aceea c unittile functionale din procesorul matriceal opereaz sincron, n timp ce

procesoarele sistemului multiprocesor functioneaz asincron. Tendintele indic

utilizarea calculatoarelor controlate prin flux de date cu procesoare algoritmice

VLSI. Aceste tipuri de calculatoare sunt caracterizate printr-o crestere masiv a

hardware-ului pentru a atinge paralelismul.

Tipuri de arhitecturi

33

2.2.1.1. Calculatoare pipeline

Executia unei instructiuni presupune patru faze majore: ncrcarea

instructiunii IF, decodarea instructiunii ID, ncrcarea operanzilor OF si

executia efectiv EX. n procesoarele non-pipeline, aceste faze se desfsoar

secvential, iar n procesoarele pipeline se desfsoar cu paralelism temporal.

Pentru procesoare complexe, faza de executie a instructiunii poate fi

partajat n suboperatii organizate dup principiul pipeline. Problemele care apar n

calculatoarele pipeline sunt datorate conflictelor de acces la memorie, salturilor si

ntreruperilor.

Datorit suprapunerii operatiilor, calculatoarele pipeline (CPL) sunt

optimizate pentru a efectua operatii de acelasi tip. Ori de cte ori se modific tipul

operatiei (instructiunii), registrele pipeline trebuie sterse si rencrcate si, ca

urmare, se consum timp suplimentar. Proiectarea CPL include: secventializarea

sarcinilor (task-urilor), prevenirea conflictelor de acces (coliziunilor), controlul

congestiei si controlul salturilor n program.

O schem functional a unui CPL este ilustrat n figura 2.17.

Fig. 2.17. Structura functional a unui calculator pipeline.

n schema de mai sus, exist dou structuri pipeline: una pentru date scalare

si una pentru date vectoriale. Faza de ncrcare a operatiilor este mprtit n dou

subfaze independente, corespunztoare operrii cu scalari sau cu vectori. Faza de

executie se desfsoar n dou procesoare distincte, asociate scalarilor sau

vectorilor.

ARHITECTURA SISTEMELOR DE CALCUL

34

Tehnica pipeline

Executia unei instructiuni este privit ca fiind alctuit din mai multe faze

(sau stagii), care se succed una dup alta si care pot fi tratate de unitti specializate,

ntr-un mod asemntor functionrii unei linii de asamblare (de ex.: de automobile).

Exemplu. Fie un sir de procese care are loc la executia unei instructiuni.

P1 1 2 3 4 5 6 7

P2 1 2 3 4 5 6

P3 1 2 3 4 5

P4 1 2 3 4

P5 1 2 3

t

Fig. 2.18. Exemplu de sir de procese la executia unei instructiuni si desfsurarea lor n timp.

Se presupune c de fiecare din aceste procese se ocup o unitate specializat.

Cnd se atinge al cincilea impuls de ceas, la toate cele cinci procese se lucreaz n

paralel; astfel se mreste de cinci ori viteza de executie. n faza ncadrat,

instructiunea 5 este n faza de ncrcare, instructiunea 4 n faza de decodare etc.

Problema este c n faza P5 poate s apar fenomenul de strangulare, pentru

c una sau mai multe instructiuni aflate ntre P1 si P5 pot s nu fie instructiuni utile

(de ex.: salt). Desi exist un paralelism n executia instructiunilor, aceasta este o

masin pipeline de tip SISD.

2.2.1.2. Calculatoare matriceale

Un procesor matriceal tipic este prezentat n figura 2.19. Exist dou unitti

functionale distincte: o unitate de control si sincronizare a elementelor de procesare

(care are ca sarcin suplimentar efectuarea operatiilor cu scalari) si o unitate de

prelucrare matriceal. Fiecare element de prelucrare (EP) reprezint un element

pasiv, adic, fr posibilitatea de a decodifica instructiuni.

ncrcarea instructiunilor si decodarea lor (fazele IF si ID) pentru unitatea de

prelucrare matriceal este efectuat de ctre unitatea de control, prin intermediul

unei retele de interconectare ntre EP. Fiecare element de prelucrare este alctuit

dintr-o unitate ALU, registre si memorie local, iar conexiunea dintre elemente este

realizat ntr-o arhitectur de tip NUMA.

Pentru o sesiune de lucru specific, unitatea de control stabileste functia

ALU pentru fiecare EP, dup care transfer operanzi din exterior ctre memoriile

locale ale EP si rezultatele de la un EP spre alt EP (utiliznd reteaua de

interconectare). Programarea CM este mult mai dificil dect programarea CPL.

Tipuri de arhitecturi

35

Fig. 2.19. Structura functional a unui calculator matriceal.

2.2.1.3. Calculatoare multiprocesor

Structur de baz a unui CMP este prezentat n figura 2.20.

Fig. 2.20. Calculator multiprocesor.

ARHITECTURA SISTEMELOR DE CALCUL

36

Notatiile din figura 2.20 sunt urmtoarele:

P1 Pn procesoare;

ML1 MLn memorii locale.

Sistemul este alctuit din mai multe procesoare care mpart resurse comune

(memorie), dar posed si resurse proprii (private), ntr-o arhitectur de tip UMA cu

memorii (cache) locale. Procesoarele functioneaz independent (asincron), dar

trebuie s comunice ntre ele.

Structura de interconectare ntre procesoare si ntre procesoare si resursele

comune determin organizarea sistemului multiprocesor. Exist trei mari categorii

de interconectri:

1. partajarea unei magistrale comune (bus);

2. utilizarea unei retele de interconectare total (crossbar);

3. utilizarea unei memorii multiport (ca memorie comun, dual).

CMP pot fi centralizate sau distribuite. Sistemele centralizate contin toate

procesoarele n acelasi sistem de calcul, spre deosebire de sistemele distribuite, n

care procesoarele pot fi fizic plasate n subsisteme diferite. Pentru sistemele

distribuite este necesar o retea de comunicatie rapid, flexibil (adaptabil) si

fiabil.

2.2.2. Mecanisme de prelucrare paralel

Aceste solutii de implementare a prelucrrii paralele sunt corelate cu

arhitecturile clasificrii Flynn n privinta solutiilor hardware, solutiile software

fiind specifice sistemelor de operare care gestioneaz intervalele de timp alocate

diferitelor aplicatii si speculnd, astfel, posibilitatea prelucrrilor paralele.

2.2.2.1. Soluii hardware de prelucrare paralel

Multiplicarea i specializarea unitilor aritmetico-logice(ALU)

Procesoarele clasice aveau o singur unitate de tip ALU. n acest fel, nu se

efectua dect o singur operatie la un moment dat. Prin multiplicarea ALU,

majoritatea functiilor pot fi distribuite ntre unittile specializate pe o anumit

functie aritmetic sau logic si pot functiona n paralel. n unele procesoare exist

dou ALU care pot lucra n paralel (o unitate pentru aritmetica n virgul fix si

alta pentru aritmetica n virgul mobil). Ideea specializrii functionale si a

distribuirii si multiplicrii ALU (numite si unitti functionale) poate fi extins att

la sistemele multiprocesor, ct si la cele matriceale. Acest mecanism constituie, de

fapt, implementarea paralelismului la sistemele SISD.

n figura 2.21 se prezint un exemplu de schem pentru figurarea acestei

solutii. Unitatea central contine 5 unitti ALU specializate pe diferite operatii,

care pot lucra n paralel.

n timp ce o instructiune este executat de o anumit unitate ALU, unitatea

de comand ncarc si decodific o alt instructiune pe care o ncredinteaz unei

alte unitti ALU s.a.m.d.

Tipuri de arhitecturi

37

Fig. 2.21. Multiplicarea ALU prin specializarea pe operatii.

Sistemul este eficient dac timpul de executie de ctre ALU a unei operatii

este mult mai mare dect timpul de ncrcare si decodificare a unei instructiuni.

Aceast conditie este, n general, ndeplinit.

Exprimarea algebric a conditiei de eficient pentru multiplicarea si

specializarea ALU este:

t

EX(ALU)

>> t

IF

+ t

ID

.

Paralelism i structur pipeline n CPU

Primele generatii de microprocesoare utilizau ALU (n special, sumatoare)

care operau cu flux de biti (serial).

Introducerea unui ALU care opereaz n paralel, pe flux de 8, 16, 32 sau 64

biti simultan (cu sumatoare, cu transport anticipat sau multiplicatoare matriceale)

duce la cresterea vitezei de prelucrare.

Arhitectura superscalar

n arhitectura superscalar, siruri de instructiuni diferite (de obicei dou,

eventual mai multe), utilizeaz resurse diferite n aceleasi stadii de executie a

instructiunilor de pe fiecare sir.

Un exemplu particular de arhitectur superscalar este prezentat n figura 2.22.

ARHITECTURA SISTEMELOR DE CALCUL

38

Fig. 2.22. Arhitectura superscalar.

Structura superscalar cu tehnic de burst (citire n rafale) este folosit

ncepnd cu microprocesorul 80486 si este corelat cu momentul introducerii n

capsula procesorului a memoriei cache de nivel 1.

Tehnica burst foloseste aceast memorie pentru a citi blocuri de instructiuni

din memoria cache, instructiuni care au fost ncrcate acolo din memoria principal

(MP) n mod secvential (vezi figura 2.23). n acest mod, se citesc dintr-o dat fie

dou, fie patru cuvinte, n functie de dimensiunea instructiunii (pe 32 sau 16 biti).

S-a folosit initial o magistral intern ntre cache si decodificatorul de instructiuni

de 64 biti, ajungndu-se n prezent la 128 de biti.

Fig. 2.23. Arhitectura superscalar cu tehnic de burst (citire n rafale).

Tipuri de arhitecturi

39

Exemplu. Schema din figura 2.24 reprezint o arhitectur superscalar cu

trei siruri de instructiuni diferite. Se execut n acelasi timp o operatie cu numere

reale si dou operatii cu numere ntregi. Fiecare unitate este de tip pipeline si poate

executa cteva operatii n diferite stagii pipeline.

Fig. 2.24. Exemplu de arhitectur superscalar cu trei unitti pipeline n paralel.

Arhitectura superpipeline

Se bazeaz pe divizarea stagiului pipeline n substagii si, deci, pe cresterea

numrul de instructiuni care sunt procesate de pipeline la un moment dat. Diviznd

fiecare stagiu n dou substagii, perioada ciclului de ceas t va fi redus la jumtate:

t/2.

La capacitate maxim, structura pipeline produce un rezultat la fiecare t/2

secunde. Pentru o arhitectur dat si setul de instructiuni aferent ei, exist un numr

optim de stagii pipeline. Dac numrul de stagii pipeline creste peste aceast limit,

se va reduce performanta global. O solutie pentru a creste viteza fr a face

compromisuri este arhitectura superscalar, prezentat anterior.

n figura 2.25, este prezentat un exemplu de executie pipeline (a),

superpipeline (b) si superscalar (c) a unei instructiuni.

Suprapunerea operaiilor CPU cu operaiile I /O

Utilizarea unor controlere I/O separate permite efectuarea n paralel a

operatiilor interne ale CPU cu operatii de transfer de date pe canalele I/O.

Exemple de controlere I/O:

controlere DMA (Direct Memory Access), care permit transferul direct de

date: memorie memorie sau memorie canale I/O, bazat pe principiul

cererii de magistral (aceasta reprezint una dintre tehnicile evoluate de

transfer de date, vezi paragraful 3.4.4.2);

procesoare specializate I/O, care lucreaz pe canale I/O cu sarcini specifice.

ARHITECTURA SISTEMELOR DE CALCUL

40

a

b

c

Fig. 2.25. Modul de operare al tehnicilor pipeline (a), superpipeline (b) si superscalar (c).

Unitate ALU vectorial

Fig. 2.26. Arhitectur SIMD cu unitate ALU vectorial.

Este o solutie de paralelism pentru sistemele SIMD, prezentat n figura 2.26.

Tipuri de arhitecturi

41

Utilizarea unui sistem ierarhizat de memorie

Memoria unui sistem de calcul trebuie s satisfac mai multe cerinte, adesea

contradictorii: capacitate mare, timp de acces mic, cost rezonabil si dimensiuni

reduse. Aceste cerinte nu pot fi ndeplinite simultan de un singur tip de memorie.

Cu tehnologia actual se pot realiza memorii de mare vitez, dar de capacitate mic

(RAM static), memorii de capacitate mare, dar de vitez medie (variante de

memorii DRAM) sau memorii de capacitate foarte mare, dar cu timp de acces

ridicat (memorii externe pe suport magnetic sau optic).

n sistemele de calcul performante, spatiul de memorare este ierarhizat pe

mai multe nivele, cu scopul de a beneficia de avantajele oferite de diverse tipuri de

memorii. Un sistem de calcul cu memorie organizat ierarhizat poate echilibra

diferentele de vitez ntre componentele sistemului (CPU, memorie, discuri) .

ntr-o astfel de arhitectur, memoria este organizat pe patru niveluri:

registrele CPU;

memoria cache (MC);

memoria principal sau operativ (MP);

memoria virtual (MV).

Registrele CPU sunt direct adresabile de ctre ALU.

Memoria cache (rapid) este cea mai apropiat de CPU, ceea ce impune ca

timpul de acces s fie mic, capacitatea fiind limitat. Aici sunt pstrate instructiunile

si datele cu probabilitatea cea mai mare de a fi utilizate ntr-o proximitate de timp.

Memoria cache reprezint un tampon ntre memoria principal si CPU.

Memoria principal sau operativ pstreaz programele si datele aferente

n curs de executie. Ea poate fi adresat n mod aleatoriu de un program utilizator.

Are o capacitate medie-mare si un timp de acces mediu. Este un tampon ntre

memoria virtual si CPU.

Memoria virtual este un concept arhitectural prin care memoria operativ

este extins peste spatiul de adresare al memoriei externe (hard disk, band

magnetic). Prin tehnicile de implementare, numite segmentare si paginare (vezi

capitolul 6), se urmresc dou aspecte esentiale:

cresterea resurselor de memorare disponibile pentru programele utilizator;

protejarea zonelor de memorie alocate modulelor de program.

Memoria virtual este util n cazul sistemelor de operare multitasking si

multiuser (Windows, Unix).

n general, tehnicile de implementare a MC si a MV sunt transparente pentru

programele utilizator. Aparent, programele de aplicatie lucreaz numai cu memoria

principal. Transferul de informatii ntre diferitele nivele de memorie se realizeaz

n mod automat, fie de ctre componente hardware specializate (unitatea de gestiune

a memoriei, MMU), fie de ctre sistemul de operare. Procesoarele recente ofer

suport hardware pentru implementarea memoriei cache si a memoriei virtuale.

Eficienta utilizrii unei arhitecturi ierarhizate de memorie se bazeaz pe

cteva principii legate de modul de utilizare a informatiilor continute n memorie.

Astfel, conform principiului localizrii referinei, adresarea locatiilor de

memorie se realizeaz ntr-o secvent repetitiv. Exist o probabilitate mare ca o

ARHITECTURA SISTEMELOR DE CALCUL

42

locatie adresat de curnd s fie adresat si ntr-un timp imediat localizare

temporar si, similar, este previzibil ca si locatiile adiacente s fie accesate n

curnd localizare spaial. Principiile localizrii temporale si spatiale sunt o

consecint a modului uzual de executie a secventelor de program.

Exemple:

un program contine bucle care presupun executia repetitiv a aceleiasi

secvente de instructiuni;

executia instructiunilor este, n majoritatea cazurilor, secvential

(succesiunea n executie), exceptie fcnd instructiunile de salt;

secventa de program (procedura) utilizeaz repetitiv aceeasi variabil sau

adreseaz repetat elemente ale unei structuri de date (tablouri, nregistrri).

Concluzie. Statistic s-a constatat c pentru majoritatea programelor este

valabil urmtoarea regul: 90% din timpul afectat unui program este utilizat

pentru executia a numai 10% din codul acestuia. Pe baza acestor observatii,

informatiile pot fi amplasate n mod dinamic pe diferite niveluri ierarhice ale

memoriei, n functie de probabilitatea de a fi utilizate.

2.2.2.2. Soluii software de prelucrare paralel

Prelucrarea pe loturi

Prelucrarea pe loturi (batch processing) presupune formarea unui fisier cu

extensia .bat si lansarea lui. Procesele au loc succesiv, iar CPU (care execut

operatiile de calcul) nu este folosit n mod eficient.

Fig. 2.19. a. Prelucrarea pe loturi. b. Multiprogramarea.

Tipuri de arhitecturi

43

Exemplu. Fie trei procese paralele, P1, P2 si P3, fiecare fiind vzut n timp

ca o succesiune de trei etape: intrare (i), calcul (c), iesire (o) (vezi figura 2.27.a).

Multiprogramarea

n acelasi interval de timp pot exista mai multe programe (procese) active n

sistemul de calcul, concurnd pentru memorie, I/O si CPU. Totusi, unele programe

sunt orientate ctre calcule (utiliznd intens CPU), n timp ce altele sunt orientate

ctre citirea/scrierea dispozitivelor I/O. Se pot astfel organiza (intercala) cele dou

clase de programe pentru a obtine un timp de prelucrare global ct mai bun. n

figura 2.27.b, cstigul de timp este notat cu A.

Intercalarea programelor permite utilizarea mai eficient a resurselor

calculatorului prin suprapunerea operatiilor I/O cu operatiile CPU. Acest mod de

organizare este gestionat de sistemul de operare (programul de supervizare). Astfel,

multiprogramarea se poate defini ca intercalarea operatiilor CPU cu operatii I/O

pentru mai multe programe.

Observaii.

1. P1, P2 si P3 pot apartine aceluiasi program sau unor programe diferite.

2. n cadrul multiprogramrii, se poate ntmpla ca un proces cu prioritate

mare s ocupe CPU un timp ndelungat si n acest fel se mpiedic

executia altor procese. Neajunsul se poate nltura folosind un sistem de

operare cu divizare n timp.

Diviziunea n timp(time sharing)

Diviziunea n timp reprezint mprtirea timpului de executie al CPU ntre

toate procesele (task-urile) active din sistemul de calcul. Cuantele de timp alocate

fiecrui proces pot fi inegale de la un proces la altul. Viteza de prelucrare poate

creste astfel mai mult dect n cazul multiprogramrii (vezi cazul particular din

figura 2.28).

Fig. 2.28. Repartizarea n timp a desfsurrii proceselor (time sharing).

ARHITECTURA SISTEMELOR DE CALCUL

44

Procesul de calcul se mparte n mai multe etape. n functie de divizarea n

intervale de timp, se poate face ca procesele s se termine aproximativ n acelasi

interval de timp (nu exist un proces dominant).

Diviziunea n timp constituie o atributie a sistemului de operare (numit, n

acest caz, sistem de operare cu diviziune n timp). Utilizarea diviziunii n timp a

programelor (sau a proceselor) n sistemele uniprocesor creeaz conceptul de

procesor virtual.

Exemplu: sisteme de calcul cu un singur procesor si mai multe terminale.

Pentru subiectul uman, rspunsul unicului procesor este suficient de rapid astfel

nct s se considere c fiecare terminal opereaz independent, ca si cum ar poseda

el nsusi procesor (utilizatorul are impresia c lucreaz singur pe calculator).

Conceptul de diviziune n timp poate fi extins n mod similar la sistemele

multiprocesor.

Observaii.

1. n cazul multiprogramrii, procesele si termin faza de calcul (n CPU),

aprnd suprapunere doar ntre operatii CPU si operatii I/O.

2. n cazul diviziunii n timp, procesele nu si termin faza de calcul nainte

de a se executa alt proces; procesele pot fi intercalate, astfel nct s se

cstige timp de executie n raport cu multiprogramarea (suprapuneri ntre

operatii CPU si operatii I/O, respectiv ntre diferite operatii I/O).

Noiunea de multithreading

Termenul de multithreading reprezint un aspect important al proiectrii

software, care necesit atentie special n constructia sistemelor mari si, n deosebi,

atunci cnd se pune problema eficientei (exprimate n termeni de vitez a

sistemului) si a performantei (exprimate n termeni de corectitudine n functionare

a sistemului). Folosind adecvat instructiunile de multithreading, se pot realiza

aplicatii optimizate.

Fiecare aplicatie sau program care ruleaz pe sistemul de operare este un

proces alctuit din unul sau mai multe fire (thread-uri). Un thread este un set de

instructiuni sau o parte anume a aplicatiei, care se execut independent n cadrul

programului sau sistemului. Thread-urile sunt entitti responsabile cu multitasking-

ul n cadrul unei singure aplicatii. De obicei, sistemul de operare (SO) se ocup cu

programarea si executarea thread-urilor.

Multithreading-ul presupune executia n paralel a mai multor procese, pentru

a mbuntti eficienta sistemului. Thread-urile sunt implementate n situatiile n

care trebuie ndeplinite mai multe sarcini simultan.

Avantajele threading-ului sunt urmtoarele:

sarcinile care cer mai mult timp de executie pot fi rulate n background;

interfata aplicatiei poate fi realizat mai atrgtor si mai simplu de

utilizat (de ex.: dup apsarea unui buton se afiseaz o bar de progres);

viteza aplicatiei poate creste;

thread-urile pot fi folositoare n situatiile n care exist decalaje ntre

anumite evenimente, putndu-se astfel elibera anumite resurse care nu

sunt necesare la un moment dat.

Tipuri de arhitecturi

45

Modelele de threading suportate de sistemele win32 sunt:

1. Modelul thread-ului unic (Single Thread Model). Acest tip de thread

presupune rularea unui singur thread la un moment dat. Restul thread-urilor trebuie

s astepte. Principalul dezavantaj al acestui tip de thread l reprezint timpii lungi

de executie pentru sarcini mici. Corespunde din punct de vedere conceptual

prelucrrii pe loturi (batch processing).

2. Modelul Apartment Thread (Single Thread Apartment Model STA). n

acest model, pot exista mai multe thread-uri care se execut n cadrul aplicatiei. n

STA, fiecare thread este izolat ntr-un apartament separat n cadrul procesului.

Fiecare proces poate avea mai multe apartamente, care pot partaja date ntre ele. n

acest caz, aplicatia este rspunztoare pentru stabilirea duratei fiecrui thread din

cadrul fiecrui apartament. Toate cererile sunt ordonate folosind Windows Message

Queue, astfel nct un singur apartament poate fi accesat la un moment dat.

Avantajul acestui model fat de modelul thread-ului unic este c se pot procesa

simultan mai multe cereri ale utilizatorului. Totusi, nu este atins nc eficienta

maxim, deoarece sarcinile se vor executa una dup alta. Corespunde din punct de

vedere conceptual multiprogramrii.

3. Modelul Multithread Apartment (Free Thread Apartment Model FTA).

Modelul Multithread Apartment presupune existenta unui singur apartament. Nu

este nevoie de ordonare, deoarece toate thread-urile apartin aceluiasi apartament si

pot partaje resursele. Aceste aplicatii se execut mai rapid dect cele care

implementeaz modelul unic sau STA, deoarece sistemul este mai putin solicitat si

poate fi optimizat s elimine timpii morti. Corespunde din punct de vedere

conceptual diviziunii n timp (time sharing).Aceste tipuri de aplicatii sunt foarte

complexe, deoarece trebuie s se asigure c thread-urile nu acceseaz simultan

aceleasi resurse (principiul pipeline). Este, astfel, absolut necesar s se furnizeze un

sistem de blocare a resurselor. Acesta trebuie implementat cu atentie, deoarece

poate conduce la blocarea total a sistemului.

Prin natura si arhitectura sa, mediul de programare Microsoft .NET

Framework este un mediu de tip multithreading.

Evaluarea performanelor. Utiliznd de n ori mai multe resurse n paralel,

un algoritm nu va rula de n ori mai repede, datorit fenomenului de timp

suplimentar (overhead), indus prin aplicarea paralelismului. Acest timp

suplimentar apare din urmtoarele cauze:

interactiunea ntre procese (transmiterea rezultatelor intermediare sau

partiale) si sincronizarea proceselor;

inactivitatea temporar (idling), care nseamn c exist procese inactive

pe anumite perioade de timp, datorit ncrcrii inegale si a asteptrii

sincronizrii;

calculele suplimentare, care nu apar n formularea serial a algoritmului.

Parametrii de intrare care contribuie la calculul performantelor sunt:

timpul de executie secvential sau serial, T

S

(timpul msurat de la

nceputul si pn la sfrsitul executiei algoritmului pe un calculator

secvential);

ARHITECTURA SISTEMELOR DE CALCUL

46

timpul de executie paralel, T

P

(timpul msurat de la nceputul executiei

si pn la terminarea ultimului subtask paralel);

numrul de procesoare, p.

Cu ajutorul acestora, se pot calcula urmtorii parametri de iesire:

suprasarcina, T

O

(Total Parallel Overhead) = diferenta dintre timpul

total de lucru nsumat al tuturor procesoarelor si timpul necesar celui mai

rapid algoritm secvential;

accelerarea, S (Speedup) = raportul dintre timpul necesar rezolvrii unei

probleme pe un procesor si timpul necesar rezolvrii aceleiasi probleme

n paralel pe p procesoare identice;

eficienta utilizrii calculatorului paralel, E = S / p;

costul, C = T

P

p, care reflect timpul total de lucru nsumat al

procesoarelor.

2.3. Categorii de calculatoare

Calculatoarele pot fi grupate n 5 categorii, n functie de structur,

dimensiuni, vitez, putere de calcul si destinatie:

microcalculatoare (ex.: computerele Apple si toate modelele de PC);

minicalculatoare (ex.: serverele IBM, SGI, Sun Microsystems etc.);

superminicalculatoare (ex.: Norsk Data Nord, Interdata, DEC VAX etc.);

mainframe-uri;

supercalculatoare.

2.3.1. Mainframe-uri

Un mainframe este un computer mare, folosit de institutii guvernamentale si

companii pentru procesarea datelor importante n statistic, recensminte, cercetare

si dezvoltare, proiectare, prognoz, planificarea productiei, tranzactii financiare etc.

Ca aspect exterior, primele mainframe-uri artau ca niste dulapuri uriase de metal.

Cu trecerea anilor, tehnologiile de fabricatie s-au dezvoltat, mrimea fizic a

mainframe-urilor a sczut, iar viteza lor de calcul a crescut foarte mult.

La nivelul anului 2008, prin mainframe se ntelege un calculator compatibil

cu modelele de tip IBM System/360 (1965). Actualmente, cel mai modern model

de la IBM este System z10. Sunt considerate mainframe-uri calculatoarele actuale

de tip: Nova (Fujitsu-Siemens), DPS (Groupe Bull), NonStop (Hewlett-Packard),

ClearPath (Unisys) si cele compatibile IBM System z9 (Hitachi, Platform Solutions).

Un mainframe poate rula sau gzdui mai multe sisteme de operare simultan,

functionnd ca mai multe masini virtuale. Un mainframe poate nlocui astfel chiar

si cteva sute de servere de dimensiuni mici (de exemplu, n aplicatii web),

reducnd costurile de ntretinere, dar mentinnd un nivel ridicat de sigurant.

Tipuri de arhitecturi

47

2.3.2. Supercalculatoare

Un supercalculator este un calculator complex cu destinatie special, compus

din mai multe procesoare care acceseaz aceeasi memorie central si care

functioneaz concomitent si coordonat, n cooperare strns, astfel nct

supercalculatorul poate atinge o performant total de calcul foarte ridicat. Modul

de operare al supercalculatoarelor este calculul paralel. Numrul de procesoare

interconectate ale unui supercalculator depseste la anumite modele chiar si

100.000.

Pentru a mentine costul unui asemenea supercalculator la un nivel rezonabil,

exist arhitecturi care fac uz de procesoare mai ieftine si mai lente, dar foarte

numeroase, grupate n asa-numite cluster-e.

Printre primele firme care au produs supercalculatoare pentru piat s-a

numrat firma Cray (modelul Cray-1 din 1976 a atins viteza de calcul de 130

Mflops). n acest domeniu, exist o list (actualizat de dou ori de an) a celor mai

rapide 500 de supercalculatoare din lume (Top 500), care se bazeaz pe testul

standardizat numit Linpack. Pe lng supercalculatoarele comerciale, exist si linia

supercalculatoarelor militare.

Exemplu: arhitectura supercalculatorului bazat pe IBM BlueGene/L.

Modelele IBM BlueGene detin momentan (2008) primele dou locuri n Top

500. Calculatorul se bazeaz pe un nou concept, care renunt la cresterea frecventei

de ceas n favoarea micsorrii componentelor, cresterii densittii acestora si

reducerii consumului de putere. Reducerea frecventei de ceas este compensat prin

mrirea gradului de paralelism, folosind un numr mai ridicat de procesoare.

Procesorul de baz este un PowerPC 440 la 700 MHz. Dou astfel de

procesoare sunt amplasate pe un cip mpreun cu o memorie cache L3 de 4 MB

partajat si 2 KB memorie cache L2 pentru fiecare procesor. Fiecare procesor are

dou porturi de ncrcare si unul de stocare ctre memoriile cache L2, functionnd

cu 8 biti/ciclu. Aceasta este jumtate din banda necesar celor dou unitti de

virgul mobil (FPU). Procesoarele au o memorie cache L1 de 32 KB pentru

instructiuni si date, n situatii favorabile atingnd performante de 2,8 Gflops/2. Se

observ c memoria cache L1 este mai mare dect L2, un lucru neobisnuit, care

permite ns atingerea unor viteze de procesare mai mari.

Arhitectura modelului IBM BlueGene/L este reprezentat n figura 2.29.

Sistemul este alctuit astfel: sunt introduse dou cipuri pe o plac cu o

memorie de 512 MB, saisprezece asemenea plci sunt plasate pe o alt plac nod,

iar 32 de plci nod sunt introduse ntr-un asa-numit cabinet. Asadar, un cabinet

contine 1024 cipuri (2048 CPU). Pentru configuratia maxim, se folosesc 64 de

cabinete cuplate, care formeaz un sistem cu 65.356 cipuri si 130.712 CPU.

n modul normal de operare, o unitate de procesare a unui cip este folosit

pentru calcule, iar cealalt, pentru sarcinile de comunicare. n acest fel,

performanta de vrf teoretic a sistemului este de 183,5 Tflops. Dac necesittile

de comunicare sunt mici, se pot folosi ambele procesoare pentru calcule, dublnd

viteza de vrf, ajungnd la 360 Tflops.

ARHITECTURA SISTEMELOR DE CALCUL

48

Fig. 2.29. Arhitectura IBM BlueGene/L.

Din punct de vedere al interconectrii, BlueGene/L posed mai multe retele:

dou retele pentru conectarea procesoarelor, o retea inel 3D si o retea arbore.

Reteaua inel este folosit pentru comunicatii generale, iar cea arbore pentru

comunicatii colective: broadcast, operatii de reducere etc. Lrgimea de band a

retelei arbore este de dou ori mai mare dect a retelei inel, ajungnd la 350 MB/s

(fat de 175 MB/s).

Performantele sistemului ajung la 280,6 Tflops pentru testul Linpack. n

urma testului, s-a efectuat rezolvarea unui sistem liniar de N = 1.769.471 ecuatii.

Eficienta rezultat a fost de 76%.

Supercalculatoarele care au la baz modelul IBM BlueGene/L

implementeaz arhitectura masiv paralel.

Aceasta const ntr-un numr de procesoare (de obicei, foarte mare de

ordinul miilor) interconectate si controlate de un singur computer central. Fiecare

CPU are memoria sa si spatiul de date propriu, care contine si o copie a sistemului

de operare. Toate blocurile CPU comunic ntre ele cu ajutorul unor interconectri

de foarte mare vitez.

Tipuri de arhitecturi

49

2.4. Exemple de arhitecturi

2.4.1. Arhitecturi uniprocesor

Se bazeaz pe cele trei componente majore: UCP, memoria, subsistemul I/O.

VAX 11/780 (superminicalculator)

Sistemul a fost produs de firma DEC. Schema de arhitectur general este

prezentat n figura 2.30. Aceasta contine:

CPU unitatea central de prelucrare, care include:

o R

0

, ..., R

15

= 16 registre generale a cte 32 biti fiecare;

o PC = contorul de program (program counter);

o ALU = unitatea aritmetic si logic;

o ML = memoria local;

MD = memorie de diagnoz;

CVM = coprocesor de virgul mobil;

MP = memoria principal (maxim 2

32

cuvinte);

C = consol;

F = floppy disk;

SBI = interfata cu magistrala sincron (Synchronous Bus Interface);

AU = adaptor unibus, cu (U) = magistral unibus;

AMB = adaptor masterbus, cu (M) = magistral masterbus.

CPU mai contine un registru de stare, care indic starea curent a

microprocesorului, a programului care se execut si a memoriei cache.

Fig. 2.30. Schema arhitecturii generale pentru VAX 11/780.

ARHITECTURA SISTEMELOR DE CALCUL

50

I BM 370/168

Fig. 2.31. Schema arhitecturii generale pentru IBM 370/168.

Schema de principiu (vezi figura 2.31) contine:

MP = memoria principal;

LSU = local storage unit (unitate de memorie local);

CM = controller memory (legtur multiport CPU memorie);

SS I/O = subsisteme de intrare-iesire (mai multe canale asincrone).

I BM RS/6000 model 250

Arhitectura simplificat este prezentat n figura 2.32.

Fig. 2.32. Schema arhitecturii generale pentru IBM RS/6000-250.

Schema de principiu contine:

PPC = PowerPC Processor Optimized With Enhanced RISC

Performance Chip;

SIMM = Small In-line Memory Modules (module de memorie);

CTRL = controler;

MCA = magistral de control si adres;

Ethernet = controler de retea.

Tipuri de arhitecturi

51

2.4.2. Arhitecturi multiprocesor

Arhitecturile multiprocesor sunt cel mai bun exemplu al tentativei de a

paraleliza un sistem de calcul. Acestea sunt de dou tipuri: cele care folosesc

procesoare multiple, discrete, pe o plac de baz sau sisteme hardware speciale si

cele care folosesc mai multe nuclee n interiorul unui singur procesor fizic.

2.4.2.1. Arhitecturi cu procesoare multiple

Arhitecturile cu procesoare multiple pot fi de dou feluri:

cu multiprocesare simetric;

cu multiprocesare asimetric.

Multiprocesarea simetric utilizeaz mai multe procesoare fizice legate

printr-o magistral de memorie partajat si suportul magnetic aferent (vezi

paragrafele 2.1.1.4 si 2.2.1.3, referitoare la sisteme cu memorie partajat shared

memory si calculatoare multiprocesor).

n cazul sistemelor cu arhitecturi de multiprocesare asimetric, fiecare

procesor are alt task. Exemple: cipseturile 3D din plcile grafice moderne si

cluster-ele de calculatoare personale (Beowulf), n care fiecare procesor are acces

numai la memoria calculatorului din care face parte (vezi paragraful 2.1.1.5,

referitor la sisteme fr memorie partajat shared nothing).

I BM RS/6000 model F50

Sistemul cuprinde ntre 1 si 4 procesoare Power PC cu cache extern si are o

magistral de 64 de biti. Memoria cache se numeste 8-way (cu 8 ci) pentru c datele

sunt grupate n seturi de cte 8 64 biti. Memoria foloseste date de 72 biti: 64 pentru

date si 8 pentru codul corector de erori (ECC = Erorr Correction Code). Procesorul

are o arhitectur de tip superscalar si poate executa pn la 4 instructiuni pe ciclu.

Caracteristici (vezi figura 2.33):

frecventa de tact: 166332 MHz, 87 MHz pentru magistrala de memorie;

32 KB cache de date, 32 KB cache de instructiuni;

magistral de date de 64 de biti si magistral de adrese de 32 de biti;

memorie de pn la 4 GB si memorie virtual de pn la 4 PB (1P = 2

52

).

Arhitectura I ntel multiprocesor

Arhitectura multiprocesor propus de firma Intel este reprezentat prin

schema din figura 2.34.

Notatiile din schem au urmtoarele semnificatii: BSP = Bootstrap Processor,

AP = Application Processor, APIC = Advanced Programmable Integrated Circuit,

ICC Bus = Interrupt Controller Communications Bus.

2.4.2.2. Arhitecturi biprocesor

Un sistem care suport dou procesoare trebuie s aib o plac de baz

adaptat pentru a servi dou CPU. n acest scop, placa de baz este dotat cu o

magistral special, a crei constructii depinde de la productor la productor, dar

care se conformeaz unor reguli generale.

ARHITECTURA SISTEMELOR DE CALCUL

52

Fig. 2.33. Schema arhitecturii generale pentru IBM RS/6000-F50.

Fig. 2.34. Schema arhitecturii Intel multiprocesor.

Astfel, cele dou CPU sunt servite de dou interfete paralele cu magistrala

principal a sistemului, iar arbitrarea traficului pe aceasta este efectuat de un

controler specializat. Accesul la magistral este multiplexat, astfel c la un anumit

moment de timp si pentru o durat bine stabilit (fix sau adaptat sarcinii curente)

accesul la magistral l are doar un singur procesor. Aceste tipuri de scheme pot

cuprinde zone de memorie cache comune (integral sau partial), iar magistrala poate

fi cu ltime variabil sau cu adaptare dinamic la cereri.

Tipuri de arhitecturi

53

Pentium I I biprocesor

Fig. 2.34. Arhitectura unui sistem biprocesor cu Pentium II.

AMD Athlon biprocesor

Este un exemplu de arhitectur biprocesor construit pe baza cipsetului 760 al

firmei AMD (vezi figura 2.35).

Fig. 2.35. Arhitectura unui sistem biprocesor cu AMD Athlon.

ARHITECTURA SISTEMELOR DE CALCUL

54

Cresterea performantelor este realizat prin utilizarea magistralei punct-la-

punct (Point-to-Point) si a modului snoop. Modul snoop permite citirea datelor de

ctre un procesor din cellalt procesor (prin intermediul Northbridge-ului),

nemaifiind necesar accesarea memoriei. Acest mod elimin tehnica prin care

datele necesare unuia din cele dou procesoare erau nscrise n memorie de ctre

primul procesor si apoi citite de ctre al doilea.

AMD K7 biprocesor

Microprocesorul AMD K7 lucreaz pe magistrala ultrarapid EV6 la

frecventa de 200 MHz. Astfel, K7 poate folosi memorii foarte rapide si cu lrgime

de band mare, cum este Rambus DRAM. Datorit suportului multiprocesor al

protocolului de magistral EV6, sistemele AMD pot fi folosite n domeniul statiilor

de lucru si al serverelor. Arhitectura EV6 permite o flexibilitate ridicat, cu

facilitti de tipul topologiei punct-la-punct si clock-forwarding. Magistralele de

date si de adrese sunt decuplate, procesorul putnd s emit cereri n timp ce

primeste date si comenzi de la logica de sistem. Tot aici sunt gestionate

transferurile cu sistemul, ctre memorie sau ctre magistralele AGP si PCI.

Schema bloc a acestei arhitecturi este prezentat n figura 2.36.

Fig. 2.36. Arhitectura unui sistem biprocesor cu AMD K7 pe magistrala EV6.

Sun SPARC I V biprocesor

Arhitectura biprocesor Sun SPARC IV este prezentat n figura 2.37.

Notatiile din schem au urmtoarele semnificatii: ECC = Error Checking/Correction

Code (cod de verificare/corectie de erori), DCSS = Dual Chip Data Switch (bloc de

alegere a cipului), SIU = System Interface Unit (unitatea de interfat cu sistemul),

MCU = Memory Control Unit (unitate de comand a memoriei).

Tipuri de arhitecturi

55

Fig. 2.37. Arhitectura Sun SPARC IV biprocesor.

Se observ c cele dou procesoare au att memorie cache comun, ct si

individual. Accesul la memoria comun se realizeaz prin intermediul unui

multiplexor, care nu permite lucrul simultan celor dou CPU cu aceasta, pentru a

preveni blocajele si erorile ce pot aprea n urma unor accesri simultane. Schema

este capabil s ruleze dou fire de executie (thread-uri) cu latente foarte mici de

scriere a cache-ului. De asemenea, accesul la magistrala principal este multiplexat,

pentru a preveni congestiile si erorile de transmisie. Strategia de gestiune a

memoriei cache este de tipul LRU (Least Recently Used cel mai putin recent

utilizat), ceea ce duce la mai multe sanse de a gsi n cache informatia necesar la

urmtoarea procesare (cache hit). Memoria acestui sistem este de tipul SDRAM.

Exist scheme care aduc mbunttiri suplimentare legate de administrarea

eficient a magistralei (prin repartizarea dinamic a duratelor de acces bazat pe

predictii si pe comportri anterioare ale proceselor care se repet la fiecare CPU etc.).

I ntel Xeon biprocesor

Sistemul este echipat cu dou procesoare Intel Xeon instalate pe o plac de

baz de tipul Supermicro P4DC6+. Aceast plac de baz este dotat cu cipsetul

i860, constituit din trei componente principale: Intel 82806AA PCI 64 Hub (Intel

P64H din figura 2.38), Intel 82860 Memory Controller Hub (MCH din figura 2.38)

si Intel 82801BA I/O Controller Hub (ICH2 din figura 2.38). Aceste blocuri

asigur un transfer foarte rapid de date att ntre procesoare, ct si ntre acestea si

memorie sau dispozitive periferice.

ARHITECTURA SISTEMELOR DE CALCUL

56

Fig. 2.38. Arhitectura sistemului Xeon biprocesor.

Pentru aceasta, arhitectura pune la dispozitie componentelor sistemului

(controlerul SCSI, sloturile PCI pe 32 sau 64 de biti) magistrale distincte, care

asigur separarea fluxurilor de date. Acest lucru este vital ntr-un server n care

schimbul de date dintre componente este realizat n flux continuu. Tot pentru o

sporire a vitezei de lucru, s-a recurs la utilizarea memoriei de tip RDRAM.

AMD Opteron biprocesor

Sistemul cu dou procesoare AMD Opteron 250 la 2,4 GHz foloseste o plac

de baz dotat cu cipsetul NVIDIA nForce Professional 2200. Noutatea acestei

configuratii este c procesoarele nu mpart aceeasi magistral pentru a accesa

memoria, ca la sistemele traditionale. n acel caz, magistrala reprezenta gtul

sticlei (bottleneck) sistemului, fiind un obstacol n calea procesrii la potentialul

maxim al CPU-urilor. Pentru a evita aceast limitare, AMD a recurs la o arhitectur

cu memorie cache neuniform, de tip ccNUMA (vezi figura 2.39).

Fiecare procesor dispune de un controler de memorie, care poate accesa o

portiune de memorie rezervat doar lui. Sunt evitate astfel suprapunerile de date si

alterarea reciproc a datelor provenite de la procesoare diferite. n plus, cele dou

CPU sunt interconectate printr-o magistral de mare vitez, de tipul HyperTransport

(tehnologie patentat de AMD), care nu are legtur direct cu memoria (spre

deosebire de un sistem clasic) si care asigur un dialog eficient ntre componente.

Cele dou procesoare pot accesa memoriile proprii cu latente foarte mici (mult

mai mici dect la sisteme traditionale), precum si memoria care nu le apartine direct,

dar cu latente mari. Aceasta nu constituie un dezavantaj, deoarece un CPU lucreaz

n mod normal doar n zona de memorie care i este repartizat. Totusi aceast

tehnologie are si un punct slab: organizarea corect a memoriei este crucial. Astfel,

arhitectura NUMA trebuie suportat att de sistemul de operare, ct si de aplicatii.

Tipuri de arhitecturi

57

Fig. 2.39. Arhitectura sistemului AMD Opteron biprocesor.

Sistemele de operare Windows XP si Windows server 2003 suport n

ntregime aceast tehnologie, optiunea activndu-se automat la detectarea unui

sistem de acest tip.

Calculatoarele biprocesor se preteaz pentru diverse aplicatii complexe, care

necesit putere de calcul. Aici intr aplicatiile grafice de modelare 3D, aplicatiile

de retea (mai ales dac sistemul este unul de tip nod coordonator de trafic sau

server pentru subretele de diverse dimensiuni) si aplicatiile specifice de prelucrare

a semnalelor n timp real. Tot ce au acestea n comun este faptul c sunt create

astfel nct s lucreze cu mai multe fire de executie simultan, conform principiilor

de calcul paralel. Aceste tipuri de algoritmi sunt create pentru a minimiza timpul de

executie foarte mare pe care l implic acele aplicatii n situatii normale.

n ultima vreme, cstig popularitate un nou tip de aplicatii care pot folosi

arhitectura biprcocesor, anume sistemele embedded. n esent, este vorba despre

conectarea n paralel, pe aceeasi plac, a dou (sau mai multe) procesoare

specializate, cu un scop bine definit, spre deosebire de calculatoarele personale,

care au scopuri multiple. De exemplu: prelucrarea unui semnal audio (codare si

decodare) si, eventual, transmiterea lui mai departe. Din aceast clas fac parte

procesoarele DSP de la firma Texas Instruments. Premisa acestor aplicatii este c

procesorul este adaptat s realizeze un numr restrns de operatii cu scopuri bine

determinate. n plus, DSP-ul este capabil s ruleze aplicatii de sine stttoare, care

s ofere interfat cu utilizatorul si suport pentru memorare si transmitere ctre alte

componente conectate la acesta. De exemplu: un subsistem care, conectat la un PC,

s codeze/decodeze fisiere audio n format mp3.

ARHITECTURA SISTEMELOR DE CALCUL

58

2.4.2.3. Arhitecturi multinucleu

Un procesor multinucleu combin dou sau mai multe nuclee ntr-un singur

cip fizic, care contine fie un circuit integrat cu toate nucleele, fie mai multe circuite

integrate interconectate. Un procesor cu mai multe nuclee implementeaz o

arhitectur de multiprocesare ntr-un singur pachet fizic. Un procesor cu toate

nucleele pe acelasi circuit integrat se numeste procesor multinucleu monolitic.

Nucleele pot partaja un singur cache de nivel nalt (de ex.: cache-ul L2

pentru procesoarele Core 2 de la Intel) sau pot avea cte un cache separat pentru

fiecare nucleu (de ex.: linia de procesoare dual-core de la AMD). Fiecare nucleu

implementeaz separat optimizri hardware, cum sunt: sisteme pipeline, executie

superscalar, extensii SSE, multithreading etc.

Un sistem cu n nuclee este eficient atunci cnd pe acesta se ruleaz n procese

(sau fire de executie) concurente si independente. Cele mai cunoscute procesoare

multinucleu sunt cele de pe piata calculatoarelor personale (Intel si AMD), precum

si cele folosite n consolele de jocuri pe televizor (de ex.: procesorul Cell folosit la

PlayStation 3 are 8 nuclee, iar Xenon folosit la Xbox360 are 3 nuclee).

Avantajele sistemelor cu procesoare multinucleu sunt:

Nucleele sunt apropiate fizic, ceea ce nseamn c semnalele trebuie s

parcurg o distant mai mic. Acestea permit procesoarelor s

interactioneze cu o frecvent mai mare dect dac ele ar fi fost separate

(dou procesoare pe o placa de baz).

Procesoarele multinucleu ofer designerilor posibilitatea de a face plcile

de baz mai mici dect pentru dou sau mai multe procesoare.

Un procesor cu dou nuclee consum mai putin dect dou procesoare

cu cte un singur nucleu, deoarece acestea necesit mai mult putere s

transmit aceleasi semnale n afara cipului,

Pretul produsului este mai redus, pachetul fizic fiind de un singur

procesor n loc de mai multe.

Dezavantajele sistemelor cu procesoare multinucleu sunt:

Desi, teoretic, dou procesoare pot dubla viteza de calcul, software-ul

trebuie optimizat pentru a beneficia de acest lucru, n functie de

posibilitatea aplicatiilor si a sistemului de operare de a crea fire de

executie (thread-uri) paralele si independente.

Integrarea a nc unui nucleu n acelasi circuit integrat pune probleme

deosebite din punct de vedere termic, deoarece, practic, acelasi pachet