Documente Academic

Documente Profesional

Documente Cultură

Cap 10

Încărcat de

micumarianTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Cap 10

Încărcat de

micumarianDrepturi de autor:

Formate disponibile

158

10. MICROCONTROLLERE

(MC)

10.1. PREZENTARE GENERAL!

10.1.1. Defini"ii

Vom defini un microcontroller pornind de la o reprezentare simplificat! a sa n

interac"iune cu mediul (Fig. 10.1.). Se va folosi n continuare prescurtarea MC pentru a

numi un microcontroller.

Intr!rile pot fi digitale sau analogice. Ca intr!ri se folosesc de regul! semnale provenind de

la comutatoarele individuale sau de la traductoare (de temperatur!, de presiune, foto,

traductoare specializate).

Ie#irile se pot face cu diode LED, pot fi relee, motoare sau sonerii. Dac! se face o

conversie D/A, ie#irea o poate constitui un difuzor.

Se poate vedea o prim! diferen"! fa"! de calculatoarele personale, unde intr!rile se fac de

regul! de la tastatur! #i ie#irile pe monitorul TV. Dac! un calculator personal este folosit

pentru a prelucra informa"ii #i a afi#a rezultatele pe monitor sau hrtie, un MC comand! un

proces.

Un element important, f!r! de care un MC nu poate func"iona, este programul (sau

programele), care se stocheaz! n memoria proprie MC.

Un MC poate fi definit ca un sistem de calcul complet pe un singur chip. Acesta include o

unitate central!, memorie, oscilator pentru tact #i dispozitive I/O. Un MC poate fi privit ca

un microprocesor care pe acela#i chip mai con"ine memorie #i o serie de interfe"e. Natura #i

complexitatea aplica"iei n care este folosit MC determin! performan"ele unit!"ii centrale,

capacitatea de memorie #i tipul interfe"elor ce compun structura intern! a MC.

Memoria

Unitatea

central!

Generator de

tact

Intr!ri

Ie#iri

Programe

MC

Fig. 10.1. Schema simplificat! a unui microcontoller

159

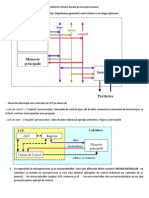

O structur! mai detaliat! se poate vedea n Fig. 10.2. unde sunt reprezentate blocurile

principale.

Privind evolu"ia istoric! a opera"iei de comand! a unui proces putem contura imaginea unui

MC. Un controller este un sistem folosit pentru a comanda #i a prelua st!ri de la un proces

sau un aspect al mediului nconjur!tor. La nceput un controller era un echipament de mari

dimensiuni. Dup! apari"ia microprocesoarelor dimensiunile controllerelor s-au redus.

Procesul de miniaturizare a continuat, toate componentele necesare unui controller au fost

integrate pe acela#i chip. S-a n!scut astfel calculatorul pe un singur chip sau

microcontrollerul. Un microcontroller este un circuit realizat pe un singur chip care con"ine

tipic:

unitatea central! CPU;

generatorul de tact (la care trebuie ad!ugat din exterior un cristal de cuar" sau n

aplica"ii mai pu"in preten"ioase, un circuit RC);

memoria RAM;

memoria ROM/PROM/EPROM/EEPROM;

dispozitive I/O seriale #i paralele;

controller de ntreruperi, controller DMA, num!r!toare/temporizatoare (timers),

covertoare A/D #i D/A, etc.;

periferice.

Memorie pentru

programe

Memorie pentru

date

Dispozitive I/O

Unitatea centrala de prelucrare

(CPU)

Oscilator

Intr!ri

digitale

Ie#iri

digitale

Bus de

date

Bus de

adrese

Reset

Fig. 10.2. Schema bloc a unui microcontoller

160

Pre"ul unui MC este redus din cauza cantit!"ilor mari n care se fabric!. Pre"ul mic al MC

aduce cu sine #i mic#orarea pre"ului sistemelor de control (se mic#oreaz! inclusiv costul

proiect!rii).

Diferen"ele dintre microprocesor #i unitatea central! a MC se atenueaz! n timp. Astfel,

marii constructori de procesoare au realizat ni#te circuite care s-ar putea numi super-

microcontrollere, a#a cum sunt Motorola 68EC300, INTEL 386EX sau IBM PowerPC

403GB, care sunt microcalculatoare pe un singur chip.

Cu un MC se poate realiza un controller integrat (Embedded Controller, EC). Un controller

integrat face parte dintr-un sistem construit cu un anumit scop, altul dect calcule generale.

Pe lng! MC, un controller integrat are nevoie de hardware suplimentar pentru a-#i

ndeplini func"ia.

Importan"a MC este dovedit! incontestabil de pia"a care este n continu! cre#tere. Astfel,

evolu"ia vnz!rilor de MC n lume se reg!se#te n tabelele 10.1. #i 10.2.

Tabel 10.1. Evolu"ia vnz!rilor MC n lume (n milioane dolari)

MC '90 '91 '92 '93 '94 '95 '96 '97 '98 '99

(esti-

mat)

'00

(esti-

mat)

4-bit 1393 1597 1596 1698 1761 1826 1849 1881 1856 1816 1757

8-bit 2077 2615 2862 3703 4689 5634 6553 7529 8423 9219 9715

16-bit 192 303 340 484 810 1170 1628 2191 2969 3678 4405

Tabel 10.2. Evolu"ia vnz!rilor MC n lume (n milioane buc!"i)

MC '90 '91 '92 '93 '94 '95 '96 '97 '98 '99

(esti-

mat)

'00

(esti-

mat)

4-bit 778 906 979 1036 1063 1110 1100 1096 1064 1025 970

8-bit 588 753 843 1073 1449 1803 2123 2374 2556 2681 2700

16-bit 22 38 45 59 106 157 227 313 419 501 585

Principalii produc!tori de microprocesoare au realizat n 1994 #i 1995 urm!toarele cifre de

afaceri (Tabel 10.3.)

Tabel 10.3. Cifre de afaceri realizate n anii 1994, 1995

microprocesoare (n milioane dolari)

Intel 10800 8036

AMD 881 992

Motorola 781 827

IBM 468 297

TI 219 202

Cyrix 210 240

Hitachi 188 66

NEC 100 82

LSI Logic 58 51

IDT 45 25

161

n prezent datele arat! modific!ri de structur!; de exemplu cifra de afaceri a AMD se

apropie de cea a lui INTEL. Cifra de afaceri, ca ordin de m!rime, era deja n anii 1994,

1995 apropiat! de cea realizat! din vnz!ri de microprocesoare (Tabel 10.4.).

Tabel 10.4. Cifre de afaceri realizate n anii 1994, 1995

microcontrollere (n milioane dolari)

Motorola 1781 1511

NEC 1421 1208

Mitsubishi 945 708

Hitachi 899 782

Intel 835 605

TI 807 534

Philips 524 345

Matsushita 500 413

Lucent (AT&T) 492 275

Toshiba 400 328

10.1.2. Arhitectura MC

Blocurile interne ale MC sunt legate ntre ele printr-o magistral! (bus) de date #i

una de adrese. M!rimea acestor magistrale constituie una dintre caracteristicile cele mai

importante ale unui MC. Prin magistrala de adrese unitatea central! (UC) selecteaz! o

loca"ie de memorie sau un dispozitiv I/O, iar pe magistrala de date se face schimbul de

informa"ie ntre UC #i memorie sau dispozitivele I/O. ntre UC #i memorie sunt transferate

att date ct #i instruc"iuni. Acestea se pot transfera pe o singur! magistral! de date sau pe

magistrale de date diferite.

Arhitectura von Neumann prevede existen"a unui bus unic folosit pentru circula"ia datelor

#i a instruc"iunilor. Cnd un controller cu o astfel de arhitectur! adreseaz! memoria, busul

de date este folosit pentru a exprima nti codul instruc"iunii, apoi pentru date, accesul fiind

realizat n 2 pa#i, deci destul de lent.

Arhitectura Harvard prevede un bus separat pentru date #i instruc"iuni. Cnd codul

instruc"iunii se afl! pe busul de instruc"iuni, pe busul de date se afl! datele instruc"iunii

anterioare. Structura MC este mai complex!, dar performan"ele de vitez! sunt mai bune.

Unitatea central! con"ine un set de registre interne, similare unor loca"ii de memorie,

folosite pentru memorarea unor date des apelate sau pentru programarea unor anumite

func"ii. Diferitele familii de MC folosesc seturi diferite de registre. Exist! ns! cteva

registre comune.

A (Accumulator) registrul acumulator care este folosit deseori pentru a stoca

un operand #i rezultatul unei opera"ii aritmetice.

PC (Program Counter) este registrul care stocheaz! adresa urm!toarei

instruc"iuni de executat. Dup! un RESET (ini"ializarea MC), registrul PC se

ncarc! dintr-o loca"ie de memorie numit! vector de reset. Aceast! loca"ie

con"ine adresa primei instruc"iuni de executat. PC este incrementat automat

dup! execu"ia unei instruc"iuni.

162

SP (Stack Pointer) con"inutul acestui registru indic! adresa curent! a stivei.

Un aspect important care determin! arhitectura unui MC este modul de programare.

Conceptul de CISC (Complex Instruction Set Computer) pe baza c!ruia sunt construite

majoritatea MC, prevede existen"a unui num!r mare de instruc"iuni (tipic >80), ceea ce

face mai u#oar! munca programatorului. Multe din instruc"iuni sunt specializate, adic! se

pot folosi doar n anumite moduri de adresare sau cu anumite registre.

Evolu"ia MC este spre arhitectura RISC (Reduced Instruction Set Computer), n cadrul

c!reia un MC are un num!r mic de instruc"iuni. Avantajele sunt un chip mai mic, cu un

num!r de pini mai mic, cu un consum mai redus #i cu o vitez! mai mare. Instruc"iunile sunt

simetrice, adic! pot fi folosite la fel n orice mod de adresare sau cu orice registru, nu au

excep"ii sau restric"ii.

n prezent un MC este cu mai mult dect arhitectur! RISC, el este cu o arhitectur! SISC

(Specific ISC). Instruc"iunile sunt specifice pentru a lucra optim cu dispozitivele I/O,

permit manipularea la nivel de bit #i sunt mai pu"ine instruc"iuni de uz general, a#a cum

ntlnim la microprocesoarele 8086, 68000 etc.

10.1.3. Memoria

MC folosesc diferite tipuri de informa"ii, care sunt stocate n diferite tipuri de

memorii. Instruc"iunile care controleaz! func"ionarea MC trebuie stocate ntr-o memorie

nevolatil!, unde informa"iile se p!streaz! #i dup! oprirea #i repornirea sursei de alimentare.

Rezultatele intermediare #i variabilele pot fi nscrise ntr-o memorie volatil!, la acestea este

important s! se poat! face scrierea /citirea rapid #i simplu n timpul func"ion!rii.

Memoria RAM (Random Access Memory) este o memorie volatil! care poate fi citit! sau

scris! de unitatea central!. Loca"iile din RAM pot fi accesibile n orice ordine. Pe chip,

memoria RAM ocup! mult loc #i implicit costurile de implementare sunt mari. De aceea un

MC include de obicei pu"in RAM. Memorie RAM static alimentat! de la baterie se

folose#te pentru stocarea nevolatil! a cantit!"ilor mari de date, la o vitez! de acces mare #i

cu un num!r nelimitat de #tergeri #i renscrieri.

Memoria ROM (Read Only Memory) este cea mai ieftin! #i simpl! memorie #i se

folose#te la stocarea programelor n faza de fabrica"ie. Unitatea central! poate citi

informa"iile, dar nu le poate modifica.

Memoria PROM (Programmable Read Only Memory) este similar! cu memoria ROM, dar

ea poate fi programat! de c!tre utilizator. Dup! posibilit!"ile de #tergere, aceast! memorie

poate fi de mai multe feluri:

Memoria EPROM (Erasable PROM) care se poate #terge prin expunere la

ultraviolete. MC cu EPROM au un mic geam de cuar" care permite ca chipul s!

fie expus la radia"ia ultraviolet!. $tergerea este neselectiv!, adic! se poate

#terge doar ntreaga informa"ie #i nu numai fragmente. Memoria poate fi #tears!

#i renscris! de un num!r finit de ori. Programarea EPROM-ului necesit! o

procedur! special!, iar MC cu EPROM au nevoie de regul! pentru nscrierea

163

EPROM-ului de o tensiune auxiliar!, de 12 V de exemplu. Unele MC au incluse

circuite de programare a memoriei EPROM, cu ajutorul c!rora unitatea central!

poate programa memoria EPROM. n timpul program!rii memoria EPROM nu

este conectat! la magistrala de date #i adrese. Unele MC sunt prev!zute cu mod

special de lucru, n care sunt v!zute din exterior ca ni#te memorii EPROM

obi#nuite #i pot fi astfel programate cu orice programator.

OTP (One Time Programmable PROM) se folose#te pentru multe serii de MC.

Memoria OTP este de fapt o memorie EPROM, dar chipul a fost capsulat ntr-o

capsul! de material plastic f!r! fereastr!, care este mult mai ieftin!. Memoria nu

se poate #terge sau reprograma. Pre"ul unui MC cu OTP este mic, viteza este

bun!, dar aplica"iile sunt lipsite de flexibilitate.

Memoria EEPROM (Electrically Erasable Programmable Read Only Memory)

poate fi #tears! electric de c!tre unitatea central!, n timpul func"ion!rii.

$tergerea este selectiv!, iar pentru renscriere trebuie parcur#i mai mul"i pa#i.

Memoria EEPROM echipeaz! multe MC, fiind ieftin!. n memoria EEPROM

se memoreaz! un mic num!r de parametri care se schimb! din timp n timp.

Memoria este lent! #i num!rul de #tergeri/scrieri este limitat (tipic 10 000).

Memoria FLASH este o memorie asem!n!toare EPROM #i EEPROM n sensul

c! poate fi #tears! #i reprogramat! n sistemul n care este folosit! (f!r! a fi

necesar un sistem dedicat). Are capacitatea unui EPROM, dar nu necesit!

fereastr! pentru #tergere. Ca #i EEPROM, memoria FLASH poate fi #tears! #i

programat! electric. Memoria FLASH nu permite #tergerea individual! de

loca"ii, utilizatorul poate s! #tearg! doar ntregul con"inut.

Stocarea programelor n memorii nevolatile permite ca MC s! fie programat f!r! a fi scos

din circuitul n care func"ioneaz! (Field Programming/Reprogramming). De exemplu la

auvehiculele comandate de MC, schimbarea tipului benzinei sau schimbarea unei legi

privitoare la poluare pot fi actualizate n programul MC f!r! ca acesta s! fie scos din

autovehicul.

n func"ie de num!rul aplica"iilor n care urmeaz! s! fie folosit MC se recomand! folosirea

MC cu ROM pentru volum mare de produc"ie (ROM se nscrie cu masc! la fabricant),

OTP pentru volum mic de produc"ie #i EPROM pentru prototipuri.

10.1.4. Dispozitive I/O

Dispozitivele I/O implementeaz! func"ii speciale degrevnd unitatea central! de

toate aspectele specifice de comand! #i control n func"ia respectiv!. Exist! o varietate

mare de dispozitive I/O; dispozitivele I/O conduc opera"ii generale de comunica"ie

(transfer serial sau paralel de date), func"ii generale de timp (num!rare de evenimente,

generare de impulsuri), opera"ii de conversie analog/numeric!, func"ii de protec"ie, func"ii

speciale de comand!, #i enumerarea poate continua. Din aceast! mare varietate, parte din

dispozitive se g!sesc n configura"ia tuturor MC sau sunt foarte des ntlnite, iar o alt!

parte de dispozitive o reg!sim doar n MC costruite pentru a optimiza aplica"ii cu un grad

mare de particularitate. n acest capitol, n continuare, vor fi prezentate dispozitive des

ntlnite n echiparea MC. n capitolele urm!toare, pe m!sur! ce vor fi prezentate exemple

de MC, vor fi descrise #i o serie de dispozitive I/O speciale ce intr! n componen"a

acestora.

164

Dispozitivele I/O sunt v!zute de unitatea central! ca porturi. Unitatea central! apeleaz!

porturile prin semnale de selec"ie construite din decodificarea magistralelor de adrese #i

control. Porturile sunt mapate fie n spa"iul de memorie, fie ntr-un spa"iu propriu. Unitatea

central! poate opera scrieri sau citiri cu porturile ca #i cu memoria.

10.1.4.1. Module de comunica!ii seriale

SCI (Serial Communications Interface) este un subsistem I/O serial indepenent, de tipul

full duplex UART asincron. SCI poate fi folosit pentru comunica"ii ntre MC #i un

terminal, un calculator PC sau un alt MC. Rata transferului este controlat! de un generator

propriu, care furnizeaz! frecven"e pentru rate de transfer standard, folosind oscilatorul MC.

SPI (Serial Peripheral Interface) este un modul serial folosit pentru a comunica sincron la

distan"e mici cu viteze de pn! la 4 Mbps. SPI este folosit pentru a comunica cu periferice

cum ar fi un simplu registru de deplasare, un sistem de afi#are LCD sau un sistem de

conversie A/D. Modulul SPI este suficient de flexibil pentru a interfa"a direct periferice cu

standarde diferite, provenite de la diver#i produc!tori. SPI poate fi folosit #i pentru a

extinde num!rul de intr!ri/ie#iri acolo unde acesta este limitat de num!rul de pini ai

capsulei MC.

SCI+ este similar cu SCI, are n plus suport pentru comunica"ii seriale sincrone. Dispune

de o ie#ire de ceas folosit! pentru a transfera date n mod sincron cu un periferic de tip SPI.

SIOP (Simple I/O Port) este o implemenatre mai simpl! a SPI.

I

2

C (Inter-Integrated Circuit) este o magistral! serial! bidirec"ional! sincron! care pune la

dispozi"ie un mod simplu #i eficient de a transfera date la 100Kbps.

10.1.4.2. Module Timer

Sistemul timer (circuit de timp) este folosit pentru a m!sura timpul #i pentru a

genera semnale cu perioade #i frecven"e dorite. Timerele nu sunt doar circuite cu func"ii de

temporizare; n modulul timer sunt implementate cteva mecanisme care pun la dispozitia

utilizatorului func"ii specifice. Mecanismul de comparare la ie#ire permite controlul unor

semnale de ie#ire; mecanismul de captur! la intrare permite monitorizarea unor semnale de

intrare; num!r!toarele interne permit generarea de referin"e de timp interne, necesare n

bucle de ntrziere, multiplexarea diferitelor sarcini software, #.a. Timerul poate fi folosit

practic pentru orice func"ie de timp, inclusiv generarea unor forme de und! sau conversii

D/A simple.

Mecanismul IC (Input Capture captur! la intrare) este folosit pentru a determina

momentul apari"iei unui eveniment sau pentru a m!sura perioada sau durata unui semnal de

intrare. Acest mecanism este folosit pentru sincronizarea cu evenimente externe.

Mecanismul OC (Output Compare comparare la ie#ire) este folosit pentru a determina o

schimbare la ie#ire la un moment de timp dorit. Mecanismul este folosit pentru a genera

spre exterior referin"e de timp.

165

Mecanismul PWM (Pulse Width Modulation modularea impulsurilor n l!"ime) este

folosit la generarea semnalelor pentru comanda motoarelor, a comutatoarelor de putere, a

convertoarelor D/A simple.

Mecanismul RTI (Real-Time Interrupt) este folosit la generarea automat! de ntreruperi

periodice. Func"ia este util! n realizarea opera"iilor I/O de tip polling, n opera"ii de

diagnoz! sau ntre"inere.

Mecanismul RTC (Real-Time Clock) este similar cu RTI, dar este folosit pentru a

implementa un ceas de timp real.

10.1.4.3. Module A/D "i D/A

Convertorul A/D este un modul implementat pe chip. Acesta e#antioneaz! periodic

semnale analogice externe #i livreaz! valorile digitale corespunz!toare. Convertoarele A/D

sunt folosite de obicei pentru a m!sura m!rimi analogice ca tura"ia unui motor,

temperatura, presiunea, nivelul lichidului, #.a.

Convertorul D/A este de asemenea un modul implementat pe chip. Acesta preia de la

unitatea central! o serie de valori binare #i produce semnalul analogic corespunz!tor. De

obicei aceast! func"ie se realizeaz! cu ajutorul modulului PWM (mai este necesar! o

filtrare extern!). O aplica"ie tipic! este comanda volumului la un aparat TV.

10.1.4.4. Module de protec!ie

COP (Computer Operating Properly) este un ceas de gard!, numit watchdog, folosit pentru

a detecta erorile de program. Folosirea ceasului de gard! este op"ionala. n cazul n care se

folose#te, programul utilizator trebuie s! reseteze periodic un registru COP; dac! nu are loc

resetarea, unitatea centrala decide c! a ap!rut o problem! n rularea programului #i

reseteaz! sistemul pentru a preveni o desf!#urare necontrolat! a programului.

LVR (Low Voltage Reset) este un circuit care monitorizeaz! tensiunea de alimentare a

unit!"ii centrale #i for"eaz! un reset daca se constat! c! aceasta este mai mic! dect un

minim predefinit.

LVI (Low Voltage Interrupt) este un circuit care monitorizeaz! tensiunea de alimentare a

unit!"ii centrale #i genereaz! o ntrerupere dac! se constat! c! aceasta este mai mic! dect

un minim predefinit. ntreruperea for"eaz! executarea unei rutine de oprire nefor"at!.

10.1.5 Sisteme de economie de energie

Pentru a realiza economia de energie, esen"ial! n cazul aliment!rii de la baterii de

exemplu, un MC poate fi comandat prin soft s! treac! n starea de a#teptare (IDLE) sau n

HALT. Prin intrarea n aceste st!ri memoria RAM nu-#i schimb! con"inutul #i ie#irile nu-#i

schimb! valorile logice.

n mod IDLE nceteaz! activitatea tuturor blocurilor func"ionale cu excep"ia oscilatorului, a

ceasului de gard! #i a ceasului pentru modul a#teptare.

166

Curentul de alimentare n aceast! stare este tipic 30% din curentul normal de func"ionare.

Din modul de a#teptare se poate ie#i prin RESET sau la un stimul exterior (o ntrerupere de

la un dispozitiv I/O). Ceasul pentru modul de a#teptare genereaz! periodic ntreruperi

pentru ca MC s! verifice starea. Dac! nu exist! cereri de activare (Wake Up), MC se

ntoarce n starea de a#teptare.

Starea de HALT este asem!n!toare cu cea de a#teptare. Capabilitatea MIWU (Multi Input

WakeUp) face ca un MC s! poat! fi trezit de una din 8 cereri de ntrerupere exterioare.

OnNow este o ini"iativ! actual! pentru modernizarea metodelor de economie de energie n

sistemele cu microprocesoare. Se inten"ioneaz! ob"inerea unui consum de energie (pentru

un calculator PC) de o treime din cel actual #i un timp de ie#ire din starea inactiv! mai mic

de 5 secunde. Informa"ii despre aceast! in"iativ! se gasesc la adresa

www.microsoft.com/hwedev/onnow.htm

10.1.6. Familii de MC

INTEL 4048 a fost primul MC ap!rut pe pia"!, avnd o structur! Harvard modificat!, cu

64-256 octe"i de RAM #i este nc! folosit n multe aplica"ii datorit! pre"ului sc!zut.

INTEL 8051 (MCS-51) este a doua genera"ie de MC #i n prezent este familia care se

vinde cel mai bine; este fabricat #i de mul"i al"i produc!tori. Acest MC are o arhitectur!

Harvard modificat! cu spa"iu de adresare diferit pentru program (<64K din care 4-8K pe

chip) #i date (<64K din care 128-256 octe"i pe chip, cu adresare indirect!). Dispozitivele

I/O au un spa"iu propriu de adresare. 8051 dispune de un procesor boolean prin care se pot

executa opera"ii complexe la nivel de bit, iar n func"ie de rezultate se pot face salturi.

Pentru 8051 exist! foarte mult soft, att contra cost ct #i gratuit.

INTEL 80C196 (MCS-96) este a treia genera"ie de MC propus! de INTEL. 80C196 este

un MC pe 16 bi"i care admite un tact pn! la 50MHz. Acest MC con"ine blocuri aritmetice

pentru nmul"ire #i mp!r"ire, lucreaz! cu 6 moduri de adresare, convertor A/D, canal de

comunica"ii serial, controller de ntreruperi cu 8 surse, pn! la 40 de porturi I/O, generator

PWM #i ceas de gard!.

INTEL 80186 #i 80188 sunt MC propuse de INTEL ca versiuni a popularelor

microprocesoare 8086 #i 8088 care au echipat primele calculatoare IBM PC XT. Pe chip

sunt incluse 2 canale DMA, 2 num!r!toare/temporizatoare, controller de ntreruperi #i bloc

de refresh pentru memoria RAM. Exist! #i multe versiuni, MC cu consum redus, cu canale

seriale etc. Un mare avantaj la folosirea acestor MC este faptul c! se pot folosi uneltele de

dezvoltare (compilatoare, asambloare etc.) de la PC-uri. Cine este familiarizat cu softul de

PC poate trece repede de etapa de nv!"are. Un alt avantaj este un spa"iu mare de adresare,

specific PC-urilor. INTEl a fabricat #i MC-ul 80386EX, o variant! a procesorului 386 care,

la puterea lui 386 mai are n plus canale seriale, canale DMA, num!r!toare/

temporizatoare, controller de ntreruperi, refresh pentru RAM dinamic, gestionarea

aliment!rii (Power Management).

167

65C02/W65C816S/W65C134S (Western Design Center). WDC a creat procesorul pe 8

bi"i 65C02 folosit n calculatoarele Apple, Commodore #i Atari urmat de procesorul pe 16

bi"i W65C816S #i un MC pe 8 bi"i avnd ca nucleu procesorul de baz! 65C02.

Motorola MC14500 a fost primul MC realizat de Motorola. Acest MC n arhitectur! RISC

avea calea de date de un bit, 16 instruc"iuni #i era furnizat ntr-o capsul! mic! (16 pini). El

a fost eliminat de pe pia"! de noile MC RISC.

Motorola 6805 se bazeaz! pe procesorul 6800 #i este asem!n!tor cu 6502 produs de WDC.

Are o arhitectur! von Neumann n care instruc"iunile, datele, dispozitivele I/O mpart

acela#i spa"iu de adresare. Stiva este limitat! la 32 de pozi"ii din cauza indicatorului de

stiv! pe 5 bi"i. Unele MC din aceast! familie includ convertoare A/D, sintetizoare de

frecven"! cu PLL, canale seriale etc.

Motorola 68HC11 (preluat #i de TOSHIBA) este un MC popular pe 8 bi"i de date #i 16

bi"i de adres!, cu o arhitectur! ca #i 6805. 68HC11 are inclus! memorie EEPROM sau

OTP, linii digitale I/O, num!r!toare/temporizatoare, convertoare A/D, generatoare PWM,

acumulator de impulsuri, canale seriale de comunica"ii sincrone #i asincrone etc.

Motorola 683xx (MC68EC300) sunt super MC de nalt! performan"! bazate pe un nucleu

cu arhitecura procesoarelor 68xx, cu o filozofie #i performan"! asem!n!toare MC INTEL

80386EX.

PIC (MicroChip) sunt primele MC RISC ap!rute, cu un num!r mic de instruc"iuni (tipic

33, fa"! de 8048 care are 90). Simplitatea arhitecturii (Harvard) duce la realizarea unui chip

de mici dimensiuni, cu pu"ini pini, consum redus, vitez! mare #i pre" mic. Aceste avantaje

au impus MC PIC pe pia"!. Exist! 3 linii de MC PIC: PIC16C5x, PIC16Cxx #i PIC17Cxx,

din care linia 16Cxx este cotat! cel mai bine pe pia"!.

COP400 (National Semiconductor) este un MC pe 4 bi"i care are 512o-2K ROM, #i 32x4-

160x4 RAM, n capsule de 20-28 de pini, cu tensiuni de alimentare 2,3V-6,0V. Sunt

echipate cu num!r!toare/temporizatoare #i magistral! MICROWIRE. Aceste MC se fabric!

n peste 60 de modele echivalente #i sunt primele MC care au un pre" sub 0,5USD/bucat!.

COP800 (National Semiconductor) este un MC de 8 bi"i care con"ine MICROWIRE,

UART, RAM, ROM, num!r!toare/temporizatoare de 16 bi"i, controller de ntreruperi,

comparator, ceas de gard!, monitor de tact, generator PWM, transmisie n infraro#u,

convertor A/D cu 8 canale cu prescalare (admite #i intr!ri diferen"iale), protec"ie la

sc!derea tensiunii de alimentare, mod de a#teptare #i HALT, un trigger SCHMITT #i

circuit de trezire cu mai multe intr!ri (Multi-Input-WakeUp). Eficien"a este dat! #i de un

set puternic de instruc"iuni, majoritatea fiind de un singur octet #i executate ntr-un singur

ciclu. Exist! #i variante pentru uz militar.

HPC (National Semiconductor) sunt MC pe 16 bi"i de mare performan"!, cu o arhitectur!

von Neumann. Unitatea central! poate executa nmul"iri #i mp!r"iri. Con"in n structur!

func"iile executate de familia COP800 avnd n plus canale seriale HDLC (High Level

Data Link Control) #i elemente DSP, la o tensiune de alimentare de 3,3V. MC din aceast!

familie au multe aplica"ii n telecomunica"ii, n sisteme de securitate, imprimante LASER,

hard discuri, frne ABS #i aplica"ii militare.

168

Proiectul PIRANHA (National Semiconductor) este un proiect de realizare a unui MC

RISC, primul MC dedicat aplica"iilor integrate. Acest MC are avantajele arhitecturii RISC,

deci pu"ine instruc"iuni, simplitate, modularitate.

Z8 (Zilog) a fost unul dintre primele MC. Modelul ini"ial avea UART, num!r!toare/

temporizatoare, DMA, 40 de linii digitale I/O, controller de ntreruperi. Modelul Z8671

avea n ROM un BASIC simplu. Modelul Z86C95 are o structur! Harvard, facilit!"i DSP

etc. Un avantaj este c! se pot folosi pentru extensii unele circuite de interfa"! din familia lui

Z80.

HD64180 (Hitachi) este un MC puternic, cu structura #i posibilit!"ile lui Z80, avnd n plus

2 canale DMA, canal de comunica"ii sincrone #i asincrone, num!r!toare/temporizatoare #i

controller de ntreruperi. Unele versiuni includ EPROM, RAM #i PIO (Programmable

Input Output). Ruleaz! instruc"iunile lui Z80, dar n mai pu"ine cicluri #i are instruc"iuni n

plus. Exist! variante care func"ioneaz! pn! la 18MHz.

TMS370 (Texas Instruments) este similar cu 8051. Con"ine RAM, ROM (OTP sau

EEPROM), 2 num!r!toare/temporizatoare de 16 bi"i, controller de ntreruperi, ceas de

gard!, generator PWM, convertor A/D cu 8 canale, SCI (port serial asincron), SPI (port

serial sincron), comparator, poate executa nmul"iri #i mp!r"iri. Tactul poate fi pn! la

20MHZ, cu 5MHz tact de magistral!.

1802 (RCA) este un MC mai vechi, cu o structur! apropiat! de un microprocesor. Este

folosit mai ales n aplica"ii spa"iale.

MuP21 (Forth) este un MC care are puterea de calcul a unui procesor INTEL 80486

(100MIPS) la un pre" mult mai mic. Are integrat un coprocesor video care gestioneaz! o

memorie video, deci se poate ata#a direct un monitor TV. Acest MC a fost creat ca s!

ruleze programul OKAD (program de proiectare VLSI), #i execut! acest lucru de 10 ori

mai repede ca un 486. Mup21 are 40 de pini.

F21 (Forth) a fost conceput pentru aplica"ii multimedia #i procesare paralel!. Viteza ajunge

la 250MIPS datorit! structurii care con"ine procesoare de prelucrare analogic! #i procesor

de interfa"! la re"eaua de calculatoare.

10.1.7. Clasificarea MC

Se pot considera multe criterii de clasificare a MC; de exemplu dup! aplica"iile n

care se folosesc, dup! interfe"ele pe care le au incluse n configura"ie, dup! furnizor etc. O

clasificare sumar! a celor mai uzuale MC, dup! compatibilitatea software, este:

MC CISC

Compatibile 8051

MOTOROLA 68xx

Compatibile x86

COP8 (National Semiconductor)

TMS370 (Texas Instruments)

ST (Thomson)

Alte arhitecturi (MC low cost) HITACI - 4bi"i, Z8 - 8 bi"i

169

MC RISC

Super H

PIC

Atmel

10.1.8. Schema bloc a unui MC

n general, orice MC are o structur! intern! organizat! n jurul unei magistrale

(Fig. 10.3.).

Unitatea central! execut! instruc"iunile pe care le prime#te prin magistrala de date din

memoria program. Structura Harvard este posibil! #i r!spndit! la MC pentru c! de regul!

instruc"iunile sunt stocate n memoria ROM, iar datele n cea RAM. Magistrala de date #i

cea de adrese pot fi separate sau multiplexate. Magistralele pot s! nu fie disponibile n

exterior (Motorola 6805) sau pot fi disponibile n exterior direct (MCS-51) sau

multiplexate (MC pe 16 sau 32 de bi"i).

Fiecare MC are un controller de ntreruperi care admite att intr!ri din exterior ct #i de la

modulele interne. Unele MC dispun de un controller DMA propriu.

Modulele I/O pot fi seriale sau paralele. Fiecare modul transfer! date cu exteriorul prin

intermediul registrului de date (RD). Modulul este comandat (configurat) de unitatea

central! prin intermediul unui registru de comenzi (RC) #i se poate citi starea modulului

prin registrul de stare (RS). Prin RS se pot genera ntreruperi. Registrele modulelor I/O pot

fi v!zute de UC ca loca"ii de memorie (la familia Motorola) sau ca dispozitive de I/O

ntr-un spa"iu de adresare separat (MCS 51). De regul!, structura de baz! a familiei con"ine

anumite interfe"e considerate foarte importante (timer, canal serial UART) #i linii I/O

Intr!ri/ie#iri

de date

Seriale/ Paralele

BUS INTERN

Unitate centrala

ALU

Registre

interne

Memorie pentru

programe

Memorie pentru

date

PORT

RD RC RS

Controller de

ntreruperi

Controller DMA

Fig. 10.3. Schema bloc a unui microcontroller

RSreg. de stare

RCreg. de comenzi

RD-reg. de date

170

grupate n porturi paralele de uz general. Pe structura de baz! se adaug! diferite tipuri de

interfe"e care folosesc n comun liniile I/O cu porturile paralele de uz general.

10.1.9. Tehnologii de fabrica"ie

CMOS (Complementary Metal Oxide Semiconductor) este cea mai r!spndit!

tehnologie. Consumul MC construit n aceast! tehnologie este mic #i permite astfel

alimentarea de la baterii. Circuitele CMOS pot fi statice sau "aproape" statice, ceea ce

nseamn! c! tactul poate fi ncetinit sau chiar oprit pentru regimul de economie de energie.

MC n tehnologie CMOS au o bun! imunitate la perturba"ii.

PMP (Post Metal Programming) permite programarea ROM-ului intern n ultimele faze de

produc"ie, dup! metalizarea final!. Uzual ROM-ul se programeaz! n etapele de nceput,

ceea ce nseamn! c! realizarea unei serii de MC poate dura 6-8 s!pt!mni. Cu tehnologia

PMP MC se pot realiza aproape n ntregime, inclusiv metalizarea #i testarea electric!

anterior program!rii ROM. Dup! programarea ROM-ului se aplic! doar stratul de pasivare.

Astfel, timpul de realizare a unei serii se reduce la 1-2 s!pt!mni.

10.1.10. Criteriile pentru alegerea unui MC

Sunt multe aspecte de care trebuie "inut seama la alegerea unui MC pentru o

anumit! aplica"ie. Alegerea unui MC potrivit poate duce la succesul proiectului, a#a cum o

alegere nepotrivit! poate duce la e#ecul proiectului. Fiecare cititor trebuie s! adapteze

aceste criterii nevoilor sale #i scalei proprii de valori.

Obiectivul urm!rit n alegerea unui MC este ob"inerea calit!"ii dorite cu un cost ct mai

sc!zut. Calit!"ile dorite nseamn! performan"!, fiabilitate, calit!"i EMC (de compatibilitate

electromagnetic! cu mediul), iar costul total include costurile cercet!rii, proiect!rii,

construc"iei, test!rii, repar!rii produsului.

n primul rnd se pune problema stabilirii func"iei pe care MC trebuie s-o ndeplineasc! n

sistem. Alegerea din catalog a unui MC trebuie f!cut! n ideea a ct mai pu"in hardware

suplimentar (din motive economice). Procesul de c!utare este dificil din cauza num!rului

foarte mare de tipuri de MC disponibile pe pia"!. Munca de c!utare este ajutat! de bazele

de date din Internet, a#a cum este baza de date de la www.questlink.com . Dup! stabilirea

MC optim se verific! pre"urile, dac! este disponibil, suportul acordat de fabricant, existen"a

uneltelor de dezvoltare, stabilitatea firmei constructoare. Un criteriu important este

posibilitatea de a fi g!sit pe pia"! (optenabilitatea), mai ales n zone n care circula"ia

m!rfurilor este destul de greoaie.

Criteriile pentru alegerea unui MC sunt, n ordinea importan"ei:

1.Posibilitatea folosirii n aplica"ia dat!

! este suficient un MC sau sunt necesare circuite suplimentare;

! liniile I/O sunt suficiente (un num!r prea mic nseamn! c! aplica"ia nu se poate face

cu acest MC, iar un num!r prea mare nseamn! un cost excesiv);

! exist! toate interfe"ele solicitate de aplica"ie: I/O serial, convertoare A/D, D/A #i nu

exist! interfe"e n plus;

! exist! capacitatea de memorare suficient!: RAM, ROM;

! MC are viteza suficient! pentru aceast! aplica"ie. Se verific! timpul necesar rul!rii

programului care trebuie s! fie mai mic dect intervalul de timp n care trebuie s!

reac"ioneze MC;

171

! alimentarea MC poate fi f!cut! din aplica"ie (este posibil ca aplica"ia s! fie

portabil!, atunci este nevoie de un MC care s! func"ioneze la 3V;

! pre"ul acestui MC este bun (acceptabil) pentru aplica"ia respectiv!.

2. Optenabilitatea MC

! trebuie s! fie disponibil n cantit!"i suficiente;

! trebuie s! fie n produc"ia actual!, dar #i n viitor pentru posibilitatea aprovizion!rii

n viitor;

! disponibilitatea unor accesorii (convertoare A/D, D/A, alimentatoare etc).

3.Disponibilitatea suportului de dezvoltare

! asambloare;

! compilatoare;

! debuggere;

! module de evaluare;

! emulatoare n circuit;

! analizoare logice;

4. Suport din partea constructorului

! documenta"ie tehnic! ;

! buletine de aplica"ii;

! service prin telefon (BBS);

! rapoarte despre prbleme de func"ionare;

! software de utilizare;

! dac! MC este folosit #i de al"i utilizatori, atunci sunt formate grupuri de lucru care

pot oferi ajutor.

5.Seriozitatea constructorului

! dac! este demonstrat! competen"a lui ;

! stabilitate #i fiabilitatea MC realizate;

! viteza de livrare;

! num!r de ani ca #i constructor #i rezultate financiare.

Un argument pentru alegerea unui tip de MC este existen"a unui modul de evaluare. Pentru

a promova propriile MC, mul"i furnizori au creat Kituri de evaluare care con"in pl!ci de

evaluare #i un soft minimal cu care se poate nv!"a utilizarea MC #i se pot pune la punct

aplica"ii. Un kit con"ine de regul! un program monitor pentru calculator PC, un program de

transfer al datelor spre placa de evaluare (prin interfa"a RS232 sau CENTRONICS), un

asamblor #i un compilator C. Toate kiturile sunt nso"ite de documenta"ie. Cteva din

modulele de evaluare sunt:

Motorola EVBU, EVB, EVM, EVS sunt echipate cu MC 68HC11.

Dallas Semiconductor DS5000TK sunt echipate cu MC Dallas din seria DS5000.

Philips #i CEIBO DS750 sunt echipate cu 87C75x, echivalent cu 8051.

American Educational Systems AES-51(8051), AES-11(68HC11), AES-88(8088)

con"in o tastatur!, un afi#aj cu LCD #i documenta"ie.

Firma Texas Instruments pune la dispozi"ia celor interesa"i un set de accesorii pentru

familia TMS370, un sistem de dezvoltare extins XDS #i unelte de dezvoltare (CDT).

Aplica"ia poate fi scris! n limbajul C, de exemplu pe un PC (utiliznd orice editor) #i

codul pentru TMS va fi generat de link editor. Codul poate ajunge la MC prin intermediul

172

interfe"ei seriale RS232. XDS analizeaz! softul creat, (chiar n domeniul timp) #i permite

punerea la punct (chiar rularea lui pas cu pas).

Exist! firme specializate n construirea unor module de evaluare cu diferite MC, a#a cum

este de exemplu PHYTEC (www.phytec.de).

Fiecare furnizor de MC pune la dispozi"ia clien"ilor un Kit de start (Starter Kit), care este

un instrument foarte valoros pentru a putea ncepe lucrul cu un anumit tip de MC. Kit-ul de

start con"ine o plac! cu soclu #i hard-ul aferent pentru programarea ini"ial! a MC, uneori

programarea EPROM-ului, interfa"a #i cablul de leg!tur! la PC, documenta"ie #i programe

(asamblor, link editor, debugger) dar nu con"ine de regul! un MC. Pre"ul unui astfel de Kit

porne#te de la 100USD (www.schuricht.de , www.farnell.com ).

Un alt argument pentru alegerea unui MC este comoditatea folosirii lui. Unele MC, a#a

cum este Motorola 68HC11A8P1 are nscris n ROM un program monitor (numit Buffalo).

Pentru punerea n func"iune este nevoie doar de o leg!tur! serial! RS232 cu un PC (este

nevoie de o conversie de nivel) #i se poate lucra de pe PC cu monitorul MC, rulnd

programele n RAM-ul MC #i stocndu-le n EEPROM. Pe I exist! subprograme scrise n

Buffalo. Un alt MC, 8052AH-BASIC con"ine un BASIC. MC Dallas din seria DS5000 are

nevoie doar de un cristal pentru oscilator #i este gata de lucru. MC con"ine memorie RAM

static alimentat! de la o baterie #i programul #i datele sunt astfel nevolatile.

10.1.11. Proiectarea sistemelor cu MC n vederea siguran"ei n

exploatare

Tendin"a produc!torilor de MC de a sc!dea pre"urile duce la r!spndirea din ce n

ce mai mare a MC #i la crearea a noi #i noi aplica"ii. Mic#orarea dimensiunilor duce la

cre#terea frecven"ei de lucru. Cu ct frecven"a cre#te, cu att cre#te posibilitatea

interferen"elor electromagnetice (EMI) #i se pune problema proiect!rii n vederea

compatibilit!"ii electromagnetice (EMC).

Apar dou! categorii de probleme: aplica"ia poate genera perturba"ii (conduse sau radiate)

sau poate fi susceptibil! la perturba"ii (conduse sau radiate). Descoperirea unor probleme

de EMI n faza final! de produc"iei a aplica"iei poate fi costisitoare deoarece s-ar putea s!

fie necesar! reproiectarea aplica"iei; de aceea este necesar ca proiectarea ini"ial! s! se fac!

n vederea EMC.

Perturba"iile sunt generate de armonicile semnalelor digitale din circuit. Ele pot fi radiate

de buclele de cablaj care se comport! ca #i antene sau sunt conduse spre sursa de

alimentare. Orice cale inductiv! sau capacitiv! pe traseul acestor armonici poate provoca

vrfuri de tensiune sau c!deri de tensiune. Pentru un sistem cu MC perturba"iile sunt

generate de regul! de cablaj, deoarece circuitele integrate au dimensiuni prea mici pentru a

putea emite. Semnalul cu frecven"a cea mai mare este tactul sistemului generat cu un

circuit oscilant cu cuar". Datorit! faptului c! forma semnalului este apropiat! de forma

sinusoidal!, con"inutul de armonici este mic. Dac! tactul este adus din exterior, se impune

aten"ie m!rit! pentru a reduce buclele de circuit emisive.

Pentru un sistem care are memorii externe cuplate la MC, liniile de transfer pot fi emisive,

deoarece frecven"ele de tranzi"ie sunt mari.

173

Susceptibilitatea sistemelor cu MC este creat! de natura sincron! a MC. Un tact cu nivel

elctric insuficient poate produce o eroare. Erorile sistemelor cu MC pot fi grupate n:

1. aplica"ia are o eroare dar se corecteaz!;

2. aplica"ia are o eroare dar o ntrerupere sau un RESET corecteaz! func"ionarea;

3. aplica"ia are o eroare #i oprind #i repornind sistemul, eroarea dispare;

4. aplica"ia are o eroare permanent! datorat! unei componente defecte.

Problemele din categoria 1 #i 2 pot s! nici nu fie observate de beneficiar.

Performan"ele EMC pot fi mbun!t!"ite acordnd aten"ie deosebit! urm!toarelor aspecte de

proiectare:

desenul cablajului imprimat;

ceasul de gard!

programarea defensiv!

10.1.11.1. Cablajul imprimat

Orice perturba"ii pe liniile de alimentare pot produce ofunc"ionare defectuoas! a

sistemului. De aceea se recomand! utilizarea unui cablaj multistrat la care masa #i

alimentarea sunt plane interne. La aplica"iile cu pre" mic, o cale important! de a reduce

pre"ul este folosirea cablajului dublu placat sau chiar simplu placat. La aceste tipuri de

cablaj traseele de mas! #i +5V trebuie s! fie ct mai late pentru a avea o impedan"! ct mai

mic!. Decuplarea cu condensatoare a MC trebuie s! fie realizat! ct mai aproape de circuit.

n unele aplica"ii care trebuie s! fie foarte ieftine se folose#te alimentarea MC de la re"eaua

de c.a. f!r! transformator, cu un redresor monoalternan"! (Fig. 10.4.).

n acest caz se creeaz! o linie de mic! impedan"! spre mas! prin re"eaua de alimentare de la

V

DD

. La acest tip de alimentare se recomad! decuplarea liniilor de frecven"! nalt! spre

linia de +5V.

Un circuit critic este cel de generare a tactulului. Orice impuls parazit care apare modific!

factorul de umplere de 50% al semnalului de tact #i instruc"iunea nu se execut! corect,

circuitul ie#ind din program. O astfel de situa"ie singular! poate fi rezolvat! de ceasul de

gard! care comnad! un RESET, dup! care MC ruleaz! din nou corect. Se recomand! ca

toate componentele aferente gener!rii tactului s! fie situate ct mai aproape de circuit, iar

MC

V

DD

V

SS

Re"ea

220V

Diod! de Rez. de

redresare putere

DZ

5V 0,1

100

Mas! flotant!

Fig. 10.4. Schema simpl! de alimentare de la re"ea

174

dac! este posibil toate traseele s! fie nconjurate de un traseu lat de gard!. Se recomand! o

decuplare a cristalului la linia de cea mai mic! impedan"! (de regul! masa) cu condensatori

SMD. Se recomand! s! se p!streze o distan"! mare ntre liniilor de frecven"! mare #i

circuitul de tact.

Este de asemenea important! protec"ia pinilor de intrare, cum ar fi RESET sau IRQ. Un pin

n aer poate comuta dac! n vecin!tatea lui sunt linii de nalt! frecven"!. Se recomand!

decuplarea acestor pini cu condensatori 1-10nF ct mai aproape de circuit.

10.1.11.2. Ceasul de gard#

Folosirea ceasului de gard! este foarte util! n cre#terea siguran"ei n func"ionare.

Majoritatea MC au un ceas de gard! integrat, iar dac! nu, un ceas de gard! extern poate fi

u#or realizat cu un monostabil redeclan#abil.

Redeclan#area ceasului de gard! trebuie f!cut! n programul principal, nu n subrutine.

Pentru a putea folosi corect ceasul de gard! trebuie analizat! cu aten"ie durata normal! a

programului pe ramura cea mai lung!.

10.1.11.3. Programarea defensiv#

Prin metodele de programare defensiv! se poate mbun!t!"i mult siguran"a n

func"ionare f!r! nici un hardware suplimentar. Cteva din cele mai eficiente metode sunt:

renc!rcarea periodic! a registrelor care comand! pinii I/O #i a celor mai

importante registre. Pinii I/O sunt leg!tura MC cu exteriorul, de aceea ei sunt

supu#i perturba"iilor. Readucerea lor la nivele corecte mic#oreaz! probabilitatea

ca o perturba"ie s! se propage n circuit.

citirea repetat! a semnalelor de intrare mic#oreaz! riscul unei citiri gre#ite. De

exemplu citirea de 3 ori la rnd a unui pin care este legat la o tast!. Dac! s-a

citit aceea#i valoare de fiecare dat! se elimin! posibilitatea unei perturba"ii.

dac! exist! loca"ii n RAM nefolosite, dup! fiecare etap! de rulare a

programului se scrie un bit n RAM. nainte de rularea unei rutine critice se

verific! valoarea stocat! n RAM #i rutina se execut! doar n cazul n care

valoarea din RAM este corect!.

dac! ntr-o aplica"ie exist! memorie nefolosit!, aceasta se umple cu instruc"iuni

de salt ntr-un loc cunoscut pentru ca un salt neprev!zut n memorie datorat unei

perturba"ii s! fie anulat de saltul n locul cunoscut.

10.2. MC din familia MOTOROLA (MC cu arhitectur$ CISC)

Motorola a dezvoltat cteva tipuri de unit!"i centrale, la care s-au ata#at o

multitudine de interfe"e, ob"innd astfel foarte multe tipuri de circuite, compatibile soft.

Motorola a creat astfel posibilitatea producerii a nenum!rate variante de MC, care s!

acopere ct mai multe din aplica"iile utilizatorului, numind aceste structuri CSIC

(Customer Specified Integrated Circuit). Spre deosebire de familia 8051 unde pe nucleul

creat de INTEL, firme constructoare au dezvoltat propriile MC compatibile, Motorola a

creat o familie de MC, ob"innd astfel o unitate n diversitate.

175

Schema bloc simplificat! a unui MC din familia Motorola este dat! n Fig. 10.5.

Porturile I/O pot fi de uz general, dar liniile porturilor pot fi utilizate #i de interfe"ele

speciale. n continuare vor fi prezentate blocurile din structura MC Motorola 6805.

10.2.1. MC M68HC05

10.2.1.1 Memoria intern#

MC din familia Motorola, ca #i toate circuitele MC, sunt echipate cu memorie

RAM, ROM #i EPROM (OTP). Fiecare din memorii are o capacitate specific! fiec!rui tip

particular de circuit. Memoria poate fi format! din 176 304 octe"i de RAM, 240 octe"i de

ROM #i 7600 7744 octe"i de memorie programabil! (EPROM sau OTP); este cazul

circuitului MC68HC705C8.

Memoria RAM este folosit! pentru stocarea temporar! a datelor. n modul de lucru

bootstrap (specific MC Motorola), memoria RAM poate fi nc!rcat! cu informa"ie de tip

program prin portul SCI, urmnd ca programul s! fie executat din RAM. Memoria ROM

este folosit! pentru a stoca programe. Modulul ROM con"ine #i programul care

coordoneaz! nc!rcarea RAM prin portul SCI. Memoria EPROM (OTP), ca #i memoria

ROM, con"ine programe #i variabile specifice aplica"iei cu diferen"a c! acestea sunt

nscrise de utilizator, nu de fabricant.

n acela#i spa"iu de adresare se afl! memoria de diferite tipuri, registre I/O #i registre de

control #i stare, privite ca loca"ii de memorie. Pentru a #ti adresa la care se afl! fiecare

element se utilizeaz! o reprezentare numit! harta memoriei. Harta memoriei pentru un

membru al familiei 6805 (MC68HC705J1A) este dat! n tabelul 10.5.

Unitatea central!

6805, 6808...

Memorie ROM,

EPROM sau OTP

Memorie RAM

Memorie

EEPROM

Magistrala de date #i

adrese

+VDD (+5V

sau +3V)

RESET

IRQ

Oscilator

Port A Port B Port C

Porturi cu func"ii

speciale, timer, CAN,

SPI, SCI

Fig. 10.5. Schema bloc a unui microcontroller Motorola

176

Tabel 10.5. Maparea memoriei la MC68HC05J1A

Con"inut Adresa (H)

Date port A 0000

Date port B 0001

Nefolosit 0002-0003

DDR pentru port A 0004

DDR pentru port B 0005

Nefolosit 0006-0007

Stare #i control pentru timer 0008

Registru num!r!tor pentru timer 0009

Stare #i control a ntreruperilor 000A

Nefolosit 000B-0011

Nefolosit 0012-0017

Registru de programare a EPROM 0018

Nefolosit 0019-001F

Nefolosit 0020-00BF

RAM utilizator sau stiv! (64 octe"i) 00C0-00FF

Nefolosit (512 octe"i) 0100-02FF

EPROM 1232 octe"i 0300-07CF

Nefolosit 30 octe"i 07D0-07ED

Test ROM 2 octe"i 07EE-07EF

Registru COP 07F0

Registru de m!#ti 07F1

Rezerva"i 07F2-07F7

Vector pentru timer (octet semnificativ) 07F8

Vector pentru timer 07F9

Vector pentru IRQ (octet semnificativ) 07FA

Vector pentru IRQ 07FB

Vector pentru SWI (octet semnificativ) 07FC

Vector pentru RESET (octet semnificativ) 07FE

Vector pentru RESET 07FF

Pentru a putea lucra cu un MC particular trebuie studiat! alocarea (maparea) memoriei din

catalog pentru acel MC, tabelul 10.5. este doar orientativ.

10.2.1.2. Unitatea central#

Unitatea central! realizeaz! prelucrarea datelor pe 8 bi"i la o frecven"! intern! de

2MHz (tact extern de 4MHz), are o magistral! de adrese de 11-14 bi"i #i con"ine registre #i

unitatea aritmetic!/logic!, Fig. 10.6. n general, la MC Motorola, bus-ul de adrese #i de

date nu este disponibil n exterior.

177

Unitatea central! are o arhitectur!cu bus unic pentru date #i instruc"iuni (von Neumann) #i

con"ine urm!toarele registre:

Registrul Acumulator (Accumulator - A) este un registru pe 8 bi"i de uz general. El nu

este afectat de Reset.

Registrul index (Index Register - X) este un registru pe 8 bi"i folosit la adres!rile indexate.

Nu este afectat de Reset.

Registrul indicator de stiv$ (Stack Pointer - SP) este un registru de 13 bi"i care con"ine

adresa urm!toarei loca"ii libere n stiv!. Dup! Reset indicatorul de stiv! devine 00FFh.

Registrul num$r$tor de program (Program Counter - PC) este un registru de 13 bi"i care

con"ine adresa urm!toarei instruc"iuni de executat. Dup! execu"ia instruc"iunii registrul este

incrementat. Un salt sau o ntrerupere determin! nc!rcarea PC cu alt! valoare dect adresa

urm!toarei loca"ii. Dup! Reset registrul PC este nc!rcat cu con"inutul loca"iilor 3FFEh #i

3FFFh (la MC68HC705J1A).

Registrul de condi"ii (Condition Code Register - CCR) este un registru de 8 bi"i (din care

sunt folosi"i 5) cu urm!toarea semnifica"ie:

Bitul 0 (LSB), (Carry/Borrow Flag) pozi"ionat dac! o adunare produce un

transport sau la o sc!dere este nevoie de mprumut.

Bitul 1 (Zero Flag), pozi"ionat dac! rezultatul unei opera"ii este zero.

Bitul 2 (Negative Flag), pozi"ionat dac! rezultatul unei opera"ii este negativ

(bitul 7 este 1).

Bitul 3 (Interrupt Mask Bit) cnd este 1 sunt invalidate ntreruperile. Dac! apare

o ntrerupere cnd acest bit este 1, ea este memorat! pn! bitul devine 0. Atunci

se salveaz! registrele UC n stiv!. Dup! Reset bitul este setat n 1 #i poate fi

pozi"ionat n 0 cu instruc"iunea CLI.

Bitul 4 (Half-Carry) este pozi"ionat cnd apare un transport de la bitul 3 spre 4

n acumulator la o opera"ie de adunare cu sau f!r! Carry. Este util la opera"ii

BCD.

Unitatea aritmetic! #i logic! realizeaz! opera"iile aritmetice #i logice definite de setul de

instruc"iuni. Multe din instruc"iunile aritmetice se bazeaz! pe algoritmul de la adunare.

Astfel, o nmul"ire este realizat! printr-un #ir de adun!ri #i deplas!ri succesive #i dureaz!

11 perioade de clock.

Unitatea central! 6805

Acumulator

Registru index

Indicator de stiv!

Num!r!tor de program (PC)

Registru de condi"ii

ALU

Unitatea aritmetic! #i logic!

Fig. 10.6. Unitatea central! 6805

178

Ini"ializarea unit!"ii centrale

Un Reset duce unitatea central! ntr-o stare determinat! (la o adres! cunoscut!). Un

Reset poate fi declan#at de o surs! intern! sau de o surs! extern! astfel:

extern, prin pinul de RESET, activ pe 0;

extern, Power On Reset (POR), la pornirea sursei de alimentare. Circuitul

POR asigur! o ntrziere de 4064 tacte de la momentul n care oscilatorul

devine activ #i dac! semnalul RESET extern este inactiv, procesorul ncepe

s! lucreze;

intern, de c!tre ceasul de gard!, Computer Operating Properly (COP).

ncercarea de a executa o instruc"iune de la o adres! ilegal!. Dac! unitatea

central! ncearc! s! execute o instruc"iune care nu este n EPROM sau RAM

se genereaz! un RESET pentru a proteja MC de scrieri sau citiri din zone

necontrolate.

10.2.1.3. Moduri de adresare

Unitatea central! folose#te 8 moduri de adresare pentru o ct mai mare flexibilitate

n utilizare:

1. adresare inerent$ - instruc"iunile nu au operand, cum este ntoarcerea din ntrerupere

(RTI) sau STOP. Instruc"iunile inerente au lungimea de un octet.

2. adresare imediat$ - instruc"iunile au un operand, care este o valoare imediat utilizabil!

ntr-o opera"ie cu acumulatorul sau cu registrul index. Instruc"iunile au doi octe"i,

primul fiind codul, iar al doilea valoarea imediat!.

3. adresare direct$ - instruc"iunile pot avea acces la primele 256 de loca"ii de memorie.

Instruc"iunile sunt pe doi octe"i, primul este codul iar al doilea este octetul cel mai pu"in

semnificativ al adresei operandului; octetul cel mai semnificativ este considerat

implicit 00h.

4. adresare extins$ - instruc"iunile sunt pe trei octe"i #i pot adresa orice loca"ie de

memorie. Primul octet este codul, al doilea este adresa (parte HIGH) iar al treilea este

adresa (partea LOW).

5. adresare indexat$ f$r$ offset - instruc"iunile au un octet #i pot avea acces la loca"ii cu

adresa variabil! din registrul index (care con"ine partea LOW a adresei). Pentru partea

HIGH se folose#te 00h, a#a nct aceesul este n zona 0000-00FFh.

6. adresare indexat$ cu offset pe 8 bi"i - instruc"iunile au doi octe"i, fiind accesibile

loca"ii cu adresa variabil! n zona primelor 511 loca"ii. Unitatea central! adun! octetul

din instruc"iune la registrul index (f!r! semn) #i se ob"ine adresa efectiv! a operandului.

Un exemplu de utilizare al acestui mod de adresare este selectarea unui elemnt k dintr-

un tabel de n elemente. Valoarea k este n registrul index, iar adresa nceputului

tabelului este al doilea octet al instruc"iunii.

7. adresare indexat$ cu offset pe 16 bi"i - instruc"iunile au trei octe"i, fiind accesibile

toate loca"iile. UC adun! f!r! semn registrul index la cei doi octe"i din instruc"iune

(primul octet dup! codul instruc"iunii este octetul HIGH) #i se ob"ine adresa efectiv! a

operandului.

8. adresare relativ$ este folosit! n instruc"iunile de salt. La un salt relativ, se adun!

(cu semn) octetul care urmeaz! dup! codul instruc"iunii la con"inutul Program Counter.

Se pot face salturi relative n gama 127 de octe"i nainte sau napoi.

179

10.2.1.4. Setul de instruc!iuni

Unitatea central! MC68HC05 are 61 de instruc"iuni (mai mult de 200 de coduri).

Cteva dintre instruc"iunile mai importante, clasificate dup! tipul opera"iei sunt enumerate

n continuare.

registru- memorie

ADD, ADC adun! con"inutul unei loca"ii de memorie la acumulator (f!r! sau cu

transport)

AND #i ntre memorie cu acumulator

CMP compar! memorie cu acumulator

EOR sau exclusiv memorie cu acumulator

CPX compar! registru index cu memoria

LDA, LDX ncarc! acumulator (registru index) cu un octet din memorie

ORA sau logic ntre acumulator #i memorie

SBC, SUB sc!dere cu sau f!r! mprumut

STA, STX salvare acumulator (registru index) n memorie

MUL nmul"ire

cite#te- modific!- scrie

ASL,ASR, LSL, LSR deplasare aritmetic! (logic!) stnga (dreapta)

BSET, BCLR setare sau resetare bit

CLR resetare registru

COM complement fa"! de 1

NEG complement fa"! de 2 (negare)

ROL, ROR rota"ie stnga (dreapta) prin Carry

TST- test pentru zero sau negativ

de salt

BCC, BCS dac! Carry este 0 sau 1

BEQ, BNE dac! este egal (sau nu)

BHCC, BHCS dac! bitul de Half Carry este 0 sau 1

BHI, BHS dac! este mai mare ori mai mare sau egal

BLO, BLS dac! este mai mic ori mai mic sau egal

BIH, BIL dac! linia de ntrerupere extern! este 1 sau 0

BMI, BPL dac! este negativ (sau pozitiv)

BMC, BMS dac! masca de ntrerupere este 0 sau 1

BRA, JMP salt necondi"ionat

BSR, JSR salt la subrutin!

manipulare la nivel de bit

BCLR, BSET nscrierea unui bit cu 0 (sau n1)

BRCLR, BRSET salt dac! un bit este 0 (sau n1)

de control

CLC, SEC nscriere cu 0 (cu1) a bitului de Carry

CLI, SEI punere la 0 (cu 1) a m!#tii pentru ntrerupere

NOP nu se execut! nici o opera"ie

RTI, RTS ntoarcere din ntrerupere (subrutin!)

180

STOP, WAIT se opre#te oscilatorul CPU #i se a#teapt! o ntrerupere extern! (se

valideaz! nreruperile)

SWI ntrerupere software

TAX, TXA transfer! acumulatorul n registrul index (sau invers)

10.2.1.5. Sistemul de ntreruperi

Unitatea central! poate fi ntrerupt! din programul curent de urm!toarele surse:

un 0 logic aplicat din exterior pinului /IRQ;

un 1 logic aplicat din exterior la pinii PA3-PA0 ai portului I/O PA, dac! aceste

ntreruperi sunt validate;

o ntrerupere de la temporizatorul sistemului (TOF Timer Overflow sau RTIF

Real Time Interrupt), dac! ntreruperea este validat!;

instruc"iunea de ntrerupere software SWI.

Dac! o ntrerupere vine n timp ce UC execut! o instruc"iune, instruc"iunea n curs este

terminat! #i apoi se consider! ntreruperea. ntreruperile pot fi invalidate global n registrul

condi"iilor de program (CCR) sau individual pentru fiecare surs! n parte. Un Reset inhib!

toate ntreruperile pentru ca procesul de ini"ializare s! nu poat! fi ntrerupt.

La apari"ia unei ntreruperi, unitatea central! termin! instruc"iunea n curs, apoi salveaz! n

stiv! registrele UC, invalideaz! ntreruperile pentru ca o nou! ntrerupere s! nu deranjeze

servirea ntreruperii curente. Cererile de ntrerupere sunt memorate #i servite dup! servirea

ntreruperii curente. n PC se transfer! vectorul de ntrerupere #i se execut! rutina de

servire a ntreruperii. Rutina se termin! cu instruc"iunea RTI care restaureaz! registrele UC

din stiv!. Vectorii de ntrerupere pentru fiecare dintre sursele enumerate mai sus sunt

stoca"i n memorie la adresele:

timer 07F8h #i 07F9h;

/IRQ sau PA 07FAh #i 07FBh;

instruc"iunea SWI 07FCh #i 07FDh;

Reset (POR, RESET din exterior, COP sau adres! ilegal!) 07Feh #i 07FFh.

Adresele vectorilor se g!sesc n harta memoriei furnizat! de produc!tor.

Unele MC din familie au #i alte interfe"e, care pot #i ele s! solicite ntreruperi, a#a cum

poate cere circuitul timer.

Pn! la servirea ntreruperii trece un anumit interval de timp (tacte), pentru ca UC s!

termine instruc"iunea curent! #i s! salveze n stiv! registrele. Acest timp este numit

Interrupt Latency #i poate fi orict de lung dac! ntreruperile nu sunt validate. Cea mai

lung! instruc"iune este MUL, care dureaz! 11 tacte, iar unitatea central! are nevoie de 9

tacte pentru a salva registrele n stiv!, deci cel mai lung timp de a#teptare pentru servirea

unei ntreruperi este de 20 de tacte. Acest timp trebuie s! fie luat n calcul n momentul

realiz!rii unei aplica"ii n timp real. Dac! survine o a doua ntrerupere, timpul de a#teptare

pentru servirea ei poate fi prea lung. O solu"ie ar fi validarea ntreruperilor n timpul

servirii primei ntreruperi. n acest caz trebuie avut grij! ca stiva s! fie destul de mare

pentru a permite salvarea a dou! seturi de registre.

181

10.2.1.6. Interfe!e "i periferice on chip

Blocurile func"ionale integrate n circuitul MC sunt de o deosebit! importan"! n

implemenatrea unei aplica"ii. Este n egal! m!sur! important s! fie cunoscute #i bine

st!pnite att capabilit!"ile unit!"ii centrale ct #i ale interfe"elor cu care este echipat MC

aceast! cunoa#tere conduce la o exploatare performant! a resurselor.

a. Porturi paralele I/O

Porturile paralele I/O sunt forma cea mai simpl! a interfe"elor. MC68HC705C8

dispune de 31 de linii I/O digitale de uz general grupate n patru porturi. Porturile A, B, #i

C sunt porturi de cte opt bi"i fiecare; sensul transferului pe fiecare linie (intrare sau ie#ire)

poate fi stabilit prin program. Fiecare linie are asociat cte un registru de direc"ie (DDR).

n Fig. 10.7. este ilustrat! organizarea portului A al circuitului mai sus men"ionat;

Organizarea este identic! #i la celelalte dou! porturi de opt bi"i, porturile C #i D.

Structura circuitului pentru o linie bidirec"ional! de scriere/citire la porturi este redat! n

Fig 10.8. Se poate constata modul de ac"ionare a bitului din registrul de sens asupra

circuitului driver de ie#ire.

Bit 7 6 5 4 3 2 1 Bit 0

DDRA7 DDRA6 DDRA5 DDRA4 DDRA3 DDRA2 DDRA1 DDRA0

0 0 0 0 0 0 0 0

Starea registrelor de ie#ire nu este influen"at! de Reset

$04 DDRA

Condi"ii la Reset

(toate liniile intr!ri)

$00 Port A

Condi"ii la Reset

PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0

Fig. 10. 7. Organizarea portului paralel A (MC68HC705C8)

D Q

C /Q

Bit de

date

WRITE

Bit

DDR

Intrare/

Ie#ire

digital!

Driver

READ

Bit de

date

Buffer

Fig. 10.8. Circuite bidirec"ionale de scriere/citire la porturi

182

Portul D dispune de #apte linii (f!r! PD6); acestea pot fi folosite doar ca linii de intrare. O

particularitate a acestui port este faptul c! pinii corespunz!tori sunt folosi"i fie de portul D,

fie de porturile seriale SPI #i SCI, n func"ie de starea de activare nscris! n registrele de

comand! SPI #i SCI.

Liniile pot fi citite sau scrise de unitatea central! cu instruc"iuni specifice. Liniile pot fi

apelate grupat, la nivel de port sau individual, la nivel de bit. Pentru a economisi timpul

unit!"ii centrale, interfe"ele pot lucra cu unitatea central! prin intermediul ntreruperilor.

b. Portul serial asincron SCI (Serial Communications Interface)

SCI este un transmi"!tor receptor asincron universal (UART) cu posibilitatea

lucrului full-duplex. Pentru un transfer bidirec"ional sunt suficien"i 2 pini. Cu circuite de

transla"ie de nivel RS232 se pot face transferuri la distan"e suficient de mari. Se poate

programa una din 32 viteze de transmisie #i lungimea caracterului; se pot valida separat

transmi"!torul #i receptorul; se pot genera ntreruperi n diferite situa"ii; se poate detecta

eroare de cadrare la recep"ie.

Formatul datelor este ca la orice transmisie asincron! (RS232 sau RS422). Linia este n

stare MARK, iar transmisia unui caracter este semnalat! de trecerea liniei n stare SPACE

pe durata bitului de START. Urmeaz! 8 sau 9 bi"i de date #i un bit de STOP.

Datele care se doresc a fi transmise sunt scrise n registrul de date al SCI (SCDR), apoi se

valideaz! transmisia prin pozi"ionarea bitului TE (Transmit Enable) n registrul de control

al SCI (SCCR2). Dup! ce cuvntul a fost transmis, se pozi"ioneaz! bitul TDRE (Transmit

Data Register Empty) n registrul de stare SCSR (SCI Status Register). Se indic! astfel c!

poate fi transmis un nou cuvnt. Se pot transmite caractere speciale, cum ar fi BREAK,

care "ine linia n stare SPACE (se transmite un #ir de 0) dac! se pozi"ioneaz! bitul SBK n

SCCR2 sau un caracter care "ine linia n stare MARK.

Golirea registrului de date semnalizat! de TDRE sau de TC (Transmission Complete) din

SCDR poate genera o ntrerupere.

Datele sunt recep"ionate n SCDR, la recep"ia complet! fiind pozi"ionat bitul RDRF

(Receive Data Register Full) n SCSR. Pentru eliminarea recep"iilor false fiecare bit de

start este e#antionat #i citit de 16 ori; orice nepotrivire a e#antioanelor duce la respingerea

acestui bit. Dac! nu se recep"ioneaz! bitul de STOP se anun"! o eroare de cadrare prin

pozi"ionarea bitului FE n SCR.

ntreruperile la recep"ie pot fi generate dac! bitul RDRF din SCSR indic! recep"ia unui

caracter, dac! este o eroare de vitez! de recep"ie prin recep"ia unui caracter nainte ca cel

precedent s! fi fost citit sau dac! s-a recep"ionat un caracter special format numai din valori

de 1.

Structura registrului de control SCCR1 este:

Bit 7 este al 9-lea bit recep"ionat dac! s-a definit o transmisie pe 9 bi"i

Bit 6 este al 9-lea bit de transmis dac! s-a definit o transmisie pe 9 bi"i

Bit 4 comand! lungimea caracterului, 8 sau 9 bi"i

Bit 3 este un bit de trezire care comand! ce fel de condi"ie treze#te SCI

183

Structura registrului de control SCCR2 este:

Bit 7 TIE Transmit Interrupt Enable - valideaz! ntreruperile cerute de TDRE

Bit 6 TCIE Transmit Complete Interrupt Enable - valideaz! ntreruperile cerute de TC

Bit 5 RIE Receive Interrupt Enable - valideaz! ntreruperile cerute de RDRF

Bit 4 ILIE Idle Interrupt Enable Bit -valideaz! ntreruperile cerute de caracterul #ir de 1

Bit 3 TE Transmit Enable - valideaz! transmisia

Bit 2 RE Receive Enable - valideaz! recep"ia

Bit 1 RWU Receiver Wakeup Enable - pune receptorul n stare de a#teptare

Bit 0 SBK Send Break - trimite caracterul BREAK

Structura registrului de stare SCSR este:

Bit 7 TDRE Transmit Data Register Empty - registru de transmisie gol

Bit 6 TC Transmission Complete - transmisie complet!

Bit 5 RDRF Receive Data Register Full - registru de recep"ie plin

Bit 4 IDLE - s-a recep"ionat un #ir de 1

Bit 3 OR Receiver overrun - eroare de vitez! de recep"ie

Bit 2 NF Receiver Noise - s-au detectat perturba"ii n datele citite (prin e#antionarea

bitului de START)

Bit 1 FE Framing Error - eroare de cadrare.

Registrul ratei de transfer este descris n tabelul 10.6.

Tabel 10.6. Con"inutul registrului ratei de transfer

Bit 5 Bit 4 Ceas pentru

transfer

Bit 2 Bit 1 Bit 0 Rata de transfer

0 0 ceas intern 0 0 0 ceas de transfer

0 1 ceas intern /3 0 0 1 ceas de transfer/2

1 0 ceas intern/4 0 1 0 ceas de transfer/4

1 1 ceas intern/13 0 1 1 ceas de transfer/8

1 0 0 ceas de transfer/16

1 0 1 ceas de transfer/32

1 1 0 ceas de transfer/64

1 1 1 ceas de transfer/128

Rata de transfer se ob"ine printr-o dubl! divizare, nti se ob"ine un ceas de transfer prin

divizarea ceasului intern, apoi se divizeaz! ceasul de transfer. Se pot astfel ob"ine diferite

rate de transfer, de exemplu 4800 Baud (4808) la un ceas de 2MHz prin divizarea nti cu

13, apoi cu 1.

c. Portul serial SPI (Serial Peripheral Interface)

Cu acest port se poate realiza o comunica"ie sincron! simpl!, folosit! de regul!

pentru a transfera date ntre circuite pe aceela#i montaj cu MC. Un transfer bidirec"ional

necesit! 3 pini, unul dintre ei fiind alocat ceasului de transmisie generat de masterul SPI.

Cu SPI se pot realiza transferuri #i ntre microcontrollere. Transferurile pot fi full duplex.

Registrele care controleaz! transferul SPI sunt registrul de control (SPICR SPI Control

Register) #i registrul de stare (SPISR SPI Status Register). Un transfer SPI poate fi ini"iat

184

doar de un master. Masterul scrie un octet n registrul de transmisie SPI (SPDR SPI Data

Register) de unde datele merg ntr-un registru de deplasare n care sunt serializate #i de

unde sunt transmise sincron cu ceasul de transmisie. Transmisia se termin! dup! 8 tacte,

cnd se pozi"ioneaz! bitul SPIF. nainte ca masterul s! trimit! un nou octet trebuie s! se

reseteze bitul SPIF prin citirea registrul de stare SPSR. n slave datele intr! n registrul de

deplasare cu tactul de recep"ie, acela#i cu cel de transmisie. Cnd au intrat 8 bi"i, caracterul

este transferat n registrul de date SPDR. Pentru a se evita erorile de vitez! (sau de

suprascriere - Overrun) trebuie ca octetul din SPDR s! fie citit nainte ca un alt octet s! fie

transmis din registrul de deplasare.

Pozi"ionnd bitul MSTR din registrul SPCR n 1, MC lucreaz! n mod master. n acest mod

pinii au urm!toarea semnifica"ie:

SCK (Serial Clock) este ie#ire de tact pentru sincronizare;

MOSI (Master Output Slave Input) este ie#irea serial!;

MISO (Master Input Slave Output) este intrarea serial!;

/SS (Slave Select) protejeaz! MC dac! dou! circuite sunt master. Acest semnal

activ dezactiveaz! la cel!lalt port SPI modul master, #terge bitul MSTR #i

pozi"ioneaz! bitul de eroare (MODF Mode Fault Flag).

Cu bitul MSTR=0 se valideaz! modul slave, n care pinii au semnifica"ia:

SCK (Serial Clock) este intrarea de tact pentru sincronizare de la MASTER;

MOSI (Master Output Slave Input) este intrarea serial!;

MISO (Master Input Slave Output) este ie#irea serial!;

/SS (Slave Select) valideaz! SPI pentru modul slave.

n Fig. 10.9. este ar!tat! o conexiune SPI n care sunt legate un circuit master #i mai multe

circuite slave.

Circuitele slave sunt validate pe rnd cu semnale dintr-un port de ie#ire auxiliar.

Pentru a putea adapta transmisiei seriale ct mai multe echipamente seriale, se poate

programa faza #i polaritatea ceasului de sincronizare cu bi"ii CPOL #i CPHA din SPCR.

MC master

SPI MISO

MOSI

SCK

/SS

Port I/O

0

1

2

/SS SCK MOSI MISO

Dispozitiv slave

/SS SCK MOSI MISO

Dispozitiv slave

+1

Fig. 10.9. Conexiune SPI

185

n SPI pot apare urm!toarele erori:

mai multe MC master conectate (Mode Fault Error)

scrierea n SPDR n timpul unei transmisii (coliziune), are ca urmare scrierea

bitului WCOL n SPSR;

omiterea citirii SPDR nainte ca urm!torul octet s! soseasc! (suprascriere).

O ntrerupere poate fi generat! n urm!toarele situa"ii:

registrul de date este gol sau plin (la transmisie respectiv la recep"ie) se semnaleaz!

cu SPIF care poate genera o ntrerupere dac! ntreruperea este validat! cu SPIE;

la apari"ia unei erori Mode Fault semnalat! cu MODF, dac! ntreruperea este

validat! cu SPIE.

d. Timer

Circuitele de timp timere - care echipeaz! MC Motorola sunt foarte variate. De la

cel mai simplu (MC68HC05J) care poate genera 2 ntreruperi periodice: una cu frecven"a

fix! #i una cu frecven"a variabil!, #i pn! la cel mai complex (MC68332) care con"ine un

temporizator cu propria lui unitate aritmetic! #i logic! proiectat special pentru controlul

motoarelor cu ardere intern!.

Un temporizator tipic (de la MC68HC705J1A), nu cel mai simplu dar nici cel mai

complex, are schema bloc dat! n Fig. 10.10.

Ceasul de intrare n timer este ceasul de magistral! (frecven"a cristalului/2) care, dup! o

divizare cu 4, constituie tact pentru un num!r!tor de 8 bi"i. Valoarea acestui registru

num!r!tor poate fi citit! de UC n oricare moment la loca"ia 09h (TCR Timer Counter

Register). UC nu poate s! modifice valoarea acestui registru. Cnd num!r!torul trece de la

Xtal/2 Divizare

cu 4

Num!r!tor hexa de 8 bi"i MSB

TCR (Timer Counter Register) la adresa 0009h

TCSR registru de control #i stare a timerului

TOF RTIF TOIE RTIE TOFR RTIFR RT1 RT0

Num!r!tor hexa de 7 bi"i Selec"ie ie#ire

Num!r!tor COP Generare de Reset

intern al UC

Fig. 10.10. Timer 6805

186

FFh la 00h este pozi"ionat bitul TOF (Timer Overflow Flag) n registrul de stare al

timerului (TCSR Timer Control and Status Register). Starea acestui bit poate fi citit! de

UC n oricare moment. Dac! bitul TOIE (Timer Overflow Interrupt Enable) din registrul

de stare TCSR este 1, n momentul trecerii de la FFh la 00h se genereaz! o ntrerupere,

numit! ntrerupere de dep!#ire (Overflow Interrupt).

Ie#irea num!r!torului de 8 bi"i constituie tact pentru un alt num!r!tor de 7 bi"i. Ie#irea de la

oricare dintre cei mai semnificativi 4 bi"i ai acestui ultim num!r!tor (selectat! de unul din

cei doi bi"i RT1 #i RT0 din registrul de control TCSR) poate fi folosit! pentru generarea

unei ntreruperi, numit! de timp real (Real Time Interrupt ) care nscrie bitul RTIF (Real

Time Interrupt Flag) din TCSR. Se genereaz! o ntrerupere dac! bitul RTIE (Real Time

Interrupt Enable) este 1.

Ultimul nivel al timerului este un num!r!tor de 3 bi"i folosit pentru cesul de gard! (COP

Computer Operating Properly). Dac! este validat! verificarea COP, trebuie ca

programatorul s! reseteze COP nainte de expirarea perioadei programate pentru comanda

unui RESET al UC. Perioada de timp n care COP trebuie resetat depinde de RT1 #i RT0.

n tabelul 10.7. sunt date perioadele de ntrerupere #i perioadele n care COP trebuie

resetat. Perioadele corespund unui tact de 2MHz:

Tabel 10.7. Perioade de ntrerupere #i perioade de reset programabile cu un tact de 2 MHz.

RT1 RT0 Perioada de ntrerupere Perioada n care COP trebuie resetat

0 0 8.2ms 57.3ms

0 1 16.4ms 114.7ms

1 0 32.8ms 229.4ms

1 1 65.5ms 458.8ms

Un reset al COP se poate realiza prin scrierea bitului 0 de la adresa 07F0h (COPR COP

Register).

MC din seria 68705 sunt echipate cu un temporizator care are posibilitatea de captur! #i

comparare. Captura poate nregistra momentul la care apare un eveniment extern (o

tranzi"ie pe pinul TCAP). n acest moment memoreaz! con"inutul registrelor timerului n

registrele de captur!. Memorarea registrelor timerului la tranzi"ii de aceea#i polaritate a

TCAP poate determina perioada unui semnal, iar la tranzi"ii de polaritate opus! poate

determina l!"imea unui impuls. Polaritatea de declan#are este programabil!. Prin

comparare se poate genera un semnal de ie#ire cnd num!r!torul timerului atinge o valoare

selectat!. La fiecare 4 tacte se compar! valoarea num!r!torului cu cea scris! n registrul de

comparare. Dac! este egalitate se genereaz! un semnal TCMP.

e. Portul PWM

Modula"ia impulsurilor n l!"ime (Pulse Width Modulation) are multe aplica"ii, mai

ales n comanda motoarelor de curent continuu sau a surselor de alimentare. Din acest

motiv unele MC includ n structura lor un modulator PWM ca interfa"!.

Un semnal PWM arat! ca n Fig. 10.11.

187

Circuitul MC68HC05D9 con"ine 5 canale PWM de cte 6 bi"i care sunt realizate cu

ajutorul unui num!r!tor de 6 bi"i, un registru de control PWM #i 5 registre de date care

formeaz! 5 linii PWM ce sunt disponibile la pinii portului D (Fig. 10.12).

n registrul de mod sunt 5 bi"i care valideaz! modulul PWM astfel nct semnalele PWM s!

fie livrate pe la pinii portului D. Tot n registrul de mod mai este un bit, SCIB, care

selecteaz! dac! la adresa 000Dh s! fie date pentru PWM sau rata de divizare pentru SCI.

Dac! nu sunt folosite ca ie#iri PWM, liniile portului D pot fi folosite ca intr!ri/ie#iri

obi#nuite. Registrul de mod PWM se afl! la adresa 0008h.

Dac! se ncarc! registrul de date cu 00h semnalul la ie#ire va fi tot timpul zero. nscrierea

valorii 20h n registrul de date are ca rezultat un semnal cu factor de umplere 50% la

ie#irea corespunz!toare, iar nc!rcarea valorii 3Fh va determina un semnal cu factor de

umplere de 63/64.

f. Portul USB (MC68HC05JB4)

MC68HC05JB4 con"ine un convertor A/D #i o interfa"! USB, ceea ce l face ideal

pentru achizi"ia de date #i transferul lor c!tre un calculator PC-AT. Datorit! structurii USB,

T1

T2

Factorul de umplere este

T2/T1

Fig. 9.11. Semnal PWM

Num!r!tor de 6

bi"i

PWM4 (000Dh)

PWM3 (000Ch)

PWM2 (000Bh)

PWM1 (000Ah)

PWM0 (0009h)

R

E

G

I

S

T

R

U

D

E

M

O

D

P

W

M

PWM 4

PWM 3

PWM 2

PWM 1

PWM 0

Fig. 10.12. Structura modulului PWM la familia 6805

0008h

188

este posibil! realizarea unui punct central de prelucrare echipat cu PC #i multe puncte de

achizi"ie echipate cu acest MC.

Modulul USB implementeaz! standardul USB 1.0, de mic! vitez!, la 1,5Mbps, cu 3 puncte

de cap!t (End Point). MC con"ine #i transceiverul USB. Schema bloc a modului USB este

dat! n Fig. 10.13.

Figura 11

Transceiverul are o ie#ire diferen"ial! care poate lucra cu 3 st!ri pentru a permite transferul

de date bidirec"ional de tip full-duplex. Receptorul trebuie s! fie de asemenea cu intr!ri

diferen"iale.

Comanda interfe"ei USB se realizeaz! prin intermediul a 3 registre de comand! iar starea