Sisteme Cu Microprocesoare M.popa

Încărcat de

Fromy AlexSisteme Cu Microprocesoare M.popa

Încărcat de

Fromy Alex6

cu !\[lr:Jlc >PH<)( ;1.:sc )ARI :

Cartea a fost n 7 capitole. Capitol ul I este o introducere n tematica

n caite.

Capitolele 2-4 microprocesoare din familia fntel. Sunt descrise micro-

procesoarele 8086, 80386 Pentium rI. Desigur mai multe microprocesoare n

familia Intel dar au fost alese cele de mai sus pentru

0

8086 este primul microprocesor pe l 6 al familiei J ntel primul microprocesor

pe 16 care s - a are caracteristici care au fost preluate dezvoltate

de membri ulteriori ai familiei, este didactic de

c 80386 este primul microprocesor pe 32 al familie i fn tel modul de

gestiune a memoriei se la membri ulteriori ai fami liei;

o Pentium Il este un microprocesor evoluat care cteva caracteristici

structurale avansate, ca de exemplu a

care extraordinarele la microprocesoarele mai

evoluate de azi.

Sunt descrise: structura microprocesoarelor, modul de gestiune a memo1i ei, sistemul

de ntreruperi, modul de conectare a circuitelor de memorie a porturilor de intrare I

Capitolele 5 6 microprocesoare din familia Motorola. Au fost aJese

microprocesoarele 68000, echivalentul lui 8086 68030, echivalentul lui 80386.

microprocesoarelor Motorola este mai autorul a considerat

prezentarea lor pentru a alte pentru implementarea unor caracteri"stici

existente la micoprocesoarele din familia lntel precum noi caracteristici.

Capitolul 7 este dedicat calculatorului PC, mai exact a modului de conectare a sa

la lumea Autorul este modului n care

calculatornl PC poate monitoriza, controla comanda diferite externe, industriale

mai al es, ca urmare sunt descrise prin care PC-ul poate face acest lucru: porturi le

paralel seri e, portul USB magistralele de intrare I de pe placa de Sunt

descrise cteva

carte constituie suportu] pentru disciplina Sisteme cu microprocesoare,

din anul 3 ingineri 2 colegiu ai de Calculatoare, respecti v

de calcul, din Facultatea de Calc11/atoare, Universitatea

"Politeli11ica" din Autorul lucrarea este

din domeniile electronicii, electrotehnici i, energeticii

mecatronici i.

decembrie 2002

.,

CUPRINS

.. : .. . .. .. ?

:: : ::: : : : : :::::: ::: ::: : : : :: : : :: : : :: ::: : : : : . ; : :;: ... . ........

p. . I. I. de ale microprocesoarelor pe 16, 3_ 64 b1,1..::i 6

1

2.

.. .

2. I . Prezentare . .. . .. .. 28

2

? Moduri le d; lucru tenninalele.. .. ... ..

31

, J l. ::;:::: : : : :.::: ::.:. ::::: :: :::.:. . .::::::.::: .: .:: :: : :: :: : ::.::::: ::::: ::.:: ::::: : :::::: ::::: :;

2.5. Oroanizarea gestionarea memone1 .. .. ..

45 . . . . ...... ... .

2.6. Sistemul de intrare I .. .. . .46

2 7 Sistemul de ntreruperi . 50

--5-'s: Unitate cu microprocesorul 8086 .:.i.8086.56

.

1

1

- 2]). Conectarea memoriilor la

0

[Link] cu m.1croprocesoru

1 8086

:::: :::::::::

59

,_ . 2 I O. Conectarea porturilor la o unitate cu 62

---1:2. 11 Conectarea microprocesorului 8086 n sisteme mult1?roce2s8o91 . 63

. . 2 11 1 Arb1'ttarea maoistralei comune de c1rcu1tul 8 . -

. . . "' . . I 8?89 6:>

C

i ? I I 2 Controlul magistralei comune de c11:cu1tu - 66 11

i 11 :3: Comanda controlerului 8288 .de arbitrul 8289

66 /

2

.

1

1.

4

. de sistem cu arbitrul 8289 .. .

73 Cap 3 Microprocesorul S0386 .: .. .. .. .. .. 73

:, ! t

: . . H

, 3 4. Ciclurile .. .. .. 86

5 Oroanizarea gestionarea memoriei ..... .. . 86

t-.). . o . .

1 3.5. l. Modul real g

7 ..1, 3.5.2. Modul protejat. .... ...... ... .. .... . .. . ... . .. .... .. . .. .i03

1. 3.5.3. Modul virtual.....:::: :: ::::::: I o4

/ 3 .6. Initializarea microprocesorului .. .. I 05

' 3.7. Sistemul de intrare .... . ... ... 105

1.8. Sistemul de ntreruperi.. .. ... ... .... . ... .... .. .. . ... .. 109

. . 3 9 Unitate cu microprocesorul 80386 .:.... I 10

. . , 3: I O. Conectarea memorii ior la o unitate cu microprocesorul 80386. I 13

Cap. 4. Microprocesorul Pentium II : :::::::: :: ::: 113

4. 1. Caracteristici generale . 113

4 2. arhitecturale .. . ... . 121

4

3 Configuratii ale procesorului .. !24

4 4: Conectare; microprocesorului Pentium fI pe placa de . .. 125

4:5. Alte microprocesoare din familia P6 .:::: ::::::::::

127

Cap. s. Microprocesorul 68000 ... .. ... .. . : 127

s l Prezentare ... .... .. .. . ' l ?7

s:2: Terminalei: ................ ... ... .... . .. .... . . .. . ....... ......... ....... .......... .. .. -

Sl!'Tl.i\U: Cll flll<:R< Jl'H< l \RI :

5.3. Structura .. .... .. . . .. .... .. .. .. . . 131

5.4. Cicluri le .. . .. ...... ... . . 135

5.5. Funciionarea n modul asincron n modul sincron ...... 138

5.6. Organizarea gestionarea memoriei .... 140

5.7. Sistemul de intrare I ... .. . ... .... . ... I <11

5.8. Sistemul de ntreruperi .... . .. ... 14 J

5.9. Unitate cu microprocesorul 68000 .... .. ... ... 150

5.1 O. Conectarea memoriilor la o unitate cu microprocesornl 68000. 150

Cap. 6. Microprocesorul 68030 ... .... 153

6. 1. Prezentare .. . .. ......... . 153

6.;2. Organizarea gestionarea memoriei...... 153

6.2. 1. Unitatea de gestiune a memoriei .. ..... . ... .. .153

6.2.2. de translatare a adreselor ......... 158

r 6.2.3. . ..... ... ....164

, Cap. 7. Comanda cu microcalculatorul PC... .. .. 167

7.1. Portul paralel .. . .. . .. . .......:.. 167

7. 1. 1. Standardizarea portului paralel .. . ..... 168

7.1.2. Caracteristicile de ale portului paralel . 168

7. 1.3. Cabluri caracteristici electrice . .. .... 172

7 .1.4. Moduri de lucru... .. .. . . . 175

7. 1.5. ntreruperile la portul paralel ..... 191

7. 1.6. Utilizarea porcului paralel prin intermediul BIOS-ului .. J 92

7.1. 7. ............. 193

7 .2. Portul serial .. .. .. . ... . ........ ... .. . .. . .. .. . .. ... . ... .. . 237

7.2.1. Bazele serie a datelor .......237

7.2.2. Standardul RS232 ..............243

7.2.3. Standardele RS422 RS485 .... .. ..... 245

7.2.4. Cabluri conectori .... .. ..... ... 250

7.2.5. Magistrala FC .. ..... .. . ..253

7.2. 6. Portul serie al calcul atorului PC... .. ..259

7.3. Portul USB......... ...... .. .269

7.3. 1. Stadiul actual al periferiei la calculatorul PC ....269

7 .3.2. Caracteristici generale ale USB ..... . . . . 270

7.3.3. Caracteristici fizice ale USB ........270

7.3.4. Protocolul USB .. . .. . ... .. . .. .. . .. ... .. .. 275

7.3.5. Configurarea sistemului USB . ...277

7.3.6. Codificarea datelor. .. ... .. .. ... .... ... .. .. 277

7.3.7. Transferul datelor .. .. ... . .. ... .. . ... . .. . .... .. 278

7.3.8. USB 2.0. .. ... .. . .. . .. . .. ... .. .. .... .. 280

7.4. Magistralele de intrare I

7.4.1. Placa de a unui PC ...........280

7.4.2. Magistrale .. ..... ... . .. .. .. . ... . .. ...... .. ... ........ .. .282

7.4.3. Magistrala ISA ... ...... ... ...... ....... .. ... ....... ... .. . ... .. .... .283

7.4.4. Alte magistrale de I/E ..... .. . . 287

7.4.5. Magistrala PCI ... .. ..... ...287

Bibliografic .... .. ..... .. ..... . .. 293

Capitolul 1

INTRODUCERE

calculatoarelor se printr-o dinamicitate.

de aproximati v 60 de ani, istoria calculntoarelor este deosebit de h

Calculatoarele au evoluat pe mai multe dimc11

consllln cost. Prime le calculatoare, de uz general, lucrau Ja de tact

tle KHz, gestionau o memorie de zeci de ocupau o ncn

consumul era la nivelul de zeci de KW iar prctul era la nivelul zecilor sau sutelor di

de dolari. Calculatoarele de uz general de azi la de tact de 1-3 t

o memorie de sute de Mo. consumul este de aproximativ 500 \-\

tot cu monitor) iar este la nivelul sutelor de dolari. Aceste date, sum.1

generale, gradientul aJ calculatoarelor.

Motorul acestei ii constituie, n opinia autorului, domeniul 111

procesoarelor. Calculatoarele au evoluat n lipsa microprocesoarelor dar semniftl

au fost acestora. Evolulin microprocesoarelor este, de asemr

istoria lor este mai de aproximativ 30 de ani. Se va 1111

doar faptul primul microprocesor, 4004, al firmei Intel era pe 4 inlo(

aproximativ 2.900 tranzistoare n timp ce microprocesoarele Pentium IV, de U7.I,

firme Intel, sunt pe 64 peste [Link] tranzistoare. M1

procesoarele au [Link] unui nou tip de calculator, microcalculatt

tipul cel mai fi ind PC-ul. Dezvoltarea PC-l11

au determinat impulsionat dezvoltarea altor domenii ale calculatoarelot

exemplu edificativ fii nd Internet- ul.

. Microprocesoarele se mpart numl!rul de linii ale magistralei de dol

microprocesoare pe: 4, 8. 16, 32 64 biJl microprocesoare deosebit de perfon11

scumpe, la care magistrala de date poate avea mai mult de 64

de uz general ntlnite ln microcalculatoarele de lip PC n sisteme orientate pe 11plir

carte descrie microprocesoarele de uz general pe 16, 32 mai 64 u1

problema microcalculatorului PC n monitorizarea co1n11

aplicariilor externe.

1.1. de ale microprocesoarelor pe 16,

32 64

n acest paragraf vor fi prezentate, pe scurt, principalele de evolL1\ic

microprocesoarelor pe 16. 32 64 raportat la microprocesoarele pe 8

, Dimensiunile magistralelor de date adrese

pe 8 biti, magistrala de 8_ biti iar ele adrese A

16 bili, gestionarea unui ele rneni.o-rie de 64 Krt La miCroprocesonr

-- -- --

10 I'. CU l\llCRlll'Rt H '. LS< 'I.I HI:

64. aceste dimensiuni cresc. Astfel de date. 1. . V

rq,sgectiv 64 ceea ce-a duS"la_ vitezei de cu _ na 1 ortunle

Tn,trudt aca a e ee I I era ;.i_n, CIC u.._a

cele e 16, 32 i 64 se mai ntr-un smour ciclu. transferul cu

memoria cu po1tunle se poate ace pe cuvant, ublu cuvnt sau quadmplu cuvnt, se

la toate microprocesoarele pe mai mult de 8 transferul I_a ni vt:I ele octet.

l n acest fel se compatibil itatea cu programele scnse pentru microprocesoarele

pe 8 din familie, se flexibilitate pentru conectarea

microprocesoarelor n sisteme.

liniilor de adrese de

la 20 linii de

pe i Mo la 36 ad:Wi II. as1gurand

gest10narea umu Cle memorie fizic de 64 Go.

.i Structura - .1

inte;ne a fost de tot mai ..

pri[l de dar

-perin!s

de tact de pe placa de a s-a impus a fost !:!,tilizarea a

2 de tact: unul extern umil intem cu tiecven a de cea cu

un actor mt e O rezuffn asttefiecven e e tact man nu

a fost un aport semnificativ a fost adus de e structurale.

_prin s-_ prin a

C0!1C_eP-te: su aducerea n avans de asamblare.

microprocesor pe 1 , ___ 64 mai rnu te care relativ

independent, asigurnd astfel, de exemplu, aducerii codului

cu altei rezultnd de t iJ}W_. La microprocesorul 8086

doar 2 astfel de interne dar la 80386 6 astfel de de timp

fi ind cu att mai mare cu ct de este mai mare.

Implementarea conceptului de aducefe i'! aVansL permlte __.!!!!.f.g>procesparelor

mai eficient timpul resursele externe. Astfel,_ n timpul unei

mi surit solicitate magist ralele externe, microg;&sorul aduce n ayaqs. din

[Link], instruqiuni le depune n o tam2on de unde

vor ti luate n vederea Ufiitatea ae microprocesorului

va mat rapta, ntruct preluarea Se face din interior, rezultnG astfel

timp.

-- Implementarea conceptul ui pern1is ca,_ la un moment

dat, ntr-un microprocesor se a e mat mu te m 1 ente

crescnd astfel de executate n un[tqtea de timp.

. Pe lngii' conceptele de mai sus, la m1croproces-oarele pe 32 au mai fost

implementate altele: t;:l_l'._ecujfa.

toate avnd ca scop vitezei de S_([Link],tea micro-

- rocesorul oate executa n _Re3qM de timP. dar

acesta este limitat de ntre ms care_i:iu permit, uneori,

n micro rocesorul ad1ice n avans mai multe

le intern aste mct mm11n1zeze inter epen ente e m re

Cap. I. Introducere

I I

n n@a qrdine, crescfuld de ti111p.

este deose6lt de ntruc1 oferit de banda de asamblare este anulat 1a

modifi carea normale de a unui program iar n cazul unor

pierderea de timp este mai mare ntruct nu se poate afla adresa

dect celor de dinainte. Conceptul

previzionarea de a astfel pierderea

nu se putea afla adresa dect

Mai multe moduri de lucru

. - - -

peste J mai multe moduri de lucru.

microprocesoare pe .16 !!lli au 2 .de lucru care au denumiri diferite, la diferite

.fa111il ii._ ele se numesc: ninirn i maxim la 80 6 i ptil izator .i su ervizor la

' !.ndi un mod este mai privilegiat mai privi legiat.

La evoluate mai multe moduri de lucru, cu diferite grade

exemplu, la 80386 4 nivele de privilegiu.

_ 'Kjodurile _de se n general, prin program, cu lui 8086 la

care instalarea se face prin hardware.

Existenta mai multor moduri de lucru este o a unui micro-

restirselor [Link] software ale unui sistem. resurse,

iTI_e_rno.rii, porturi, mi pot fi folosite dect un program n modul

astfol contra acceselor neautorizate la ele. microprocesoarele

care au m- ele de rivilegiu se oate face o jerarhizare a [Link]: astfel

nucleul sistemului de operare va avea maxim

1

avnd astfel acces la toate

resursele siste u1L i driverele sistemului de o erare vor avea nivelul oe privilegiu

imediat ca turnare nu vor avea acces la une e dm resurse iar 2ro ramefe"

' [Link] yor avea nivel minim de privilegiu avnd accesul la resurse imitat. In

' acest fel sistemul de operare este protejat contra acceselor neautoriiefaresursele sale.

rezultnd astfel o a sistemului de erorile utilizatori lor.

- Si stemul de ntreruperi }

microprocesoarele pe 8 ntreruperi externe. La pe 1 g,_32

. 64 ntreruperi externe interne. din exterior, nu

[Link] de program 11 l!!l.1RUI 2i sunt

_n raport cu Fiecare microprocesor are terminale dedicate

pen1Tuaceseintreruperi:

ex teme pot fi n 2 categorii: mast:abile si nemascabile; mascarea

realizndu-se prin program. Cele mascabile pot sau fie luate n considerare,

cui dore te ro ramatorul iar cele nemascabile vor fi [Link] ntotdeauna n considerare.

Tratarea lor se face prin intermedi ul unei ta e e care adresele de nceput ale

rutinelor de tratare diferite tipu1i de ntreruperi. Pentru cele nemasc'!bile

microprocesorul un acces la o intrare n bine de unqe

aunge la rutina de tratare iar pentru cele mascabilc:; micro rocesorul a tea un vector,

pe linu e de date, e a ce care a generat cererea, iar acest vector l pentru a .

ajunge la intrarea din care adresa de rutinei de tratare.

au _ntreruperi eXerne nevectorizate, de exemplu 68000.- H--

12 SISTl::>.w ( :1_! !lllt:llC ll'f{t )( :1:sc l.\lli'

vin din interiorul microprocesorului, sunt se

de program n timpul au apJ}rut sunt smcrone cu microprocesorul.

Ele fie care apar naintea sau n timpul

unor de [Link] . cnncercare de a realiza o cu 0 sau o ncercare

de a executa o de un program care ntr-un mod

neprivilegit, fie De exemplu, microprocesorul 8086,

din fami lie, -lNf nn a executie va provoca generarea unei

ntreruperi interne. n acest fei pot fi emulate noi Trc;tare_a [Link]

iiiterne este lot doar acum, pentru fiecare corespunde

.ojntrare)n iar n cazul vectorul este generat inte{n.

pentru implementarea de si steme mu!titasldng

Microprocesoarele peste 8 pentru implementarea de sisteme

multitasking. Primul microprocesor la care se ntlnesc este 80286 al firmei Intel, pe 16

microprocesoare, pe 32 64 aceste

Microprocesoarele firmei Intel, de la 80286 n sus, memoria n mai

multe moduri. Modul protejat este cel ce microprocesorului toate

legate de implementarea sistemelor multitasking. Astfel, n acest mod microprocesorul

prin hardware prin microcod:

o separarea segmenlelor de memorie ntre diferite taskuri ntre acestea sistemul

de operare;

segmentelor de memorie proprii unui task; n acest fel fiecare task are

propriile segmente de memorie care nu pot fi accesate de alte taskuri dect el

acest lucru, de asemenea sistemul de operare are segmente de memorie

proprii, protejate contra acceselor neautorizate;

(l comutarea taskuri lor cu schimbarea a microprocesorului

noului task.

Desigur, un sistem multitasking poate fi realizat microprocesoare care

includ de mai sus, dar lor enorm munca programatorilor

care nu mai trebuie realizeze prin program de mai sus ci se

microprocesorul de ele, in plus, semnificativ de

memoriei

a rnic_roprocesoarelor a constituit-o modul de gestiu!1e

a memoriei. La microprocesoarele pe 8 singur de adrese att pentru

programator. ct 111icro_procesor. La 111icroprocesoa1:ele pe 16

adreselor logj_9e, pentru programator adreselor fizice, pentru micro rocesor.

ca peste 16 biti un spatlu, cel al a reselor liniare, o OST!.

tot de '=-

mai multor de adrese munca programatorilor.

nu mai trebuie cont de constrngerile fizice ale microprocesorului, n plus, mai

programatori pot lucra independent scriind taskuri care pot rula n paralel pe

microprocesor.

acestor avantaje mai cere, ca microprocesorul suporte memoria

Toate microprocesoarele de la 80286 n sus au Mecanismul

de memorie permite exti nderea memoriei interne a unui sistem

1:ap. I . lntrod\1ccrc

la capacitarea da1a de memoria i11te1 plus memoria pe suport extern. n tim

execu[iei une i inst1uc1iuni, microprocesornl nu operandul dorit

memoria ntrerupe execu1i:1 instructiunii, care intervine sistemul

operare care operandul cerut pe suportul extern l l

memoria ntr-o pc c:ire o anumite criteri i apoi fie r

instn1ctiunii, fie cont inul'\ cxecuna acesteia. Eliberarea se face prin scri ere

suportul extern. Transferul ntre memoria cea nu se face la nivel

octet ci la nivel ele blocuri, segmenle sau pagini ntregul mecanism este transpan

ut il izatorului care nu arc nimi c de pentr u lansarea n a mecanismului

memorie La ni velul utilizatorului se va o a vitezei dar st

implementate, la nivelul sistemului de operare metode pentru minimizarea

tehnici. Mai mult, microprocesorul supo1i hardware pentru impl ementarea accs

tehnici . De exemplu, o asemenea n felul atunci cnd sislen

de operare blocul cu operandul dorit pe suportul extern, l va aduce n memo

va scoate din memoria un bloc, pe care l alege anumite crite

1

care va trebui fie scris pe suportul extern. Dar acest bloc a fost adus n prealabil de

extern tot n cadrul unei a mecanismului de memorie da

sistemul nu a fost scris de la ultima aducere de pe supor

extern, deci nu a. !ost modificat, decide nu mai este rescrierea lui pe supor

extern oricum se acolo. ln acest fel se ti mpul de

blocului pe supo11ul extern, timp care este semnificativ seama de faptul ori

suport extern este foarte lent raportat la viteza microprocesorului. Microorocesu

1

suport hardware pentru n sensul are ranguri, pentru fiec2

segment sau de memorie, care segmentul sau pagina au fost modific<

de la ultima lor aducere 11 memoria

]J_pplernentarea mecanismului ele memorie cere o fac ilitate anur

. osibili tatea de intreru ere a 1n timpul lor. Toate 1111croprocesoic

de a 8 - ,o 1n sus au facilitate spre deosebire de cele pe 8 restul pe

care nu permit ca lor fie ntrerupte.

mai multor de adrese impune un mecanism de translatare a adresei

.il act,rese lin_iare sau fizice. 111ec<1nism la fiecare pes

8 va 11 dem1m1t. generic, [Link] (acroni mul de la "Memo1y Management Unit"). Unc

microprocesoare includ MMU-ul, ele exemplu cele ale firmelor Intel Motorola

timp ce la microprocesoare, de exemplu cele pe 16 32 ale firmei Zilog. MMU-

este ex!ern. ln cai1e vor fi descrise doar microprocesoare ce includ MMU-ul.

ln forma sa cea mai un MMU poate fi realizat printr-o care trebu

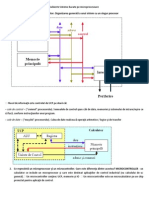

se afle n memoria fig. I. I. Adresa de programator, este l

index n iar din tabela astfel va fi tocmai adre:

Mecanismul este foa11e simplu dar poate fi aplicat doar da

microproce,sorul memoria ca fiind locati ile succesive avnd adre'.

succesive. marele dezavantaj al acestei este acela tabela va trebui ail

dimensi_uni ca memoria ce trehuie ca urmare se pierde 2/3 d

memoria ln nu este

Unele microprocesoare memoria ca fiind n blocuri care p

fi gestionate independent. 2 variante de blocuri: segmentel_e, card;tint [Link] c

dimensiuni variabile mari, de e:-:emplu pot fi de 4 Go la microprocesorul 80386

14

prin. ?9ft'"..?re_

sunt blocuri de dimensi uni

ri11ci, de exemplu 4 Ko la 80386 care sunt _gest1onate pnn hardware.

... n [Link], de exemplu 8986_ iar

1

altele, de exemp!U- dela 80386 inclusiv n sus, [Link] ca fi!nd n _

iar acestea ca fi ind din pagini . segmentele sunt blocuri cu adrese f

succesive ele se pot suprapune. Este mai o memori" .

doar n segmente, sLint inai dar ctezavanta"j"ul unei asernene __ _

este fi:agmentarea melnoriei fizice: segmentele pot fi plasate astfel .i1-- ;

existe zone ntre ele dar acestea slnle att de 1niCinct n ele

nu un alt [Link] ceea ce va duce la ineficienta util izare a memoriei fizice. Fig.-1.2

un exemplu de plasare, cu fragmentare, a segmentelor n menioria fizica.

rnil}im1zat. de defragmentare care segmentele ..

n memorie astfel nct creeze cu adrese succesive de dimensiuni mai mari n

care alte segmente. .\

Adresa

I

I I

: Memorie :

I I

I I

I

I

I

I

I

H-

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

'

I

I

I

I

' I

I

I

I

I

I

I

I

I

Adresa fizice

rL

'

' fabela de transl,1ta1e

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Locatie:

i

:

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

' I

----- ------ ------------------------- ---------- ----- -'

Fig. 1. 1. Translatarea adreselor printr-o

(Jestionarea paginilor este mai ntruct sunt semnificativ mai multe,

dar este mult de faptul au dimensiuni fixe iar

suport hardware specific. Avantajul memoriei n pagini este eficienta

utilizare a memoriei fizice. Dat [Link] o are dimensiuni mici, ea poate fi

n orice din memoria

La o memorie n segmente pagini pot fi folosite mecanisme de transla-

tare mai perfonnante. Figura 1.3 mecani smul de translatare al microprocesoarelor

din familia Intel, de la 80286 n sus. Acest mecani sm va fi re luat detaliat n Capitolul 3.

Cap. 1. Introducere

Segment

de

cod

Segment

de

date

Segment

de

zone

inutilizabile

Fig. 1.2. Exemplu de fragmentare a memoriei

/-----------------------1

/ Memorie :

I I

Componenta

/ I

'------' I

I

I

I

'------------'

Componenta

'--------'

I

I

I

I

I

I

I

I

/

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

l

I

I

I

I

: Tabela :

Fig. 1.3. Mecanismul de translatare a unei memorii n segmente

16 I .l' ,\J I( I(\ ll' I(\ )I ),\IU'.

Adresa are 2 componente: o care duce la adresa ele a

segmenlult! n care se operandul dorit care este n11 cmprocesoru!yj o

de programator _:_are .:.ste

a de a fost Asocierea nlre cele 2 componente o face

micmprocesorul reguli bine determinate poate fi doar de

programator.

cere o de translatare de dimensiuni mici, ea trebuind

attea cte segmente sunt. cum de segmente este mic, dimensiunea

tabelei v.a fi chiar o intrare nu doar adresa de nceput a segmentului

ci alte ca de exemplu dimensiunea segmentului, drepturile de acces la

segment etc. Un alt avantaj al acestei este acela pentru orice acces o

trebuie se prin mecanismul de gestiune a segmentelor care va face

pentru drepturile de acces n respectivul segment. n acest fel segmentele sunt protejate

contra acceselor neautorizate. n fine, un alt avantaj al acestei este acela diferite

taskuri pot lucra n paralel. Ele pot accesa memoria n paralel, fiecare task avnd

proprii te segmente propria de translatare. se dorqte. este posi bil ca unele

segmente fie folosite n comun de mai multe taskuri ceea ce duce la folosirea mai

a memoriei. un dezavantaj al acestei pent ru a ajunge ta

trebuiesc accese supl imentare la memorie ceea ce timp suplimentar

irosit. Acest dezavantaj a fost minimi zai ele care va fi n Capitolul 3.

programatoru! segmentele vor fi gestionate ca fiind din

pagini. Mecanismul de translatare n pagini fizice preia de mecanismul de

gestiune a segmentelor o n adres2. Mecanismul de translatare poate

fi pe un nivel, sub forma unei tabele cu attea cte tabele sunt,

ntruct dimensiunea tabelei va fi mare va ornpa o cu adrese succesive mare n

memorie, de exemplu la 80386 o asemenea are nevoie de 4 Mo, sau poate fi pe

mai multe nivele fiecare clin aceste ni vele avnd dimensiuni mici, egale chiar cu

o Aceasta este la 111icroprocesnarele Intel, de la 80386 n sus

care va fi pe larg n Cap. 3. Avantajul ei este folosirea a memori ei iar

dezavantajul este faptul introduce accese suplimentare la memorie ceea ce

timp supl imentar pierdut dar dezavantajul este minimizat prin introducerea unei

memorii cache doar pentru paginare. va fi n Cap. 3.

i .2. Circuite uzuale

n capitolele vor fi prezentate scheme pentru centrale pentru

conectarea unor circuite de memori e la centrale cu diferite microprocesoare.

Circuitele importante folosite vor fi descrise n continuare.

Circuitul decodificator 74LS1 38

Este un circuit decodificator 3 la 8, folosit n decodificatoarele pentru memorii

pt:ntru porturi. terminalelor, din punct de vedere este prezentatii

in fig. 1.4, iar tabelul I. I circ ui tului .

Cap. I. '111t roduce1c

A2

Vrc

--

-

YO

-

Al

-

Yl

AO

.7

4

-

Y2

L -

s

YJ

I -

J

Y4

-

8

- .

El YS

-

- -

-

E2

Y6

-

-

E3

GND

Y7

'i'

E3 IE2 /EJ A2 Al

I o o o o

I o o o o

l o o o l

I o o o I

I o o I o

I o o I o

1 o o l l

I o o l I

o X X X X

X I X X X

X X l X X

. .

-

-

::-

;;.

-,;.

AO !YO ! Yl

o o l

l I o

o I l

I I 1

o I I

I l l

o I I

1 I l

X I I

X I I

X I 1

Fig. 1.4. tenninalelo

circuitului 74LS 138

IY2 IY3 I Y4 IY5 /Y6 IY

I l I I 1 1

l J l I l I

o I I I l I

- ---

1 o I I l l

1 I o I I l

-

I I i o J [

I I I I o 1

l 1 1 I l o

--

I I 1 1 I I

l l J I l I

I I l l l I

Tabelul I. I. ci rcui tul ui 74LS I 38

Circuitul ;ire 3 de date,_ootate <;;!:!_A2-0, 3 de validare, notate cu IE I. /E2

EJ 8 notate cu /Y7-0. 9!:_cuitul cte o trece la O logi

e!,ntru fiecare de_la intri1rili..A2-0 dar numai IE I = /E2 =O E3 =

vreuna din a se vedea ultimele 3 linii tabele

inactive, indiferent de de la A2-0.

Circuitul decodificator 74LS139

Este un ci rcuit decodificator folosit n decoclificatoarele pentru memorii pentr

tenninalelor, din punct de vedere este n fig. 1.:

iar tabelul 1.2 circuitului.

Circuitul are 2 independente 2 la 4, fiecare cu propria linie de validare

Pentru ca o lucreze este necesar ca linia sa de validare fie ta O logic ia

aceasta este la I logic, respective sunt inacti ve, la I logic ..

18

li>

IB

IA

.

-

.

IG

.

.,. 2B

r

. 2A

.

-

. 2G

/ iG IB

o o

o o

o I

o I

I X

Vcc

-

l YO

-

!Yl

-

7

lY2

4 -

L

IY3

s

l

3

9

-

2YO

-

2Yl

-

2Y2

-

2Y3

GND

t

iA

o

I

o

I

X

-r

- .

.

.

- r

,.,.

.

.

/iYO

o

1

I

1

l

Fig. J .5. terminalelor

circuitului 74LS 139

/iYI /iY2 /iY3

l 1 I

o I 1

I o I

1 I o

I I I

?

Tabelul 1.2. circuitului 74LS 139

Circuitul amplificator/ separator 14LS244

Este un circuit folosit pentru amplificarea/ separarea magistralelor

ale mi croprocesoarelor. din. punct de

n figura 1.6, iar figura 1.7 prezmta. [Link] a ]

Din schema sa se c1rcu1tul este 2 g1 upe de 4;.

porii cu 3 avnd o intrare de val idare. j

Tabelul 1.3 c1 rcU1tulu1. }:

1/G '2/G 1Y4-l 2Y4- l

-

Cap. 1. Introducere

;. l Al

Vcc

'E

. IA2

1Y2

: IA3

1Y3

;. 1A4

7

4

IY4

'

-

L

.

I G s

2

. 2Al

4

.

2A2

4

2Yl

r

2A3 2Y2

::

.

t

;. 2A4 213

.

2Y4

.

- r .

2G r

GND

t

IA!

IA2

IAJ

!A4

IG

2Al

2A2

---r>

2AJ

-+

2A4

-----

2G

Cir cuitul amplificator/ separator 74LS245

Fig. 1.6. terminalelor

cin.:uimlui 74LS244

l Y!

IY2

I YJ

JY4

.

t-'ig. 1.7. S.:hema a

2Yl

circuitului 74LS244

2Y2

2Y3

2 Y4

o o IA4-l

o I IA4-l

I o A 3-a stare

l 1 A 3-a stare

2A4-1

A ,3-a stare

?A4- l

A 3-a srare

:

\ folosit pentru amplificarea/ se ararea magistralelor biclirectionale

. ale microprocesoarelor. terminalelor, din punct e ve ere este

; n fig. l .8, iar fig. l .9 schema a circuitului.

Din schema sa se circuit ul este din 8 perechi de porii

cu 3 bjdirectionale. o intrare dc_yal idare entru toate e o

t intrare pentru stabilirea directiei de transfer. Tabelul l .4 circuilll ui.

Tabelul 1.3. Func!ionarea circuitului 74LS244

-

:l

l

l l)

l

<ll----:---

<11----

;>

Al

A 2

A3

A4

t\5

AO

A.7

AS

DIR

G

Al

A2

A3

A4

AS

A6

A7

AS

DIR

G

Vcc

Bl

132

B3

7

84

4

L 85

s

86

2

4

B7

5 BS :]

GND

f>

SIS IFi\11" 1 :I : WUU Jl'l(C J<:l :SO,\RI;

Fig. 1.8. terminalelor

circuitului 74LS245

Fig. 1.9 Schema a

circuitului 74LS245

I . l ntioducere

IG DrR

A8-I

B8-I

o

o

BS-1

o I

AS- I

I

X A 3-a stare A 3-a stare

-

Tabelul I .4. circuitului 74LS245

Circuitul registru 74LS373

Este un circuit registru cu 8 rangur i, CLI 3 stilri, folosit, n carte, pent

demultiplexarea magistralelor 111icroprocesoarorului 8086. terminal ei

din punct de vedere este n fig. I. I O, iar fig. 1.1 1 scher

a circuitului.

t

ID

Vcc

l Q

2D 2Q

3Q

i

4Q 4D

4

SD

L

SQ

6D

s

6Q Fig. I. l O. terminale Io

7D 3

7Q circuitului 74LS373

8D 7 llQ

3

oe

G

GND

Din schema sa se circuitul este din 8 bistabi le D cu

o intrare de validare pentru toate IOC o intrare pentru

bistabilelor, G, care trebuie fie la I logic pentru a se realiza Tabel ul I.

ci rcuitului .

IOC

G

8Q- IQ

o

o Vechiul

o

I 8D-ID

I

X A 3-a stare

Tabelul I .5. circuitului 74LS373

Toate circuitele descrise acum pot fi n tehnologiile HC, HCT

Al-IC AHCT.

22

oe ---ti>

lD

20

3D

40

SD

60

70

80

G

Circuitul memorie EPROM 27256

SISTI:M1: c .li 1\ I I< .H< >l'Rc H ' l '.Sc >.\fli

-----+ IQ

---!l> lQ

3Q

SQ

Fig. I. 11. Schema a

ciicuitului 74LS373

i

,

t;.

;1

i

,).

Este un circuit memorie EPROMLavnd 32 Ko timpul de acces, !Z

n de yarian@_sub care se de 90-200 ns. terminalelor, din

punct de vedere este n fig. I. 12. i

Ci rcuitul are 15 de adrese, Al4-0, 8 li nii de date, 07-0, o linie de t

Rrogramare, /CE/ IPGM, o linie de validare a /OE, o intrare pentru tensiunea

ue programare Vpp Vcc GND. se citire din circuit,

atunci liniile 07-0 sunt if!!rart;.[Link] trebuie fi e o cu cea de la

Vcc iar citirea datelor se face n conformitate cu diagrama din fi g. 1. 13.

Vcc

-

Al4

07

..

AO

2

.

7

2

5

6

00-

,__ r

Fig. l. 12. termina[e[or

circuitu lui ele memorie 27256

.

-

"

OF.

.

-

CE /PCM

-

Vpp

GND

A J4-0

'1 1'

i

tCE I

l I .

'------t- . - - -

I

I

CE

OE

I

07-0

Fig. I. l 3. Ciclul de citire din ci rcui tul 27256

tAcc - timpul de acces

max.90ns

max. IOOns

max. I20ns

max. 150ns

max.200ns

TCE - ntrzierea de

max.90ns

max. IOOns semnalul de

max. l20ns

max. 150 ns

max. 200 ns

oE - ntrzierea de

max.35 ns

[Link] ns semnalul de validare

[Link] ns

max.50ns

max.50ns.

Tabelul 1.6. Timpii necesari la cicl ul de citire

. A

1

se ctrcuite la o unitate trebuiesc

111a1 mu trmpr. 1mpu care tre u1esc sunt n iar valorile lor m

sunt date n tabelul 1.6. Au fost considerate 5 variante de circuit, cu timpi de acces

Pent ru cl in carte nu faci litatea de programare a

circuitului ca urmare nu va fi

if

24

SISJ'l :,\11 t .1 ,\ll<.llCll ' ll< u :J."< 1 \ HI :

Circuitul de memorie EPROM 27512

Este un circuit memorie EPROM. avnd capacitatea ele 64 Ko timpul de acces,

n de varianta sub care se ele 90-200 ns. Contigura!ia terminalelor, din

punct de vedere este n fig. I . 14.

Circuitul are 16 de adrese. A [Link] linii de date. 07-0. o linie de se lec.U&

(CE. o lini e de pr_Qe:ra1mre, /QE/ Ye.p Vcc GND.

se citire din circuit, atunci liniile 07-0 sunt la intrarea de validare s.i,

j)iogramare trebuie fie O logic iar citirea datelor se face_ cu

cea cl in fig. l. 13. -

.Pentru din carte nu fac ilitatea de programare a

circuitului ca urmare nu va fi

Vcc

.

Al S

.

2

07

7

.

AO

.

5

I

2

00

- .

. CE

-

-.... OE /Vpp

GND

_t

Fig. I. 14. Configuratia terminalelor

circui tului de memorie 27512

.

.

.

Circuitul de memorie SRAM 62256

-+

Vcc

.

Al4

6

I/07

AO 2

.

2

s

6

uoo

-

;;.

cs

-

-

-

OE

-

WE

GND

if

Fig. 1.1 5. terminalelor

circuirnlui de memo1ie 62256

.

.

.

-

Este un circuit memorie SRAM, avnd capacitatea de 32 Ko timpul de acces.

n de varianta sub care se de 45-85_n?.. terminalelor, din

punct de vedere este n figura 1.15.

Circuitul are 15 linii de adrese. Al4-0. 8 lini i de date I/ 08-1, o intrare de

o 111trare de vaffciare a /OE si o de a scrierii,

C!!.f:.. Citirea din circuit se face n conformitate cu diagrama din figura I .16 iar scrierea

n circuit se face n conformitate cu diagrama din fig. 1. 17.

Timpii care trebuiesc la citire sunt n iar valorile lor

sunt date n tabelul 1.7.

Timpii care trebuiesc la citire sunt n iar valorile lor

sunt date n tabelul 1.8.

Al4-0

WE

cs

OE

l IRc I

I f,11< I

'

-------------+--

! --- -------

! Ies I

I loE r

_r-

I

1/07-0

___

Fig. I. 16. Ciclul de citire di n circuitul 62256

1 t wc

I I

IA. . ,\\V I

I

-_,,- _..,_I I

-----,v i

Al4-0

OE ' lcw iLm __ _

i._, _ ________ fjll._Jr - -----

twr I

cs

i f to_, , __ ______ Je> I

:.<L

I I " " I

I I I

I

' lr>1v I Lou

i"1 r 1 ""''----fi i

_ __________ _!,,,---- IN => _

WE

l/08-1

l/08-1

Fig. 1.17. Ciclul de scriere n circuitul 62256

26

. .\IF el' ,\lfl :1tc l l'IH lCl'.S< l \RI '

Cin.:uit HM6?256B-4 HM62256B-5 HM62256B-7 HM6?.256B-8

lRc - durata unui

min. 45 ns min. 55 ns min. 70 ns min. 85 ns

ciclu de citire

t

1

\1< - timpul de acces

max. 45 ns

la citire

max. 55 ns max. 70 ns max. 85 ns

tcs - ntrzierea

de semnalul de max. 45 ns max. 55 ns max. 70 ns max. 85 ns

loE - ntrzierea

max. 55 _:._J de semnalul de max. 30 ns max. 35 ns max. 50 ns

validare

' Tabelul 1.7. Timpii necesari la ciclul de citi re

Circuit HM622568-4 HM62256B-5 HM62256B-7 HM62256B-8

twc - durata unui

min. 45 ns

ciclu de scriere

min. 55 ns min. 70 ns min. 85 ns

tAw - timpul de acces

max. 45 ns

la scriere

max. 55 ns max. 70 ns max. 85 ns

tcw - durata semnalu-

min. 35 ns

lui de

min. 40 ns min. 60 ns min. 75 ns

twp - durata semnalu-

min. 30 ns

lui de scriere

min. 35 ns rnin. 50 ns min. 55 ns

lo1-1z - timpu 1 de

dezactivare a max. 20 ns max. 20 ns max. 25 ns max. 40 ns

tow - timpul de

prestabi li re a min. 20 ns min. 25 ns min. 30 ns min. 35 ns

dalelor

toH - timpul de

poststabilire a min. O ns min. O ns min. O ns min. O ns

datelor

Tabelul 1.8. Timpii necesari la ciclul de scriere

I

;

-Goe

I

i

\i

t!

i

0 . 1.'L t.C" ' ...

"

l 1._1

' ' I \

r::.. ._,

J. t,.I ,_. \ r. (.,: Q.i(.. \

- [Link] '.'.\, .... \\'..:!':. d ...< J ..

-:j - _,

Capitolul 2

MICROPROCESORUL 8086

t: 2.1. Prezentare

'f' Microprocesorul 8086 a n anul 1978 este _

b.i!Lcare a cunoscut o utilizare. lui a fost la scurt timp de o famil ie

de componente: generatorul de tact 8284, controlerul de 8288, coprocesorul

matematic 8087 coprocesorul de intrare I 8089. n anul I 979 a micro-

k procesorul 8088 care a toate caracteristicile microprocesorului 8086 doar

:( magistrala sa de date era de numai 8 a cunoscut o

if mai ales sale n microcalculatorul IBM PC-XT.

Printre caracteristicile microprocesorului 8086 se pot aminti:

r: r:_gistrele interne magistrala de date sunt pe 16

o a adresa dire.s;U...1fade memorie,j.,

il o de lucru {? MHz la cea mai

1. existnd variante pe 4 MHz, 8086-4 8 MHz, 8086-8) ct unei

t structuri interne pe conce12tu!.je care permite aducerea d1

memone, lll avans, a instrucpunllor, n timpul unor ciCiliii accese la magistrale;

o poate acoperi o Cle'"plicafi l celor moduri de [Link] ale

sale: modul minim pentru relativ simple, n care microprocesorul genereau'i.

el semnalele necesare transferurilor cu memoria cu porturile de intrare I

modul maxim, pentru complexe, inclusiv sisteme multiprocesor,

., n care semnalele de comana penfhr ntemotii'1i porturi sunt generate de un

,,; controler de 8288;

o magistralele de date adrese sunt multiplexate iar o parte dintre termi nalele de

au rol dublu; aceasta a pen111s ncapsularea circuitului ntr-o cu

doar 40 terminale.

Istoria microprocesoarelor este dar deosebit de Gradientul

microprocesoarelor a fost este deosebit de mare. microprocesoarelor

de azi sunt superioare de cele ale lui 8086. Sigur atunci cnd se

performantele a 2 microprocesoare se iau n considerare mai mult i factori dar, ntruct nu

'li , '

se dezvoltarea acestui subiect n carte, se vor prezenta doar 2

"'; microprocesorul 8086 include 29.000 tranzistoare pe cnd microprocesoarele

Pentium IV de azi includ peste 30.000.000 tranzistoare,

,,

:!: tactului microprocesorului 8086 este de 4, 5 sau 8 MHz pe cnd

r tactului microprocesoarelor Pentium IV de azi este de 1.2 - 3 GHz.

!, n aceste s-ar putea pune ntrebarea: la ce studiul micro-

procesorului 8086, n anul 2002? Autorul studiul acesttii microprocesor

:t este uti l din cel motive:

t,

I

28

SIS'J'l'i\.11'. ( :t, i\l lCR( Ji'lH J( :l'S( ,,,!{, r

I 2. '.l[icropn>< . :-!UH6

a) familia de microprocesoare Intel are ca microprocesor de ca microprocesor l.

de pornire, circuitul 8086. Toate microprocesoarele care i-au urmat

caracteristici le sale de pe care, evident, le-au dezvoltat completat. ,

b) Toate ntre microsistemele pe 8 cele pe 16 pot fi optim, t.

di n punct el e veuere didactic, la nivelul unui microprocesor 8086 (strlJl:tura hardware,

organizarea gestionarea memoriei. conectarea porturil or, sistemul de ntreruperi ,

pr;gramarea). acestor sunt titile necesare la trecerea spre

sisteme bazate pe microprocesoare pe 32 att pentru de sisteme ct

.,

pentru cei care pun n veri fi astfel de sisteme. 11

2.2. Modurile de lucru terminalele

Microprocesorul 8086 poate lucra n 2 moduri : modul m1111m cel maxim.

a mai multor moduri de lucru se la toate microprocesoarele peste 8 ,,

Cele pe 16 au doar 2 1noduri de lucru iar cele pe 32 au 4 1noduri de lucru.

mai multor moduri de lucru este o n sistemele cu microprocesoare '

romplexe, inclusiv n cadrul PC-urilor, ele ordonnd diferitele stratud de program din :

punct de vedere al privilegii lor. Cu facilitate se separarea

resurselor hardware software ntre diferitele straturi de programe. Astfel, de exemplu,

nucleul sistemului de operare va rula n modul care maximul de privi legiu, avnd "

acces la toate resursele sistemului. Alte module din sistemul de operare, de exemplu

driverele pentru diferite periferice, vor rula E.e un nivel de pri vilegiu mai mic

la mai putine resurse iar erogramele vor rula pe nivelul de privile iu

minim avnd acces la unele resurse. ln general, trecerea mtr-un mod n

altul se face prin controlate.

Mi croprocesorul 8086, este cel mai ,/

rudimentar, din acest punct de vedere. Cele 2 moduri nu privilegi i diferite ci ele

se n anumite hardware, pentru tipuri de diferite iar

trecerea dintr-un mod n altul se fake prin hardware: terminalul MN/ /MX la cart<,

prin I !oaie se cere modul minim iar rin O logic se cere modul maxim.

terminalelor microprocesoru u1 8086 este n figura 2. 1.

n continuare vor fi descrise sem ni le terminalelor. Se va ncepe cu terminalele

care au rol comun n ambele moduri de lucru.

e A 191 S6 - AJQ/S3 ("Address/ Status Bus"): multiplexate cu trei n timpul

l cele mai semnificative linii ale magistralei de adrese iar n ti mpul

T2 - T4, de stare: S6 este ntotdeauna O, SS

indicatorul pentru ntreruperi IF iar S4 S3 registrul de segment utilizat la :

calculul adresei fizice.

o ADI 5 - O ("Address/ Data Bus"): multiplexatt de adrese cu trei

111 starea Tl magistrala de adrese iar n T2 - T4 devine "

de date.

" IBHEI S7 ("Bus HiQh Enable/ Status"): cu trei n timpul Tl

are sau nu loc un transfer a magistralei de date 11

are loc. iar n timpul sH\ri lor T2 - T4 este bit de stare.

TEST

INTR

NMI

RESET

CLK

Vcc

GND

MN//MX---"",,,i

8

o

8

6

--.... - =:E:t=-- -c:u,:=1.:::c.

AD15 -0

/BHE /S7

11-----lli'ls> /RD

IRQ l/GTO CHOL

11-----{J'il:>- / RQ //GTJ (HLD

/ LOCK (!WR)

IS2 (M //IO)

I S l (pT !IR)

ISO (/DEN)

f;> QSO (ALE)

r:;.... QS I (/TNTA)

<3 READY

Fig. 2. l. Terminalele microprocesorului 8086

0

IRD cu trei atunci cnd microprocesorul exeCL

un c1du ae t:1 t1re sau 111trare. - - ---

0 'ff!.[Link] intrare pentru si ncronizarea cu ci rcuitele de rnemo

1

po1tunle 111a1 lente. -

0

INTR Reguest"): pentru cereri de ntrerupere mascabile.

0

("[Link] Test Control"): intrare de instruqiu:;; Vh\ IT: dacfl

1

TEST =

atunci programului n caz contrar microprocesorul <

poale fi pentru sincronizarea microprocesorului cu evenimente extern

0

NM! ( 1n

1

;[Link] Request"): cereri nemascabil

0

RESET ( System Reset ): mirare pentru 1zarea microprocesorului.

CLK ("System Clock"): intrare de tact cu frecven\a de 5 MHz factor (

umplere de l/3.

. n continuare vor fi prezentate terminalelor pentru modul rninir

term111alul MN/ /MX = l.

!;!! 110 ("M_e morv 1_10 Control"): cu trei avnd rol ca S2

modul daca are valoarea I se un ciclu de acces

iar are valoarea O un ciclu de transfel' c

portu nle ele intrare I iesire

. , .

1;-.

s1sT1::vw 1:1

1

i\llC:H< ll'R< i1 :1:.sc>i\ J(J '. I

I

:;o Cap. :Z. lvlicroprocesoiul 8086 31

r: ,_.. .. . ' .1-.:J1_,, '

o /WR ("Write Control"): cu trei atunci cnd microprocesorul ''.

ciclu ele scriere sau "2.3. Structura

" /!NTA ( "Interrupt Acknowledge") : cu trei care se atunci cnd

\,,

'

microprocesorul un ciclu de acceptare a unei cereri e mtrerupere mascabile.

("Address Latch [Link]"): se atunci cnd pe magistrala

de adrese/ date sunt active adresele; se poate folosi pentru demult1 lexarea :

n

e i5f! IR "Data Transmit/ Receive"): cu trei avnd rol ca S I n i

modul maxim: sensu trans eru ui e mag1stra a e ate: I transm1s1e f<'

iar mseamna rece[!tte. .

o /DEN _("Data @able"): Cll transferul de date pe

f!OLD ("Hold Request"): intrare pentru cerere de cedare a magistralelor.

" HLDA ("Hold Acknowleclge"): la cererea de cedare a megistralelor

semnificnd acceptarea acestei cereri; se ce microprocesorul s-a i.J

decuplat de la magistrale. .

tenninale dar pentru modul maxim, terminalul MN/ /MX

sunt descnse rn continuare.

o - O ("Bus Cycle Status"): ie iri cu trei sunt linii de stare care ti

pe care-l va executa micro rocesoru ; ele constituie

controler de 8288, care va enera semnalele de coman pentru

cu memorn e porturile; codificarea tipului de ciclu este n tabelu! 2. 1. f

/S2

o

o

o

o

I

l

I

I

_

/S 1 ISO

o o

o l

l o

l I

o o

o l

I o

I I

Tipul de ciclu

Acceptare a unei cereri de ntrerupere

Intrare

Halt

Aducere cod de

Citire date

Scriere

;

.;>

,J

Tabelul 2. L Codificarea tipului de ciclu la microprocesorul 8086 I

,.

IRQ! IOTO. IRQ! !GTJ ("Request/ Grant Bus Access Control"): linii J

folosite de microprocesor pentru primirea cererii de cedare a magistralelor

t:i n urma unui dialog de tip cerere - acceptare - cele linii

independente.

ILOCK ("Bus Prioriry Lock Control"): cu trei care atunci cnd se

microprocesoru1 nu cedarea magistralelor. Este sarcina unui arbitru J

de extern nu ca o cerere ele cedare a magistralelor

microprocesor amnci cnd /LOCK este activ.

QSJ, QSn: ("fnstruction Queue Status"): care exterio111lui ti pul de

de unitatea de din de n starea J

.>t

8086 [Link] __

enden una de Acestea sunt:

. o de executie " ecution Unit" rolul de a executa instructiunile;

--- . , iii!E::z d

uni ti,t tea de c91112gistralele. Bill "Bus Interface Unit") cu rolul de a

aduce 1i1emorie ea trans era Operanzii ntre llllitatea de

extei'ioi'ul microprocesorului.

Registre

de

date

Registre pentru

accesul n interi-

orul unui segment

Registrul indicatorilor

Unitarea de EU

I

I

I

IP

Registre

interne

Date

BIU

Magis-

trale

externe

I Unitatea de cu magistralele BfU

Fig. 2.2. Structura a microprocesorului 8086

a 2 duce la vitezei de lucru

frr ct de

mai. mace,.. vitezei este mai mare.

l![Link] cl in .familie, (de exemplu 6 la 80386 ).

'? _,_

'

;;1;;11'.i\IF. c:i1 \1 IUll ll'Rl l< .J:S< I.\ IU. j11

I

cu exteriorul. prin intermediu_l __ Jk','

magistrale de [Link]-ae- 20 linii, din care primele 16 sunt multiplexate cu magis_trala d_e :

dale iar ultimele patru, cele mai semnificative, sunt multiplexate cu de stare.

De asemenea semnalele de de stare. f

Unitatea de cu magistralele, BIU

o ... a micrnprocesorului anume aducerea

n avans a Blocul numit este de fapt o memorie FlFO. 1,

avnd capacitatea de 6 1 care. se introduc aduse n avans se

_la.. .cer.e1:e, E.Y., n acest bloc sunt cel doi EU nu

BIU pentru vi:eui1 acces la BIU va aduce n avans o

sunt pe 16 sunt preluate din rnen101ie de la adrese succesive

celeia la care. se ce se EU a rulat o cc -:;1

,i

de a de exemplu o ele .;

salt, BJU din memorie noua o transmite EU l

apoi umple citind n continuare ncepnd cu noua

facilitate_ un important n timp, ntnt::t o suprapunere 1

n timp, aducerea ca;-e; practic, face timpul de

aducere a Acest avantaj este anulat n cazul care

de a dar aceste cazuri sunt rapo11ate la

cazul n care sunt executate una

n timpul unei EU transferul unui operand ntre

el exteriorul microprocesorului (memorie sau port), el lui Bill adresa, pe

16 biri, a operandului tipul de ciclu ce trebuie executat. B!U adresa a

operandului, pe 20 printr-un mecanism ce va fi prezentat la paragraful 2.1.5, utiliznd

n acest scop unitatea UA registrele din interiorul semnalele de

pentru transferul operandului transferul ntre EU exterior.

C<! rerea de operand, din partea lui EU, apare n timp ce BIU un ciclu de aducere

a unei BlU ncheie ciclul nceput apoi noul ciclu.

Unitatea de

Are rolul ele a decodifica executa pe care le extrage succesiv clin

de -i'isfructiuni' -a1 BIU. n urma lor necesitatea unor

operanzi, lui BIU cererea de adresa pe 16 a operandului. n

timpul EU indicatorii de

de este n ntregime neocupat, EU aducerea

instructiunilor de BIU. De asemenea, n cazul unei de salt, EU

lui BIU noua a aducerea acesteia de BlU.

_,, Setul de registre

Spre deosebire de microprocesoarele pe 16 ulterioare, ale altor firme, la 8086

a fost o a registr,elor. dintre ele sunt generale,

majoritatea avnd roluri predeterminate. Se pot n categori i:

o registrele _de date, -

o registrele de segment,

0 regis(rele pentru accesul n interiorul unui segment,

o registrul indicator ele registrul indicatorilor de control.

Setul de registre este [Link] n fig. 2.J.

AX

BX

ex

DX

7 o 7

AH AL

BH BL

CH

CL

DH DL

Registre generale

o

Registru acumulator

Registru de

Registru contor

Registrn Je date

m f,ff:,.,plhn"""'

Registre de segment

15 o

t= '.J i! ; d

Reg;stre pentru acce5td n interiorul unui segment

15

::i Indicator de instructiune

FLAGS :J Registrul indicatoriior

Fig. 2.3 Setul de registre al 111icroprocesorului 8086

Registrele de date

lor sunt cete din Particularitatea lor n aceea

sunt registre pe 16 b1ti el pot fi d d - '

H

.

. r. . _ 1 a 1esate ca oua registre j)e 8 biti recristrul superior

ce t11 1erior L Orie d' I ' "'

da-- . .b .' : _a.ie intie e fi 11nplicat 111 aritmetice logic<

1

au atn specifice. prezentate n tabelul 2.2.

Registru

Functiune

AX

"

. intrare I ee cuvnt

AL

intrare I J)e octet,

AH

pe octet

BX

Translatare

ex

Contor pentru cu siruri, bucle

CL

Contor pentru

DX lnmultire intrare I

Tabelul.'.!..::?. Registrele de cln1e ale microprocesoru lui 8086

'4

'lf

)<\ . . s1sn:.M1 <'. l

1

1\l l1'J((

1

1'R< >< :1-:sc ),\lll'. 2. ;\1icroproccsorul 81J86 35

Registrele de segment . ..

1

SF ("Sign Flag" J, bit 7: indicator de semn: con rine bitul cel mai semnificativ al r.:wltatului

Pentru a adresa un de I Mo microprocesorul di3pune de 20 lm11 de aeCi rangul de semn; va fi 1 pentru rezultat negativ O pentru rezultat pozitiv.

Dar registrele inrerne akunicrogrocesorului 16 bip _Qec1 nu pot memora ?. H ' OF ("Overtlow Flag"), bit 11: indicator de se atunci cnd apare

a constituit-o memoriei. 1.n segmente de cate 64 Q_Ot tu:\ registrelor ca urmare a unei aritmetice cu operanzi cu

- - 6 b L t dat m1croi:irocesorul semn; va fi I atunci cnd apare un transport sau un mprumut n/ din rangul de semn.

adresate prin intermediul unei configurati i pe I , dresel e de '"1

oate lucra cu Qatru de co?, dy doua d_e A A i': sunt

celor atru s_unt : on mute 1n re Momii

111

cate o TF bit 8: indicator pentru modul pas CLI pas: va con(ine l,

se oo(in"a reseli:diiice-se va prezentam .paragraful 2. 1.5. . A w -ihicroprocesorul va lucra n modul Cll .

. Re istrul cs .. adresa de rnceput a segrne1:i_tu!u1 de _

111

car_e se a o IF ("Imemtpt Flag"}, bit 9: indicator pentru ntreruperi: va l. microprocesorul

.. _Pi!j_ini. a adresa_ o cei:eri!e de ntrerupere ce sosesc pe intrarea fNTR: n caz contrar Ie

CS cL--cel ai registri.t'Jur-indicator de e,,.ista .multe fi o QF ("I)irection Flag"), bit 1 O: indicator de se la cu

"se"mente de cod activ-area tmuia realizndu-se pnn m CS a adresei este 1, ad resa operandului din este fiecare transfer iar

n6'eput 3 segment. _Regi strul SS. adresa d_e nceput a este O, adresa operandului din este dupa fiecare transfer.

D_S ES 111ceput a doua segmente de date. i'.. PUSH F permit tuturor indicatorilpr prin

.

1

- . teriorul unul segment ._, r, ,c, . depunerea lor m prelucrarea readucerea lor m registrul indicatorilor. In plus,

Registrele pentru accesu mm - - d' CF IF OF - d'

.

1

. .

1

it pentru m 1catom , exista mstrucpunr cu

cu registrele de date, reg1strel_e a e _

Ele se pot diviza mdex w

,:esej .. -- - cadrul segmentelor de date . 2.4. C1cl urrle .. I',,

t. I. ES S

0

folosesc n general Io operatule cu Sl

deci n rae_ort cu reg1s g: e _ . , . . . ,

iar Dl adresa opernndulut d , ln conti_nuare se va prezenta modul de a semnalelor microprocesorului n

Registrele indicator deplasamentul adresei la care. se afia_-un.

0

?eran.

cadrul unor cicluri de Toate transferurile ntre microprocesor memorii sau

codrul' segrnentului de SP la care :e afla vartul porturi se fac n conformitate cu aceste cicluri.

raportat la ss iar BP-indic! deplasamentul adresei la care se un _ opeian lt11. L'.n [Link] cu Tl la T4, o stare

cadrul segmentului . o perioada a _unpulsulu1 de tact. Intre T4 se pot insera de

d

. t t ' ne IP "'' notate cu Tw . atunci cnd memoria sau porturile sunt prea lente, prin intermedili

I I d" t e ms ruc 1u , "' - --

Reg stru 111 1ca or ' .

semnalului READY. Impulsul de tact are facturul de umplere egal cu J/3. Pentru

adresa celeia care se Contme f generarea lui se poate utiliza circuitul 8284.

- -- 1 . . t. . . ; "e se va executa n cadrul segmentulut de coc . fi BIU - . I . I . 1- ,

adresei se at nmea cai . . , . . . 7 . . . . . . a a doar [Link] EU 11 acest lucru sau cnd

tontinutul ltu IP se combma cu cel al lut CS.; J aduce antici pat 1n care nu vreo acl1v1tate a BIU cu exteriorul

- .

1

d' t . 1 de conditii control FLAGS 'i se numesc inactive. ntre cicluri la pot exista oricte stari inactive.

Registru m ica on or ' F. 2 4 t- EU BIU 1 I

. . fi f ve ig. prez111 a activrtatea 111 cazu unei a drn o

este un registru pe 16 doar 9 sde_mrn d.t .. Ei JMP, de salt, de o instructiune MUL. sunr descrise n

. ;- I 8086 Di ntre 6 sunt m 1caton e con [Link]. r:: -

1

. . "'

111d1cator11 microprocesoru u1 . . ' . t. fi te_s.tati nlrucat semnalelor de depinde de modul n care

t' de microprocesor a unor ope1 po

1

. 1}

1

. . . . . . .

m urma . . . -t nucroprocesoru, se vor prezenta c1clunle de pentru modul m1111111 apoi

pot lua decizii n d_e __ .lor. sunt. . . . pentru modul maxim.

CF. ("Carry Flag"), bit O: indicator de se atunci cand apaie U\t . . . . . ..

uunsport sau un mprumut din/ n rangul cel mat sem111f1canv; . f Ciclul de c1t1re date tnlrare pentru moclt.I minim

PF ("Parity Flag"), bit 2: indicator de paritate: se atunci Este prezentat n fig. 2.5. Ciclul ncepe cu starea T J n care microprocesorul

unei opera(ii aritmetice sau un octet cu de _ cndt pe magistrala de ad1 ese o pe 20 De_ semnalul

AF ("Auxi liary Carry Flag"), bit 4: 111d1cator de transpo1.t auxi hai se a?:iveaza transferul va folos i Jllinatatea mat a mag1strale1 de date.

apare un transport sau un mprumut n aritmet ice cu operanzi m cod circuitele de memorie porturi cer ca adresa fie pe durata

ntre octet. . J c1clulu1. este necesar ca magistrala de I date fi e ele

ZF ("Zero Flag"), bit 6: indicator de zero: se rezultatul unei fie ntr-un registru. se face cu semnalul ALE, folos it ca

aritmet ice sau logice este zero. , semnal de strobare.

,.

SISTEi\11" 1 :1 i .\III .ll< >1'\lt lCF.S\ l ,\l{I ' i

Cidu de . . , de -

I inactive_ i 1pag1st1 ala i1.

Pj<lt

-Ui}L __ UiJL t

EU Q) ! EU d"" 2 ootofi. din (Cod"I MLIL)I u

. !

0

n 70-77 si-in \ 0 I {fJ ti

s1u I

4

. \..:},/ . I . m

. . d I EU de 1nstructn1111,

i) ntruct s-a executat o - e sat,. l . i 4 n "

2) este ool, ca urmare BI U executa c1c lll l a ma?:" . f 4

3) EU preia doi din ?oi cai e va [Link] . '

4) BIU doi m care va fi plm (6 - . . MUL

" " care EU executa mstruct1unea ,

5) BIV este liber timp de 62 : 69 Stan, tunp lll ' . ' - . . . . r " f

6) EU preia doi di_n ncep.e urmato::ue1 mstruc,1uni, '-;

7) BIV doi n care este d111 nou plm. _

Fig. 2.4. lui EU 81 U pentru o .

Ciclul instruc- I

tiunii JMP , .

Ciclu de

TI

I T3 4 T4 rl Tl

T l T2

CLK I I I >+ :

- .w.J -, .

/BHE , I - . I I \ 1. [

1 I

Cap. 2. i\licroprocesorul 81ltl 6

La nceputul Tl. semnalele M/ 110 DT/ / R sunt 1.011

ciclului in curs. starea lor tot timpul ciclului. Li nia M/ / I

indica transferul curent se cu memoria. M/ / IO= I snu c:u pllrl UI ilc

!IO = O. Linia DT/ / R va indica microprocesorul transmite, DT/ /R = I

DT/ IR= O. .

ln timpul T2. de pe liniile Al 91 S6 - A 16/ SJ se schi

reprezentnd informa!ie de stare. Liniile S3 S4 care registrul de scg

folosit la calculul adresei fizice pot fi utilizate, prin decodificare, la selec(ia

segment de memorie sau la unui segment de accesele ncauLnr i

de stare n T3 T4. Tot n starea T2. li

AD 15 - O trec n a tre ia stare se semnalul /RO, indicnd se execut

ciclu n care microprocesorul semnalul / DEN. indi

[Link] datele pot fi plasate pe

Pe frontul al tactului din starea T3, mi croprocesorul

READY. este l , n starea T4 iar este O va insera de

n care de pe lini i se din nou linia REP

cnd aceasta devine l . n starea T3 se preiau datele, iar la nceputul T

semnalele /RO /DEN indicnd ciclului. La acel

T4 se liniile DT/ / R M/ / 10 pentru ciclul

Ciclul de scriere date n modul minim

Ciclul este prezentat in fig. 2.6. El este cu cel de citire int1

avnd

o pe lini ile ADl 5 - O, de adrese se va genera imediat, n starea T2,

care se va nscrie n memorie sau po1t, ca aceste linii mai n a trei stai

o linia DT/ IR va avea nive l l de nivel O n cazul anterior;

o la nceputul T2 se semnalul de /WR, mai devremt

/RO n cazul anterior, indicnd exteriorului microprocesorul un c

de scriere sau citire;

e semnalul /DEN este act ivat mai devreme ca n cazul anterior.

Ciclurile de n modul maJCim

ADA1LsE-0 . 11_ 1

Prezentarea se va face comparativ cu ciclurile anleriore. indicnd diferentele existe

:

J! ...... i: pe magistrala de adrese I date are ca n caw l cicluri Io

\

1

=""""=*"""'....., modul minim. De asemenea semnalele ALE, /DEN OT/ IR au

M//lO

modul minim el e nu mai sunt generate de microprocesor ci de circuitul contn

i !

I 7 de 8288.

i f t Fig. 2. 7 semnalele de stare /S2 - O. Acestea circui tului 8'.2 88 ce

i I i \ de ciclu va executa microprocesorul.

I i r= Fig. 2.8 comparati v semnalele de /RD, IWR pentru modul mii

=

4

- -i- i ! -t . cele corespondente, generate de circuitul 8'.288 pentru modul maxim. semi

_.

1

1. _ \ .:. de de scriere avansate, I AM WC pentru memorii /AIOWC pentru port

I _ "--- = = "- - utile in cazurile in care semnalele de pentru scriere normale nu au du1

1

-==r= . """(

1

' I I d . . I RA l'v1 .

-l-- - __

1

. -- - . .. ._-_,

1

._1'-""""==1:

1

.

' nu pot t1 folosite dect pentru comanda acelor circuite la care inscrierea (

- - T ------ ... .. . ! de front ul posterior al semnalului ele

Fig. '.2.5 . Ciclul de citire date intrare pentrn modul minim

IRD

DT //R

/DEN

READY

38

u

\ 1)

SIS'l l':'vll <:LI 1\IJUH ll'l{( J<:J:S1 >.\l< l 1 Cap. 2. l\iicroproccsornl 8086

T2 I .._' --T4=-=-! I TI ' CLK T I 1' T2 I T3 !'=i =-=T-4- ']'I

CLK T I =--'n......_1.. -11- /RD i LJ_J_,...._._-t-

A19/S6 - - \/

I !WR

ADI S-0

I

__ l MRDC, 1+-

1

r---

1 /AMWC,/Alqwc I- J ....JJ

ALE

M /!T.O

I I j 1 r =--

mR--f' I t /MWTC, flO\fC [ lf 4 J

=-- J 4- Fig. 2.8. Semnalele de penhu modul maxim

-

DT /IR

1

r

I 'i Semnalele de pentru scriere, normale sunt utile atunci cnd 11sl'rlrrn11

I

i I este de frontul anteri or al semnalului de (de cxc111plt1 111

..--'"""""i"""'- circuite RAM dinamice). Este datelor nainte de frontul antc1irn ni

L I acestor semnale.

READY I j ________ ___ _______ I _: ____ 1:f Ciclul de acceptare a unei cereri de ntrerupere mascabile

-- -. .. . .... -.. -j-..-._.. . r--, 1 . Figura 2.9 ciclul de acceptare a unei cereri de ntrernpere mascabi lc. C1l'111 l

CLK

ALE

/S2-0

_ - . J ..... _ ___________ 1J L! -----------L .. _La nceputul [Link]. de .adrese'. date tre<.:L' t11 11

--r----- ... i I 1

1

& treia stare m stare pana la tennmarea c1clu!u1. Apoi se sc1111111l11I

Fig. 2.6. Ciclul de scriere date in modul minim

TI T2 T3 T4

!. r - ]-,--+

t

I . . ="=

- --T--------- ., I

' I - --=l I i - I

Fig. 2.7. lnformatia de stare pentru modul maxim

f. /INTA (generat de microprocesor n modul minim sau de circuitul 8288 n 111ocl11I

maxim) indicnd exteriorului a acceptat cererea de ntrerupere. In al doilea subc1rl11

o senrnalul7 1NTA md1dnd eXferiorului un vec101 du

I TI ntrernpere pe magistrala de date, linii le D7 O. Acesta este fumizat de sursa cere11i dt'

ntrerupere, n general min intermediul unui circuit spe<.:ializat entru ntreruperi 82S9A.

Microprocesorul senmalul /LOCK indicnd faptul nu cc l111l'11

!t magistralelor ntre cele subcicluri. microprocesorul este n mod minim. se1111111l11l

va fi activat doar intern dar o cerere HOLD nu va fi n

= Microprocesorul 8086 are facilitatea de cedare a magistralelor. In modul min1111,

I pent:u magistralelor este intrarea mic1,11

-,- -i procesorului la aceasta cerere este trecerea 111 a treia srare a mag1strale1 111ul t1plcxute n

L

de comnnda: /RD, /\VR. Ml /IO, /DEN, DTI I R activarea liniei de rllspum

=+-- HLDA. Dezactivarea cererii HOLD va duce la dezactivarea HLDA lu

controlului asupra magistralelor n starea celei n care s-a deznc'liv11l

!i semnalul HLDA.

'-;ISTl'.MI'. Ll' Ji'I(< li :l'.S< l ,\ 10"

TI

CLK

Fig. 2.9. Ciclul de acceptare a unei cereri de ntrerupere mascabile

f

..

I

p

n modul maxim, cedarea I preluarea magistralelor se face pe linii (;

independente una de /RQ/ /GTO /RQ/ /GTl are loc n unna um11 dialog m ;:

trei faz.e: li

n prima cel care cere controlul asupra '?'_QI ;

/GTi, care este intrare pentru microprocesor, semnalul avand semmficat1e de ce1.e1e, . ,

n a doua microprocesorul linie. semnalul av1:d

de acceptare a cererii cedare a magistralelor; activarea se face fie la

ciclului la curent fie ntr-o stare microprocesorul s-a .

deconectat de la magistrale; .

n ultima linia fRQ/ /Gi este din nou de cel care a cerut magistralele, '

semnalul avnd de la controlul asupra magistralelor.

Linia IRQ/ /GTO este asupra li niei IRQ/ /GTl.

simultan pe ambele lini i, microprocesorul /r:--Q/ /GTO ce a

reprimit magistralele, la cererea !RO/ /Gl Daca

la cererea /RQ/ /GTI, cea de pe linia O va fi doar dupa mche1e1ea d1alogul u1

referitor la linia l. _ _ . .

Microprocesorul va relua magistralele doar. [Link] a stan

liniei HOLD sau din momentul pnm1rn 1mpulsulm de pe lm1a

IRQ/ /Gi. . - A 'd ..

o cerere de pe linia HOLD sau fRQ/ /GTt, nu luata .m const e1a1e

n timpul senmalului RESET dar ea se RESET va fi

imediat Aceasta este o care poate li folos ita la de

memorie ncepnd cu adre5a FFFFOH nainte ca act1v.1ta'.ea.

ce rnicropiocesorul a cedat magistralele, EU.

din ele instruqiuni cnd devine necesar un etc lu la sau yana cand

devine gol, aceasta fiind o facil itate l:entru .v1t.eze1. .

o faci li ta te a micro procesoru lui 8086 consta 111 blocai ea mag1stl ale Io'. exte1 ne.

Microprocesorul semnal ul /LOCK atunci cnd nu cedarea magistralelor.

c;,,p. 2. Microprocesorul

Este sarcina unui arbitru de (ciicuitul 8289 n familia lui 8086) nu lase aj1

la microprocesor cereri de cedare a magistralelor n timp ce semnalul /LOCK este a1

Microprocesorul semnalul /LOCK n predeterminate (n lin

ciclului de acceptare a unei cereri de ntrerupere) n timpul unei instruc1

de prefixul LOCK. Prefixul dintr-un octet plasat naintea

compun Semnalul /LOCK se de BIV la cererea lui

ce acesta a executat prefixul LOCK activ pe durata exec1

respective. Semnalul ILOCK este activat intr-o situat ie predefinit

anume n ciclul de acceptare a cererii de ntrerupere mascabi le.

O a /LOCK este posibil itatea pe care o are mi

procesorul de a executa un acces la care nu se poate executa cli

prin mai mul te cicluri la In acest caz ce ace

trebuie fie de prefixul LOCK, ntruct n caz contrar s-ar putea ca oper

fie ntre cicluri la de un procesor mai prioritar,

transferul se ncheie cu date false.

Un exemplu clasic este se un sistem multiprocesor cu res1

partajate, starea unei resurse fiind de un "semafor" care este un indic;

comandabil prin program. El poate fi, de exemplu, un rang al LU1ei de memo

Microprocesorul 8086 are posibilitatea de a testa semaforul acesta

resursa este l activeze, astfel ca semaforul indice n continuare st<

ocupat a resursei, riscul de a fi ntrerupt intre ciclul de citire a semaforului cel

Pentru aceasta se poate folosi programul de mai jos, n care

XCHG att citirea ct semaforului :

HOV 1; se registrul AL

WAIT : LOCK XCHG MEM, P.L; se face schimbul ntre MEM, unc

se semaforul registrul AL; n AL se va afl

vechiul al semaforului iar n MEM se va af

noul al

'.::'EST 1, 1'.L; se semaforul: lui AL est

diferit ele O se ntruct resursa a fost ocupe

n caz contrar se cu accesul la

JNZ [Link].I T

prefixului LOCK, accesul la semafor sa se fac

permite accesul altui procesor la n caz contrar ar de conflict dt

cum din exemplu: procesorul i semaforul, resu

este care un acces pentru activarea semaforului dar simultan acest ac

este dori t de procesorul i + l. mai prioritar, care va activa semaforul, astfel resu

n timp ce procesorul i care nu activitatea procesorului i + l va con tir

de acces la resursa aceasta procesorul ui i +I.

, 2.5. Organizarea gestionarea memoriei

Microprocesorul 8086 poate {Vlo ele memorie. (aptului to

sunt pe 16 el__!l!! intern adrese mai lungi de 16 b

ce duce la o ele I Mo n de 64 Ko. Micropniceso

-12 s1s1 l:,\lf: c:u llfl<:R< )j>J{(JU: Sc) \RI.

poate lucra la un moment dat cu 4 asemenea segmente, a?resele lor de ncerrnt

t Cap. 2. Microprocesorul HIJ86

Pentru o erati i cu accesul_J_a_un element din irul sui se face rin intermediul

registrelor OS pentntlidresa de SI pentru deplasament iar accesul la un elemen

din se. face prin mtermediul registrelor ES Dl.

-U

se n registrele de segment. !:

Segmentele sunt blocuri de memorie care se pot suprapune. ca ij

adresele lor de nceput sa fie multiplu de l 6. Segmentar<::a memoriei are avantajele:

'" este programarea fiecare modul poate ocupa unul sau mai r

multe segmente putnd fi dezvollat independent unul de

relocarea a programe lot; pentru aceasta este necesar ca acestea ;f.

lt.

nu afecteze registrelor segment nu referire la din

afara segmentului; programul poate fi plasat oriunde n memorie prin modificarea

registrelor de segment;

'{

o se poate utiliza un mare de stive, prin plasarea adresei de nceput a

segmentului n registrul SS a vrfului stivei n SP.

Printre dezavantajele se pot enumera:

n lungimea programelor introduse de dimensiunile segmentelor;

adresa se din mecanism care timp f

deci duce la o a vitezei de lucru. tt

( Figura 2.1 O mecanisrritil de calcul al adresej Cele configuratii J

'I de progran:ator

se registru .segment este d_eplasat la stanga

cu Jatru rangun, plasandu-se O 1n ratigunle hbere apoi se aduna deplasamentl-!l

o >\1nndu-se astfel o pe 20 bl'iLExemplu: presupunem (SS) = 2590H

(SP) = I 248H. Adresa a vrfului stivei este: 25900H + J 248H = 26B48H.

{;

f

ii

f:

j

t

o

I

15

registru segment - registru pentru accesul n interiorul segmentului

este programatorul are posi b!litatea, de a modifica combinatie.

1_!_ o de ansamblu asupra n exemiJ!ul

prezentat cele 4 segmente sunt disjuncte.

Segment

de cod

.

...... ___

Segment

cs

de

ss -

DS

ES

Segment

... de date

....

Segment

de date

suplimentar

Valori mari

de adrese

Valori mici

------------

\ Atfrosn 1

15

CS,SS,DS "" ES-100001

' j ----------

de adrese

4

Fig. 2.11. Segmentarea la microprocesorul 8086

.

f . [Link] 8086 poate lucra cu operanzi pe bi t, digit, octet, cuvnt, dublu

cuvant sau bloc. In cazul n care se operanzi pe cuvnt, acesta ncepe la o

transferul se face ntr-un singur cicl u iar acesta ncepe la o

cicluri pentru transfer. Conform conventiilor firmei INTEL,

"l la ulterioare din famil ie, cuvntul este memorat cu octetul

li E:Ja1 sem111ficat1v la o de valoare mai iar dublul cuvnt este memorat

19 O cu la o de valoare mai De exemplu

Adresa C . J f AB02H este memorat la C!resa 24680H octetul 02h este memorat

, . 'li. la cu adresa 24680H octetul ABH este memorat la cu adresa 24681 H.

Fi g. 2.10. Calculul adr_esei fizice la microprocesorul 8086- ,-y - _ I li . de memorie direct adresabi l de 8086 este de I Mocu adresele de la

. . . . . . . . OOO_?CJH la se poate face la nivel de octet dar la nivel de cuvnt,

a codul unei mtotdeauna de a f a e.:1sta re_fentoare la adresa de nceput a cuvintelor. transferul unui cuvnt

1-1,n,1 tn..!:.Cj lSlrul CS iar 111 IP. Pentru un 1:1 se folosesc _ss: a. este un singur ciclu pe cnd transferul unui

pu11!1 u ocfresa de SP, pentru deplasament, atunci_ cand se ".u neal 1111at, a este cicluri procesul

SS BP att1nci cnd se accesul la un operand aflat n segmentul i fiind transparent pentru utilizator reflectndu-se doar n vitezei. n ele

i

SISTl :. r-- 11 : i;ti MI CH< lPltr J< . l.S( l,\RF

f

4-1

memorie zone, fig. 2. I 2, una la nceput, in domeniul OOOOOH - 0007FH

la n domeniul FFFFOH - FFFFFH care au speciale,.

fiind fie dedicate fie rezervate. Prima tabela de intrerupen iar a doua

secventa de initializare a unui sistem cu 8086 ntruct, dupa dezactivarea

P ESET: microprocesorul un acces la adresa FFFFOH.

Rezervat

Dedicat

Disponibil

Rezervat

Dedicat

FFFFFH

FFFFCH

FFFFBH

FFFFOH

00080H

0007FH

00014H

000!3H

OOOOOH

f

t

<!

f

p

f

j,

p

r

f Fig. 2. 12. Organizarea memoriei la microprocesorul 8086 t

Fizic, memoria poate fi n blocuri de maxim 512 .Ko: blocul_ ar

blocul imear. par cuprinde do_E cu [Link] cel np,par

doar cu adrese imP<l.!! Blocul par este coiieC'fla 1u111atatea a

dedate, 0 7 - O iar cel impar este conectat la a ?e date,

/

D 15 . 8. Liniile de adrese A 19 - I sunt folosi le pentru a selecta cte o sunultan

din ambele blocuri. Transferul ntre selectate magistrala de date se face doar )

sub controlul a li nii, AO / BHE, n conformitate cu tabelul 2.3.

/BI-LE AO Se

o o A 111 bi i

o I Octet superior la/ de la

I o Octet infe1ior la/ de la

1 1 transfer

Tabelul 2.3 pari impari la microprocesorul 8086

Figura 2.13 divizarea memoriei n cele blocuri. Pentru la.

operand octet aflat la o linia AO va val!cla b!ocul par, iar lnml

/BHE va invalida blocul impar. Va avea loc transferul intre adresata

a maoistralei de clate. Pentru accesul la un operand octet aflat la o

/inia AO va inv:lida blocul par, ntruct AO = I, n timp ce /BHE =O va [Link] bl?cul impar.

Va avea loc transferul ntre a mag1strale1 de date.

Cap. 2 . .\licrnprncesoru! 8086

FFFFFH

FFFFDH

Al9-l Dl5-8 /BHE

FFFFEH

FFFFCH

OOH

07-0

Fig. 2.13. memoriei n blocuri la 8086

n cazul unui transfer al unui cuvnt aliniat, ambele blocuri vor fi val.

simultan de liniile AO = / BHE =O. Va avea loc transferul ntre cele acin

ntrega de date.

n cazul unui acces la un cuvnt nealiniat sunt necesare ciclrn

La primul ciclu, /BHE =O AO = I, ntruct adresa este deci s

transfera octetul de la a magistralei de date. A<

este octetul mai putin al operandului. apoi al dodea ciclu m

a,2resa este deci A0;-0 7BRE = l, se va transfera ciClefi

la adresa pe a magistralei de date. Acesta este octetul

semnificativ al operandului. Aceste sunt executate de microprocesor, inel

a [Link] ale registrelor inte1

Modul de organizare gestiune a memoriei descris mai sus, impune o amu

de ordonare a programului.

2.6. Sistemu! de intrare I

Microprocesorul 8086 permite conectarea pol'turilor de imrare I at

de memorie ct n de int rare I separat de cel de memorie.

Spatiul de VE este sugrapus peste primul segment [Link] 64 KO, n zona OOOOC

OFFFFH iL_ este accesibi l prin inslrucpuni de J/E cledicate, IN OUT. 8086 pen

conectarea att a porturilor pe 8 ct a celor pe 16 Un port pe 8 pont

conectat att pe pa11ea ct pe pa11ea a magistralei de date.

conectarea unui egal de porturi pe cele ale magi str

de date dar numai din motive de

Adresele de po11 trebui e seama de conectarea liniilor ele date ale portull

magistrala de date a microprocesorului. s-a conectcirea pe j umatalea 1meri(

a acesteia al'unci adresele ele port toate pare iar s-a conect<