Documente Academic

Documente Profesional

Documente Cultură

Capitolul 4 AMP - Partea A III-a (Tipuri de Instructiuni) PDF

Încărcat de

Dani MandacheTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Capitolul 4 AMP - Partea A III-a (Tipuri de Instructiuni) PDF

Încărcat de

Dani MandacheDrepturi de autor:

Formate disponibile

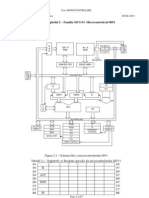

…:::4.

3 Tipuri de instrucţiuni:::…

-din punct de vedere semantic µP împarte setul de instructiuni în 5 subseturi:

1) transfer de date

2) prelucrări date

3) instrucţiuni de control al programului

4) instrucţiuni de intrare/ieşire

5) instrucţiuni de control al µcalculatorului

4.3.1 Transfer de date

(d) (s), d=destinaţie, s=sursă

-sursa e copiată la destinatie, iar după ce transfer sursa rămâne neschimbată.

Caracteristici :

1. un µP realizeaza acele tipuri de transferuri conform clasei din care face parte

2. sursa si destinatia pot fi registre atribute de arhitectura si/sau locatii de memorie

3. dimensiunea sursei si destinatiei sunt identice

4. identificarea corecta a sursei si a destinatiei se face utilizand un mod de adresare

specific tipului procesorului respectiv, cu restrictii

5. criteriul de performanta pentru aceste instructiuni de transfer este un factor de

merit intre semantica si formatul instructiunii

Curs preluat de la Domnul Profesor Corneliu Burileanu

exercitiu 1

-fie µP cu organizarea memoriei liniara, memorie formata in octeti, adrese fizice pe 16 biti,

R1 si R2 registre pe 8 biti fiecare.

PUSH R1R2; (SP) (SP)-1 -actualizare varf stiva

((SP)) (R2) -trimit cate 8

(SP) (SP)-1 -actualizare varf stiva

((SP)) (R1) -iar trimit cate 8

POP R1R2 (R1) ((SP))

(SP) (SP)+1

(R2) ((SP))

(SP) (SP)+1

exercitiu 2

-fie µP cu organizarea memoriei liniara, memorie formata in octeti, adrese fizice pe 16 biti,

R1,R2,R3,R4,R5,R6 registre pe 8 biti fiecare, concatenate doua cate doua.

-perechea R3R4 este preincarcata cu adresa fizica a primului element a unui sir

numit sursa

-perechea R1R2 este preincarcata cu adresa fizica a primului element a unui sir

numit destinatie

-perechea R5R6 este preincarcata cu un numar reprezentand numarul de elemente

din sirul sursa

Repeat

((R1,R2)) ((R3,R4)) - adresarea indirecta a sursei si a destinatiei

(R1,R2) (R1,R2) + 1 – autoincrementarea adreselor

(R3,R4) (R3,R4) + 1 – autoincrementarea adreselor

(R5,R6) (R5,R6) + 1 – autoincrementarea contorului

Until (R5,R6) = 0H – ciclu cu test final

-tipic CISC

Transfer

MOV [1064H],AX ((DS)↕0H+1064H) (AL)

((DS)↕0H+1065H) (AH)

MOV [2000H],DS ((DS)↕0H+2001H)↕ ((DS)↕0H+2000H) (DS)

MOV [BX],491FH ((DS)↕0H+(BX)) 1FH

((DS)↕0H+(BX)+1) 49H

Registrul DS nu e utilizabil pe jumatati !

Curs preluat de la Domnul Profesor Corneliu Burileanu

segmentul de stiva nu e redirectionabil, dar cel de date este

(PUSH intai actualizez si apoi efectuez transferal,POP – efectuez transferal, apoi

actualizez)

XLAT (translate,instructiune pe 8 biti)

(Al) ((DS)↕0H+(BX)+(BL))

MOVSB / MOVSW (move stream byte, move stream word)

-primitive de transfer sir

-aici trebuie initializat DS cu adresa segment unde se afla sirul sursa, ES va fi destinatia

segmentului,DF-ne spune cum trebuie parcurs sirul,intr-un sens sau in celalalt iar CX

contine numarul de elemente din sirul sursa

daca destinatia sirului se suprapune cu sirul s pe un nr de elemente atunci vom realize o

redirectionare, adica vom parcurge sirul dintr-o directie si apoi din cealalta

SS- nu se redirectioneaza

DS – se redirectioneaza

4.3.2 Instructiuni prelucrari de date

operatii monadice (un singur operand)

- cu acumulator (d) (d)

- fara acumulator (d) (s)

operatii diadice (doi operanzi)

- cu acumulator (d) (d)(s)

- fara acumulator (d) (s1)(s2)

operatie logica aritmetica oarecare.

Operatii accumulator tipic CISC

Operatii fara acumulator tipic RISC

Caracteristici :

1. tipuri de operaţii uzuale sunt:

a) logice : SI, SAU, XOR, complement fata de 1 si de 2 (CF1 si CF2)

b) aritmetice: adunare, scădere, înmulţire , împărţire, incrementare, decrementare

c) deplasari si rotatii, înmulţire , împărţire la 2

2. dimensiunea rezultatului si a operanzilor este aceeasi (cu exceptia înmulţirii şi împărţirii)

Curs preluat de la Domnul Profesor Corneliu Burileanu

3. identificarea operanzilor si a rezultatului se face folosind modurile de adresare ale μP

respective, cu restrictii.

Operanzii si/sau rezultatul in registre pot fi atribute de arhitectura sau/si in memorie.

4. în semantica acestor instructiuni intra si modul in care sunt afectate fanioanele aritmetico-

logice.

Există 4 moduri de afectare a fanioanelor

a) fanioane neafectate indiferent de operatii ( nu pot fi folosite în a lua decizii

ulterioare)

b) fanioane afectate ulterior

c) fanioane care sunt fie setate fie resetate dupa o operatie indiferent de rezultat

d) fanioane care in functie de tipul operanzilor şi de valoarea operanzilor sunt setate

sau resetate

5. Criteriul de performanta pentru aceste instructiuni este un factor de merit intre semantica

operatiei si timpul de executie

!!! CISC - timpul de executie depinde de complexitatea operatiei

(ex: . are 5 stari,: 150 stari)

exercitiu 4

-fie µP cu registrele R1, R2 pe 8 biti, cu fanion de transport optional

(R1,R2) (R1,R2)+(R3,R4) [+(C)]

instructiuni ADD si ADC (add+carry)

exercitiu 5

-fie µP cu acumulator dedicat A, si (s) un alt registru

-semantica unei comparatii care nu se stocheaza in acumulator ci ma uit in fanioane

(A) – (s) if (A)=(s) then (Z) 1

if (A)>(s) then (C) 0

else (C) 1

ADC AX,[BX]

- (AX)(AX)+((DS)↕0H+(BX)+1)↕(AX)(AX)+((DS)↕0H+(BX))+(CF)

(add+carry)

-acumulator AX

-operanzi implicit si relative la baza directa

-segmentul de date poate fi redirectionat

Curs preluat de la Domnul Profesor Corneliu Burileanu

SUB DH,[BP+4] (DH) (DH)-((SS)↕0H+(BP)+4)

-al doilea operand in stiva directa

-DH acumulator , 8 biti

-pot sa redirectionez pentru ca exista BP (SS+SP) - nu am voie

(SS+BP) – am voie

inca o primitive:

CMPSB/CMPSW = comparatii intre doua siruri

-trebuie sa initializez ES,DS,SI,DI,DF

4.3.3 Instructiuni de control al programului

-test

-salturi ( decizii si cicluri)

TESTE:

A. testeaza un fanion

B. testeaza combinatii logice fanioane

C. testeaza un bit oarecare dintr-un operand oarecare

D. testeaza linii de intrare “serie”

SALTURI:

- dupa cum urmeaza sau nu unor teste:

- neconditionate

-conditionate

- dupa modul de adresare (mult mai retrictiv)

CISC foloseste patru salturi:

-adresare directa

-adresare scurta

-adresare relativa

-adresare indirecta prin registre

-dupa cum memoreaza sau nu valoarea curenta a numaratorului de program

-salturi propriu-zise

-apeluri de subprograme

-dupa complexitate

A. salturi 2 posibilitati

B. salturi 3 posibilitati

C. cicluri

criteriu de performanta: factor de merit: tipul de salt si tipul de test

Curs preluat de la Domnul Profesor Corneliu Burileanu

exercitiu 6

-fie µP cu organizarea memoriei liniara CISC, memorie formata in octeti, adrese fizice pe

16 biti, numerator program PC si indicator de stiva SP de 16 biti

Moduri de adresare folosite pentru salturile propriu-zise

adresare absoluta

(PC) adr

in care adr face parte din formatul instructiunii

adresare relativa

(PC) (PC) + disp8 | disp16

in care disp8 si disp16 fac parte din formatul instructiunii

adresare indirecta prin registru

(PC) ((ri,rj)+1) ↑ ((ri,rj))

adresare scurta (in “pagina 0”)

(PC)l adr8

(PC)h 0H

Moduri de adresare pentru apelurile de subprograme

CALL adr; (SP) (SP) – 1

((SP)) (PC)h

(SP) (SP) – 1

((SP)) (PC)l

(PC) adr -salt adresare directa

Obs1. folosire implicita a stivei primare (PUSH,POP,CALL,RET)

RET (PC)l ((SP))

(SP) (SP) +1

(PC)h ((SP))

(SP) (SP)+1

Obs2. nu stii exact locatia din stiva, asta inseamna ca nun e scuteste de obligatia de a tine

cont de numarul de accesari a stivei

CAL,PUSH,RET – GRESIT!!!

CAL,PUSH,POP,RET -corect

Obs3. în limbaj de programare nu exista nici un mod implicit de a transfera parametrii cand

se face apelarea de program

Curs preluat de la Domnul Profesor Corneliu Burileanu

4.3.4 Instructiuni de intrare/iesire

-transferuri de date la si de la porturi

aceste instructiuni presupun ca μP face o harta a porturilor distincta de harta

memoriei

IN d,port; (d) (port)

OUT port,s; (port) (s)

-dimensiunea sursei si destinatiei identice

Caracteristici speciale:

- d sau s acumulator implicit si dedicat

- harta porturilor este mult mai mica decat harta memoriei

- moduri de adresare foarte restrictive pentru porturi : directa si indirecta

prin registru

Criteriu de performanta acces rapid la porturi

exemplu.

Intel x8086 IN

OUT

- în mod real, d si s sunt acumulatorii impliciti AL,AX,EAX

- porturi organizate pe octet ca memoria

- harta porturi – 64 kporturi/ octet

- adresare directa : 1 octet 256 porturi / octet

- adresare indirecta prin registru: DX 64 kporturi/octet

4.3.5 Instructiuni de control al μP

- instructiuni care sincronizeaza μP cu anumite stari ale lui

stare de asteptare

functionare pas cu pas

acces direct la memorie

partajarea resurselor sistemului cu alte procesoare

- accesul la anumite fanioane (setare,resetare), in special fanioanele care

semnaleaza actiuni specifice ( ca de exemplu validarea cererilor de întrerupere)

Curs preluat de la Domnul Profesor Corneliu Burileanu

Concluzii set de instructiuni ale µP

1. un procesor CISC are un set de instructiuni bogat

2. o parte din instructiuni sunt complexe

operatii cu siruri, cicluri cu contor(loop), operatii aritmetice complicate

3. setul de instructiuni puternic influentat de alte atribute de arhitectura: utilizarea

registrelor, tipuri de transfer de date, organizarea memoriei, tehnici de adresare

4. instructiuni CISC formate diferite (moduri de adresare , organizare memorie) si au

timpii de executie foarte diferiti

Curs preluat de la Domnul Profesor Corneliu Burileanu

S-ar putea să vă placă și

- Laborator 10Document8 paginiLaborator 10eujenioÎncă nu există evaluări

- Arhitectura CalculatoarelorDocument21 paginiArhitectura CalculatoarelorRocsiBalanÎncă nu există evaluări

- Curs 4 - Programarea in Limbaj de Asamblare PDFDocument26 paginiCurs 4 - Programarea in Limbaj de Asamblare PDFRaduStefanÎncă nu există evaluări

- Intel 8080Document15 paginiIntel 8080Maxim MirzencoÎncă nu există evaluări

- Curs Asm 7Document18 paginiCurs Asm 7Lavinia IoanaÎncă nu există evaluări

- Programarea Cu MicroprocesoareDocument23 paginiProgramarea Cu MicroprocesoareBadescu IonutÎncă nu există evaluări

- Curs 4 - Program Area in Limbaj de AsamblareDocument26 paginiCurs 4 - Program Area in Limbaj de AsamblareDHM1305Încă nu există evaluări

- Extinderea Setului de InstructiuniDocument22 paginiExtinderea Setului de InstructiuniVlad BotnaruÎncă nu există evaluări

- Ac RăspunsuriDocument19 paginiAc RăspunsuriRosca DoinitaÎncă nu există evaluări

- 9 - Instructiuni de TransferDocument26 pagini9 - Instructiuni de TransferMister AnonimÎncă nu există evaluări

- Proiect: Proiectarea Unui Microprocesor RISCDocument24 paginiProiect: Proiectarea Unui Microprocesor RISCCristian PlescaÎncă nu există evaluări

- Cheatsheet Colocviu CN2 UltimDocument2 paginiCheatsheet Colocviu CN2 UltimVlad PopescuÎncă nu există evaluări

- Cursul 6 - Setul de Instructiuni (Instr. de Transfer, Aritmetice)Document30 paginiCursul 6 - Setul de Instructiuni (Instr. de Transfer, Aritmetice)Marcel LefterÎncă nu există evaluări

- Curs 4 - Programarea in Limbaj de AsamblareDocument26 paginiCurs 4 - Programarea in Limbaj de AsamblareAlex ArdeleanuÎncă nu există evaluări

- UPUS ExamenDocument17 paginiUPUS ExamenAlexandru PiscaÎncă nu există evaluări

- Raspunsuri ASCDocument3 paginiRaspunsuri ASCVlad ZahiuÎncă nu există evaluări

- Cursul 4 - Formatul Instructiunilor. Moduri de Adresare. Limbajul de Asamblare.Document27 paginiCursul 4 - Formatul Instructiunilor. Moduri de Adresare. Limbajul de Asamblare.Ion CatanÎncă nu există evaluări

- Probleme EA +cal 10 Februarie 2021Document1 paginăProbleme EA +cal 10 Februarie 2021Silviu MunteanÎncă nu există evaluări

- Grile AMPDocument82 paginiGrile AMPAndrei Serban100% (1)

- Ilovepdf MergedDocument124 paginiIlovepdf MergedStefanÎncă nu există evaluări

- Cursul 4 - Formatul Instructiunilor. Moduri de Adresare. Limbajul de Asamblare.Document27 paginiCursul 4 - Formatul Instructiunilor. Moduri de Adresare. Limbajul de Asamblare.Radu DelaAfumatiÎncă nu există evaluări

- Grile RezolvateDocument4 paginiGrile RezolvateAndrei100% (2)

- Subiecte Teorie Nea NicuDocument2 paginiSubiecte Teorie Nea NicuBogdan G. StefanÎncă nu există evaluări

- Lab Ac 2Document12 paginiLab Ac 2Sebastian OglageÎncă nu există evaluări

- Moduri de AdresareDocument9 paginiModuri de AdresareCristina SerbanÎncă nu există evaluări

- Probleme1 1Document14 paginiProbleme1 1danielsb10Încă nu există evaluări

- AMP Capitolul 3Document12 paginiAMP Capitolul 3Dani MandacheÎncă nu există evaluări

- IOCLA - Curs 03 - Arhitectura x86Document17 paginiIOCLA - Curs 03 - Arhitectura x86RisteaÎncă nu există evaluări

- Sisteme Cu Microprocesoare Unitatea de Invatare 5Document12 paginiSisteme Cu Microprocesoare Unitatea de Invatare 5samycatalinÎncă nu există evaluări

- Curs Asm 6Document23 paginiCurs Asm 6Vlad PetreanÎncă nu există evaluări

- Familia MCS-51Document17 paginiFamilia MCS-51Ana MariaÎncă nu există evaluări

- Plas 50Document7 paginiPlas 50ion marianÎncă nu există evaluări

- Bti MasmDocument10 paginiBti MasmNarcisa BusuiocÎncă nu există evaluări

- ProblemeDocument13 paginiProblemeRexy RexÎncă nu există evaluări

- Grile Examen BTIDocument10 paginiGrile Examen BTIbiancanita57Încă nu există evaluări

- Curs 11 Setul Extins de Instructiuni x86Document21 paginiCurs 11 Setul Extins de Instructiuni x86eugen lupuÎncă nu există evaluări

- 4 Book30 Capitolul 4Document14 pagini4 Book30 Capitolul 4Aurelian RaducuÎncă nu există evaluări

- Curs11 StivaDocument20 paginiCurs11 StivaAlexandru TimofteÎncă nu există evaluări

- Instructiunea XLATDocument7 paginiInstructiunea XLATDaniela CcÎncă nu există evaluări

- Cuprins Curs Circuite Integrate DigitaleDocument3 paginiCuprins Curs Circuite Integrate Digitalemihai_daneaÎncă nu există evaluări

- Arhitectura Calculatorului DidacticDocument13 paginiArhitectura Calculatorului DidacticMădălina HapciuÎncă nu există evaluări

- Curs SPIDocument36 paginiCurs SPIalinupÎncă nu există evaluări

- RaspunsuriDocument11 paginiRaspunsuriPan De LaÎncă nu există evaluări

- MesteacănDocument189 paginiMesteacănAndrei SerbanÎncă nu există evaluări

- Instructiuni Ale Limbajului de AsamblareDocument19 paginiInstructiuni Ale Limbajului de AsamblareMagda BulacuÎncă nu există evaluări

- Curs 3AMDocument46 paginiCurs 3AMmarianagalbiazaÎncă nu există evaluări

- Programarea Calculatoarelor Limbajul PASCALDocument221 paginiProgramarea Calculatoarelor Limbajul PASCAL36Încă nu există evaluări

- (InfoIasi) (FII) (ACSO) (PH) Introducere in Limbaj de AsamblareDocument21 pagini(InfoIasi) (FII) (ACSO) (PH) Introducere in Limbaj de AsamblareDiana TodiroaeÎncă nu există evaluări

- Microcontrollere Curs 2016 Corneliu BurileanuDocument91 paginiMicrocontrollere Curs 2016 Corneliu BurileanuFeta MirayÎncă nu există evaluări

- Lab1 ACDocument13 paginiLab1 ACDark Light100% (1)

- Memoria Externa de Date La MCS-51Document26 paginiMemoria Externa de Date La MCS-51Denisa OlaruÎncă nu există evaluări

- Arhitectura Sistemelor de Calcul - Lab5Document15 paginiArhitectura Sistemelor de Calcul - Lab5AÎncă nu există evaluări

- AC Lab 6 PDFDocument3 paginiAC Lab 6 PDFIonut AlexandruÎncă nu există evaluări

- Baze de Date AvansateDocument270 paginiBaze de Date AvansateMihail AndronicÎncă nu există evaluări

- Magistrala SPIDocument10 paginiMagistrala SPIone_blanche6175Încă nu există evaluări

- Cap 1Document19 paginiCap 1Dan BulbucÎncă nu există evaluări

- Curs 6 APDocument6 paginiCurs 6 APBuțurcă DănuțÎncă nu există evaluări

- Subiecte Posibile Pentru Lucrare AMP 2018-2019 PDFDocument1 paginăSubiecte Posibile Pentru Lucrare AMP 2018-2019 PDFDani MandacheÎncă nu există evaluări

- Capitolul 4 AMP-partea A II-a PDFDocument9 paginiCapitolul 4 AMP-partea A II-a PDFDani MandacheÎncă nu există evaluări

- Subiecte Posibile Pentru Examen AMP 2018-2019 PDFDocument1 paginăSubiecte Posibile Pentru Examen AMP 2018-2019 PDFDani MandacheÎncă nu există evaluări

- Capitolul 4 AMP-partea I PDFDocument4 paginiCapitolul 4 AMP-partea I PDFDani MandacheÎncă nu există evaluări

- Subiecte Posibile Pentru Examen AMP 2018-2019 PDFDocument1 paginăSubiecte Posibile Pentru Examen AMP 2018-2019 PDFDani MandacheÎncă nu există evaluări

- Capitolul 1-AMP - Partea A III-ADocument9 paginiCapitolul 1-AMP - Partea A III-AEdward PtrÎncă nu există evaluări

- Capitolul 1 AMP Partea IDocument7 paginiCapitolul 1 AMP Partea IDani MandacheÎncă nu există evaluări

- Anexa2amp PDFDocument2 paginiAnexa2amp PDFDani MandacheÎncă nu există evaluări

- Capitolul 1 AMP-Partea A II-ADocument7 paginiCapitolul 1 AMP-Partea A II-AOana DiaconescuÎncă nu există evaluări

- AMP Capitolul 3Document12 paginiAMP Capitolul 3Dani MandacheÎncă nu există evaluări

- Amp 6aDocument1 paginăAmp 6aMadalin Cristian FloreaÎncă nu există evaluări

- Exercitii AmpDocument4 paginiExercitii AmpDani MandacheÎncă nu există evaluări

- Anexa 1 AmpDocument13 paginiAnexa 1 AmpMadalin Cristian FloreaÎncă nu există evaluări

- ParcariDocument3 paginiParcariDani MandacheÎncă nu există evaluări

- 04 M Depasirea SoferiDocument8 pagini04 M Depasirea SoferieltoaderÎncă nu există evaluări

- Antisemitismul Universitar in Romania (1919-1939)Document653 paginiAntisemitismul Universitar in Romania (1919-1939)Moldova.since.135980% (5)

- 03 PrioritateaDocument16 pagini03 PrioritateaSalavastru Mihai100% (3)

- !!!!!!!!!!!Document6 pagini!!!!!!!!!!!Dani MandacheÎncă nu există evaluări

- 04 M Oprirea Stationarea ParcareaDocument10 pagini04 M Oprirea Stationarea ParcareaHincu DanÎncă nu există evaluări

- 01 Semnalizarea Rutiera PDFDocument0 pagini01 Semnalizarea Rutiera PDFSergiu PopÎncă nu există evaluări

- 02 Reguli de CirculatieDocument12 pagini02 Reguli de CirculatieAndrei VanturÎncă nu există evaluări

- Boia, Lucian - Mitologia Stiintifica A ComunismuluiDocument235 paginiBoia, Lucian - Mitologia Stiintifica A ComunismuluiJennifer James100% (3)

- Main CIADocument101 paginiMain CIAAlexandra MireaÎncă nu există evaluări

- Caietele Lui CioranDocument201 paginiCaietele Lui CioranGrama Silviu100% (4)

- Albert Camus - NeintelegereaDocument28 paginiAlbert Camus - NeintelegereaCristina100% (17)

- Tema CIADocument2 paginiTema CIADani MandacheÎncă nu există evaluări

- Referat Lab2 - Badescu Dorin-Stefan - 432DDocument5 paginiReferat Lab2 - Badescu Dorin-Stefan - 432DDani MandacheÎncă nu există evaluări

- Tema Suplimentara CIADocument1 paginăTema Suplimentara CIADani MandacheÎncă nu există evaluări

- IEM Cap Erori AplicatiiDocument8 paginiIEM Cap Erori AplicatiiDani MandacheÎncă nu există evaluări