Documente Academic

Documente Profesional

Documente Cultură

Microprocesoare in Telecomunicatii

Încărcat de

Gheorghe CiochinaDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Microprocesoare in Telecomunicatii

Încărcat de

Gheorghe CiochinaDrepturi de autor:

Formate disponibile

4.

Memorii semiconductoare

Dispozitivele de memorie semiconductoare prezint dispozitive realizate

sub form de microcircuite integrate destinate pentru

memorizarea informaiei n form de coduri binare.

Dispozitivele de memorie semiconductoare au un

domeniu larg de utilizare: n calculatoarele electronice, n

dispozitivele numerice pentru prelucrarea informaiei.

1.1. Caracteristicile tehnice

Volumul de memorie cantitatea maxim de informaie care poate fi stocat

de microcircuit. nitatea de msur [bii], [baii].

1K = 1024 = 2

10

1M = 1024K = 2

20

1G = 1024M = 2

30

1 bait = 8 bii

Modul de organizare a masivului de memorie se indic cte celule

conine microcircuitul !i ci bii sunt n celul.

NK x m bii

m numrul de bii ntr"o celul#

N numrul de celule.

De exemplu:

$%$ &'$ %4( ) * bit.

Viteza de lucru caracterizeaz frecvena maxim de lucru a

sistemului n:

- regim de nscriere a informaiei +timpul de acces " ,acces nsc.-#

- regim de citire +,acces citire-#

- timpul de acces general +,acces gener.-.

Consumul de energie se caracterizeaz prin puterea disipat sau

curentul consumat.

Caracteristicile constructive +tipul cristalului, numrul de contacte,

dimensiunile-.

Condiiile de exploatare +diapazonul de temperaturi a mediului

ambiant, umeditatea, nivelul de vibraii, etc.-.

1.2. Clasificarea memoriei semiconductoare

Memoria semiconductoare poate fi clasificat dup mai multe

principii.

Dup posibilitatea tergerii operative a i!ormaiei "i mi#ro#ir#uit$

a% memorie operativ (RAM random acces memor.) permite de a

efectua n mod operativ citirea !i nscrierea informaiei.

b% memorie fix (ROM read onl. memor.) este destinat numai

pentru citirea informaiei.

Memoria /0M pierde informaia la deconectarea alimentrii

calculatorului, dar memoria /1M pstreaz informaia la deconectarea

alimentrii calculatorului.

Dup mo"ul "e orgai&are a a"resrii #elulelor "e memorie$

a% microcircuite cu structura de tipul *D +unidimensional-#

b% microcircuite cu structura de tipul 2D#

#% microcircuite cu structura de tipul 3D.

4umrul maxim de celule ce poate fi adresat poate fi:

N#elul'max'=2

$ (1D%

N#elul'max'=2

2

$ (2D%

N#elul'max'=2

3

$ (3D%

Dup a##esul la i!ormaie$

a% memorie cu acces secvenial +consecutiv- n care pentru a localiza

informaia necesar, trebuie de analizat consecutiv tot volumul de

informaie sau o parte a lui.

b% memorie cu acces aleator permite de a localiza printr"o singur

operaie informaia necesar.

b.. memorie cu adrese permite localizarea informaiei prin

adres.

b.!. memorie asociativ permite localizarea informaiei dup

coninutul ei prin analiza concomitent a tot volumului de memorie.

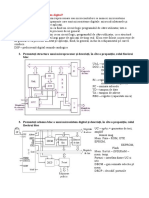

)ig' 141' Clasificarea memoriei semiconductoare

Structura microcircuitelor de memorie

semiconductoare

Ma5oritatea microcircuitelor de memorie +/0M, /1M- sunt

organizate dup principiul memoriei cu adrese. ,ot volumul de memorie

este mprit n celule. 6iecare celul poate fi adresat cu a5utorul unui cod

binar de adres. Dup structura intern, memoria cu adrese poate fi:

- de tipul *D +cu o dimensiune-#

- de tipul 2D +cu dou dimensiuni-#

- de tipul 3D +cu trei dimensiuni sau memorie cu pagini-.

7tructura *D se utilizeaz la microcircuitele cu volum mic de

memorie. 7tructura 2D este mai complicat !i se utilizeaz n

microcircuitele cu volum mare de memorie +8m*%9 celule-. 7tructura 3D

se utilizeaz pentru a realiza blocuri cu volum foarte mare de memorie.

"eprezentarea funcional a unui microcircuit de memorie este

reprezentat n fig.**$.

)ig'11*' "eprezentarea funcional a unui microcircuit de

memorie

+0,+-1 intrri de adres#

Di0,Dim-1 intrri de date#

Memorie semiconductoare

Memorie operativ RAM Memorie fix ROM

cu acces serial cu acces aleator

memorie

asociativ

memorie cu

adres

cu structura

1D

cu structura

2D

cu structura

3D

memorie

static

memorie

dinamic

memorie cu

mascare

PLA

memorie

programabil

memorie

reprogramabil

cu tergere

cu ultraviolet

cu tergere

electric

A

0

A

1

.

.

.

A

n-1

M

(RAM)

(ROM)D

00

D

01

.

.

.

D

0m-1

D

i0

.

.

.

D

im-1

./ semnal de nscriere#

01 semnal ce arat permiterea accesului#

D00,D0m-1 datele de ie!ire.

N#elule = 2

2max = 2

m

m numrul de bii.

:;nd semnalul :7 este activ, adica < logic, este permis accesul

la microcircuit +operaiile de nscriere, citire, !tergere-. Dac :7 este pasiv,

adica * logic, atunci celelalte semnale nu influeneaz starea

microcircuitului.

7emnalul =/ efectueaz nscrierea codului Di n celula cu

adresa respectiv. 7emnalul de nscriere exist numai pentru memoria

/0M.

2.1. Memorii cu structura de tipul 1D

)ig3'114' #tructura intern a unui microcircuit tip 1D

$rincipiul funcionrii%

6iecare ie!ire a decodificatorului serve!te pentru a adresa o

celul de memorie. :ircuitele de nscriere citire formeaz semnalele

pentru nscrierea !i citirea informaiei. 7tructura *D este o structur liniar,

deoarece toate celulele se afl ntr"o singur linie n raport cu acest

decodificator. :u acest microcircuit pot fi efectuate operaiile de nscriere,

pstrare !i citire a datelor.

1% &nscrierea informaiei.

>entru a nscrie informaia e necesar:

- de aplicat adresa celulei n care dorim s nscriem

informaia#

- se aplic :7 ?<.

0plic;nd un cod de adres la intrrile de adres, c;nd :7 ? <, se

permite ie!irea la una din ie!iri, ie!irea e n dependen de codul aplicat.

>resupunem la intrare codul este nul !i :7 ?< se permite accesul numai la

elementele din prima celul.

@a intrrile Di se aplic codul ce trebuie nscris, de exemplu:

*,<A<. >;n c;nd =/ este pasiv, nu vor avea loc nscrierea. Dup ce are

loc adresarea tuturor celulelor, se aplic =/ ?< !i atunci =/ permite

trecerea informaiei prin circuitul de nscriere !i citire. ,rec;nd informaia

pe la fiecare element, ea va a5unge numai la elementul care este adresat +n

exemplul nostru prima celul-. Dac dorim s nscriem informaia n alt

celul, scBimbm adresa :7?<, =/?*, aplicm la Di codul ce trebuie

nscris !i apoi =/?<Ae.t.c.

:odul Di se va nscrie n elementele celulei adresate de codul de

adres.

2% Citirea informaiei.

>entru citire este necesar:

" De aplicat adresa celulei din care dorim s citim

informaia#

" =/?*#

" :7?<.

0tunci la ie!irea D< vom obine codul din celula respectiv.

3% $strarea informaiei.

>entru pstrarea informaiei este necesar de pstrat :7?*.

'vanta(ele%

simplitatea structurii

viteza mare de lucru, deoarece citirea !i nscrierea se efectueaz ntr"

un singur tact.

)ea(unsurile%

dup asemenea structur pot fi confecionate microcircuite cu volum

mic de memorie. 0!a microcircuite conin un numr mare de

terminale.

Bloc de nscriere-citire

DC

adrese

'

'

'

C#

'

*

'

'

n+

e

.

e

.!

e

.m

* 2

n

e

2 2

n

e

Celula 2

. . .

1

2

z

n

'

'

'

Circuit de

nscr.-

citire

Circuit de

nscr.-

citire

Circuit de

nscr.-

citire

D

i

1

D

0

1

D

i

2

D

0

2

D

im

D

0

m

,"

Celula

m

n

e Celula

2

'

'

'

2.2. Structura de tipul 2D

Cn microcircuitele cu volum de memorie mai mare de *9D se folose!te principiul de structur 2D. 0ceasta permite de a mic!ora n 5umtate numrul

terminalelor de adres.

#tructura intern a unui microcircuit tip 2D este artat n fig.**E.

)ig'115' #tructura intern a unui microcircuit tip 2D

$rincipiul funcionrii%

Cn acest microcircuit avem un registru de linii la intrarea cruia

se aplic o magistral care conine nF2 bii.

2mem' = 2

#elule

0cela!i numr pleac la D:. ,ot la el acioneaz un semnal :07

+selectarea adresei coloanelor- este activ, adic < logic, c;nd prin

magistrala de adres se transmite adresa coloanelor. @a /G de linii pe lng

magistral se mai aplic semnalul /07 +selectarea adresei rndurilor -. :;nd

n magistrala de adrese este transmis adresa liniilor, atunci semnalul /07

este activ. De la /G de linii informaia este transmis la D: de adres a

liniilor, unde la ie!irea lui vom obine un semnal unitar.

Matricea elementelor de memorie conine 2

nF2

2

nF2

celule, n total

2

n

. 6iecare celul este adresat printr"un element HI, care ntrune!te o ie!ire

a D: de linii !i una a D: de coloane. 7emnalul de la ie!irea elementului HI

se folose!te la adresarea celulei. Cn afar de aceasta mai este un bloc de

nscriere !i citire, care organizeaz nscrierea datelor de intrare +m bii- !i

citire a datelor de ie!ire n celula aleas.

Ideea funcionrii este bazat pe faptul c adresarea celulei se

efectueaz n dou etape :

6' >rin magistrala de adrese se transmite 5umtate din adresa

celulei +adresa liniilor-.

0ceast informaie este nsoit de semnalul /07 !i se nscrie

adresa n registrul de linii cnd /07?<.

66' >rin aceia!i magistral se transmite a doua 5umtate a

adresei celulei +adresa coloanelor-. Cn acest caz semnalul

/07 este pasiv !i adresa dat nu se nscrie n /G, ci a5unge

la D: de adres a coloanelor. 0ctiv;nd semnalul :07,

obinem un cod la ie!irea acestui D:. @a intrrile

elementului HI corespunztor vor fi prezente dou semnale

active !i elementul dat va adresa celula respectiv de

memorie. Cn acest moment cu a5utorul blocului de nscriere"

citire se poate de efectuat nscrierea sau citirea datelor din

celula selectat.

'vanta(ele%

numrul intrrilor de adres a fost mic!orat de dou ori.

)ea(unsurile%

adresarea celulei se efectueaz n dou etape !i astfel se mre!te

timpul de acces a informaiei !i se mic!oreaz viteza de lucru.

RG

adrese

linii

DC

adrese

linii

& &

& &

&

&

.

.

.

.

.

.

.

.

.

. . .

. . .

. . .

DC

adrese coloane

ormator de semnale

nscriere - citire

D- D

*

.a celula

de memorie

.

.

.

Adresarea la celula 1

! n

!

n/!

0

!

n

2

n

adrese

2.. Structura de tipul D

#tructura intern a unui microcircuit tip 3D este artat n fig.**J.

$rincipiul funcionrii%

@a /G se aplic adresa. 0ctiv;nd semnalul > are loc nscrierea

adresei paginii n /G. 0dresarea se efectueaz n trei etape:

1' 7e transmite adresa paginii concomitent cu activarea

semnalului > !i la una din ie!irile D: obinem un semnal

activ. 0cest semnal activeaz intrarea :7 a paginii

respective.

2' >rin canalul de n"bii are loc concomitent transmiterea

adresei n blocul de adresare a celulei. @a ie!irea acestui

bloc vom obine un semnal activ care va pleca la aceia!i

celul de pe toate paginile.

3' Cn fine va fi adresat celula paginii la care :7 va fi activ.

Informaia va putea fi citit sau nscris numai de pe

pagina activ.

'vanta(ele%

volumul de memorie este mrit.

)ea(unsurile%

se mai adaug nc dou etape +adresarea paginii !i adresarea celulei-.

. Memoria operati!". #lementele pentru

memori$area informa%iei

Memoria operativ /+M permite de a efectua n mod operativ

operaii de citire !i nscriere a informaiei. /0M serve!te pentru pstrarea

datelor !i programelor utilizatorului.

Dup tipul elementului de memorizare a informaiei se deosebesc:

memorie static#

memorie dinamic.

Cn memoria operativ +/0M- static, elementul pentru

memorizarea informaiei este un bistabil. n bistabil realizat pe tranzistoare

M17 pentru memorizarea operativ static are structura din fig.**K.

$rincipiul funcionrii%

>resupunem c la drena 8,* avem potenialul zero care

nimere!te la grila 8,2 !i"l ncBide. 0tunci dac 8,2 este ncBis, potenialul

drenei este aproximativ egal cu potenialul alimentrii, adic avem * logic,

care nimere!te la 8,* !i"l descBide. :;nd se efectueaz adresarea +operaia

de citire sau nscriere- are loc transmiterea unui semnal activ, dar canalele

8,3 !i 8,4 sunt ncBise !i deci nu"i posibil adresarea. Cn acest caz

elementele bistabilelor se afl n stare de pstrare.

Dac la adresare avem * logic, atunci cBeile la 8,3, 8,4 se

descBid !i astfel are loc descBiderea accesului acionrii asupra bistabilelor.

6ie c la a* avem * logic, iar la a2 < logic. Lero logic vine la grila 8,* !i"l

ncBide, iar unu logic vine la 8,2 !i"l descBide. 0stfel bistabilul a trecut n

alt stare.

'vanta(ele%

informaia odat nscris se poate pstra oric;t de mult, p;n la

scBimbarea ei, desigur s fie pstrat alimentarea.

acest tip de memorie are un timp de acces mic !i respectiv viteza de

lucru este mare.

)ea(unsurile%

conine multe elemente, adic suprafaa cristalului va conine un

numr mic de bistabile !i deci un volum mic de memorie.

RG

adr

ese

linii

!

Bloc de

adrese

a celulei

.

.

.

adr

ese

$

$!

$!

n

Mat

rice

2D

DC

adr

ese

linii

Blo

c

de

ns

crie

re

citir

e

D

i

D

*

n

n

R1

"#

a

R2

$%&

$%1 $%2

$%'

adresare

a1 a2

citire

nscriere

citire

nscriere

(

)0*

+

)1*

.2. RAM dinamic"

Cn memoria dinamic elementul de memorizare este un tranzistor M17. Informaia se memorizeaz

sub form de sarcin electric ce se acumuleaz pe capacitatea grilei tranzistorului M17 +vezi fig.*2<-.

)ig'120' 1lementul de memorie pentru memoria "'M dinamic

pe baza unui tranzistor M2#

$rincipiul funcionrii%

Ditul de informaie se nscrie pe grila tranzistorului 8,*. ,ranzistoarele 8,2, 8,3 permit accesul la

informaia din elementul de memorie +8,*-.

- Cnscrierea: se aplic semnalul activ M*N la intrrile de adresare. 0cest semnal descBide cBeile 8,2 !i

8,3. >rin 8,2 semnalul de nscriere nimere!te la grila 8,*.

- Memorizarea: la intrrile de adres se aplic O<O , iar 8,2 !i 8,3 sunt ncBise. 0re loc ntreruperea

legturii dintre a

*

!i grila 8,*. 0re loc pstrarea potenialului nscris pe un timp limitat de ordinul *ms.

Deoarece 8,3 este ncBis nu putem citi semnalul nscris.

'vanta(ele%

volumul memoriei este mai mare de 4 ori n comparaie cu memoria static.

timpul de acces la memorie este de aproximativ $<"*<<ns.

)ea(unsurile%

memoria dinamic necesit regenerarea periodic a informaiei. /egenerarea const n renscrierea

informaiei n toate celulele de memorie cu o frecven mai mare dect *9Pz. Cn microcircuitul de baz

exist un dispozitiv autonom de regenerare.

&. Memoria fi'" ROM

Memoria !ix /7M prezint dispozitive de memorie n care informaia poate fi nscris odat

sau de c;teva ori. Cn procesul de funcionare al dispozitivului n care ea este montat, informaia poate fi

numai citit. Dup principiul de memorizare a informaiei exist urmtoarele tipuri de memorie fix:

a% Memorie cu mascare informaia este nscris la uzina productoare ntr"un proces fotolitografic. 0!a

tip de memorie conine deobicei informaie standart a!a ca tabele de codificare a alfabetelor,

simbolurilor, cifrelor, e.t.c.

b% Memoria programabil.

#% Memoria reprogramabil.

"% Matrice logice programabile 3$.'4 prezint complete de elemente logice, bistabile, realizate pe un

singur cristal fr etapa final de interconectare. >e baza lor se poate de obinut dispozitive compacte,

adic ntr"un singur circuit.

&.1. Memorie pro(rama)il"

Memoria programabil 8/7M permite nscrierea informaiei o singur dat. Informaia se

nscrie la etapa programrii. Cnscrierea are loc prin distrugerea unor elemente speciale din masivul de

$%1

$%&

a

2

$%2

a

1

$%1

nscriere

citire

adresare

R

,

"#

a

)1*

memorie +distrugerea selectiv-. nul din exemplele de structur intern a unui microcircuit de memorie

programabil este prezentat n fig.*2*.

#tructura intern%

)ig'121' #tructura intern a unui microcircuit de memorie programabil

$rincipiul funcionrii%

Qlementele de la intersecie reprezint o diod !i o conexiune fuzibil n serie. Microcircuitul conine

un D: de adrese, ie!irile coloanelor ce formeaz o matrice sunt ie!iri de date.

1% &nscrierea informaiei 3programarea4.

@a programare ie!irile de date servesc ca intrri de date. :u a5utorul codului de adres se alege celula

ce se va programa. :elula reprezint toate elementele conectate la ie!irea activ a D:. Cn fiecare element

trebuie nscris un bit de informaie. >resupunem c aplicm la intrrile de date D

<

, D

*

,AD

m"*

codul *<A*.

Dac aplicm semnal activ la :7, la o ie!ire a D: apare un semnal activ, iar D: e cu ie!iri inversoare

!i semnalul activ va fi zero. Dac la D

<

?N*N , atunci curentul va circula ca n figur. Dioda conectat la

borna a doua a D: este descBis !i curentul va distruge conexiunea fuzibil. Distrugerea conexiunii

fuzibileduce la nscrierea M*N logic.

2% Citirea informaiei.

@a citire se aplic codul de adres !i :7 ? <. 1binem zero la celula necesar, iar intrrile D

<

, D

*

,A

D

m"*

se folosesc pentru citire, deoarece legtura fuzibil este distrus, n acel loc vom citi M*N.

'vanta(ele%

pstreaz informaia la deconectarea alimentrii.

)ea(unsurile%

informaia nu poate fi scBimbat, microcircuitul nu poate fi reprogramat.

viteza mic de lucru, comparativ cu /0M, /1M are viteza de zeci de ori mai mic.

&.2. Memorie repro(rama)il"

Memoria reprogramabil 98/7M permite de a scBimba de mai multe ori informaia

programat datorit existenei unui mecanism de !tergere. Dup principiul de !tergere exist:

- !tergere cu ultraviolet +fig.*22-#

- !tergere pe cale electric.

'

*

'

.

.

.

'

m+

DC

de adrese

!

.

.

.

!

m

"- $

D

n

D

1

D

0

R

,

Cone(iune

.uzi/il0

Qlementul pentru memorizarea informaiei este un tranzistor M17 cu gril flotant. :onstrucia

scBematic a acestui element este reprezentat n fig.*22.

)ig'122' Construcia sc5ematic a elementului pentru memorizarea informaiei

6n baza unui tranzistor M2# cu gril flotant

>entru !tergerea informaiei este destul ca elementul s fie luminat cu radiaie ultraviolet. 7ub

aciunea acestei radiaii, n dielectric apar purttori de sarcin !i se formeaz canale de scurgere a sarcinii

negative de pe gril.

0lt tip de memorie reprogramabil este memoria cu !tergere electric. 0ceast memorie permite de a

!terge selectiv cu a5utorul unui semnal electric anumite pri de informaie. Qlementul pentru memorizarea

informaiei este acela!i tranzistor M17 cu gril flotant, numai c pe l;ng aceast gril flotant, acest

tranzistor mai are o gril, care se nume!te gril de !tergere.

*.Arhitectura +i func%ionarea calculatorului

1. Calculatoare electronice. ,o%iuni (enerale

0al#ulatorul ele#troi# este un dispozitiv numeric destinat pentru prelucrarea automat a

informaiei sub diri5area programului introdus de utilizator. 7pre deosebire de dispozitivele precedente, care

au un algoritm fix de funcionare, algoritmul calculatoarelor electronice poate fi scBimbat prin scBimbarea

programului. Qxist dou categorii de calculatoare electronice:

1% Calculatoare analogice n care informaia este reprezentat sub form de un semnal fizic !i se

prelucreaz prin modificarea acestui semnal.

2% Calculatoare numerice sunt implementate din dispozitive numerice# prelucreaz informaia

sub form de coduri binare, folosind algebra logic.

7 D

D

su)strat

- - - - - -

n

- .

:::: ::::

ultra!iolet

1zolator ,iO

2

1. 1. Caracteristicile tehnice ale calculatoarelor

7ipul procesorului indic ce procesor st la baza calculatorului dat.

7ipul cipsetului +cip microcircuit, set" complet-, adic completul de cipuri pe care este realizat

placa de baz

7ipul ar5itecturii +Qxemple: I70, QI70, 8Q70, >:IA-, modul de transmitere a informaiei n

interiorul sistemului

Volumul memoriei "'M +2MD, 4MD, *% MD-

Volumul memoriei intermediare MRSTN +*2J (D, 2$% (D, $*2 (D- determin viteza de lucru

a calculatorului. +memoria MRSTN se cupleaz ntre procesor !i memoria operativ-

8recvena de tact a procesorului

Volumul 5arddiscului 39DD4 sau discul rigid

)umrul :i tipurile unitilor de disc de tip flexibil 38DD4

7ipul tastaturii :i monitorului, manipulatoarele 3mouse + ul4

'lte instalaii terminale a!a ca: imprimanta, scanere, plotere, etc.

2. Arhitectura +i principiile de func%ionare ale calculatorului

2. 1. Arhitectura calculatorului

>rin ;ar<ite#tur= se sub;nelege structura unui dispozitiv la nivel de blocuri funcionale.

>e parcursul dezvoltrii teBnicii calculatoarelor au aprut dou tipuri de arBitectur de calculatoare:

1% 'r5itectura 6nc5is% prezint o arBitectur conform creia unitile calculatorului se conecteaz

dup necesitate +fig.*23-.

)ig'123' #c5ema bloc a calculatorului cu ar5itectur 6nc5is

4ea5unsul este c compatibilitatea ntre blocuri este ncBis.

2% Calculatoare cu ar5itectura desc5is : ideea arBitecturii descBise a calculatorului const n

existena unor canale standarte de transmitere a informaiei !i de cuplare a blocurilor calculatorului la aceste

canale dup necesitate. 0stfel structura este standart !i permite cre!terea ei +adugarea blocurilor noi- fr

scBimbarea configuraiei. Dup acest principiu de arBitectur sunt realizate practic toate calculatoarele

contemporane. Cn calculatorul contemporan +fig.*24- exist trei tipuri de magistrale. 1 magistral conine un

anumit numr de bii.

1 2 3

4 5 6

)ig'124' #c5ema bloc a calculatorului cu ar5itectur desc5is

a% Magistrala de adrese 3M'4 prin ea se transmit adresele celulelor de memorie !i dispozitivelor externe.

Magistrala de adrese este unidirecional, adic adresele se transmit ntr"o singur direcie.

b% Magistrala de date 3MD4 serve!te pentru transmiterea informaiei prelucrate +datelor-. De regul MD

este bidirecional.

#% Magistrala de comand 3MC4 conine semnale standarte de comand ale sistemului.

:oninutul M0, MD, M: au ie!iri la iter!aa "e sistem. @a interfa putem conecta diferite blocuri.

Interfaa este nzestrat cu cuplele pentru extensii.

0uplele petru extesii prezint conectoare destinate pentru cuplarea blocurilor adugtoare.

>lo#ul 1' :ea mai principal unitate a calculatorului este pro#esorul. Ql efectueaz operaii asupra

datelor !i diri5eaz cu procesul de prelucrare a datelor, cu celelalte uniti a calculatorului !i cu dispozitivele

externe. ,oate datele se prelucreaz n procesor, care ndepline!te funcia de diri5are. >rocesorul determin

posibilitile calculatorului: viteza de lucru, capacitatea magistralei de date, volumul memoriei operative,

posibilitile !i tipurile unitilor de intrare ie!ire, tipurile de operaii asupra datelor prin setul de

instruciuni, regimurile de lucru ale calculatorului. Cn procesul funcionrii calculatorului procesorul

ndepline!te urmtoarele operaii:

formeaz adresele de memorie a celulelor#

prime!te instruciunea urmtoare#

decodific instruciunea#

organizeaz ciclul de executare a instruciunii#

efectueaz operaii de citire !i nscriere n memorie#

efectueaz scBimbul de informaii cu dispozitivele externe#

recepioneaz !i trateaz semnalele de ntrerupere !i acces direct la memorie de la dispozitivele

externe.

>rocesorul conine dou module :

'.; 3aritmetical+logical unit4 unitatea aritmetico"logic, care serve!te pentru efectuarea

operaiilor logice, aritmetice.

C; 3command unit4 unitatea de comand, care este destinat pentru producerea semnalelor de

comand.

>lo#ul 2' memoria intern, ce conine /1M +memoria fix- !i /0M +memoria operativ-, n care

se pstreaz datele !i programele utilizatorului. /1M serve!te pentru pstrarea programelor de iniializare !i

testare a calculatorului sub denumirea DI17. Memoria intern este cuplat la M0, MD, M:.

Procesor

A2#

C!# RESET

#nitate

de

memori

eRAM

/7

M

Controlere

p/u disp.

externe

$

1

D

3

O

6

DD PDD

Interfaa

de siste

Cuplu

pentru extensii

monitorDD4DD

tastaturaDis5.

e(terne

M

+

M

D

M

0

&2

b

16

b

20

b

>lo#ul 3' unitatea de intrare"ie!ire +nit IF1- conine dispozitive externe !i controlere pentru

deservirea lor. Destinaia este de a efectua scBimbul de informaie dintre calculator !i utilizator. :ontrolerele

adapteaz dispozitivele externe la formatul semnalelor interne ale calculatorului.

2. 1. /rincipiile de func%ionare ale calculatorului

:alculatorul electric este un dispozitiv programabil. 0lgoritmul de prelucrare a informaiei depinde

de programul utilizatorului. 7cBimbarea programului aduce la scBimbarea funciilor calculatorului.

:alculatorul funcioneaz n mai multe regime.

1% "egimul de executare a comenzilor.

0cesta este un regim de baz. Cnainte de executare programul trebuie s fie plasat n memoria

operativ +/0M- !i reprezentat n limba5ul codurilor ma!in. Instruciunile n procesor sunt cBemate pe rnd

prin MD. Qxecutarea instruciunii are loc n cteva etape.

6aza de decodificare: se determin tipul operaiei, numrul de cicluri. @a fiecare ciclu se produc

semnale de comand pentru ciclul dat. Instruciunea se efectueaz ciclu dup ciclu, n caz de necesitate se

organizeaz operaii de citire sau nscriere ntre memorii !i dispozitivele externe. Cn ultima faz a executrii

instruciunii se alctuie!te adresa instruciunii urmtoare !i procesul se repet din nou.

2% "egimul de oprire se activeaz n cazul cnd n procesor vine o instruciune special +P@,-.

3% "egimul de 6ntrerupere a procesului de calcul apare atunci cnd de la un dispozitiv extern se

prime!te o cerere de ntrerupere +I4,-. acest semnal este analizat de ctre procesor !i dac este permis

ntreruperea, are loc ntreruperea executrii programului de baz !i are loc trecerea la executarea unui alt

program de tratare a ntreruperilor.

4% "egimul de acces direct la memorie apare cnd se efectueaz scBimbul de informaie direct

dintre memorie !i un dispozitiv extern.

. /rocesorul calculatorului

8ro#esorul este unitatea de baz a calculatorului n care se execut instruciunile programului.

>rocesoarele contemporane au ca nucleu un microprocesor !i conin dispozitive suplimentare pentru

asigurarea funcionrii lui. >rocesoarele contemporane au o structur tipic reprezentat n fig.*2$.

#c5ema de structur%

)ig'12*' #c5ema de structur a procesorului

MS

(local0)

RESET

MRD

M!R

I"RD

6"!R

D

I#TA

CP$

#nitatea

central0 a

5rocesorului

I#T

DMA

RESET

0

C%&

Generator

de siste

Controler cu

ma7estrale

Controler de

sistem

MC

0

,emnal de ceas

MD

n

MA

Descrierea funcional a blocurilor :i semnalelor%

Geeratorul "e sistem prezint un generator cu stabilizare cu cuar a frecvenei sau cteva

generatoare care produc semnale de sincronizare pentru toate componentele sistemului. 7emnalul :@( e

destinat unitii centrale a procesorului !i determin viteza efecturii operaiilor asupra datelor. 6recvena

generatorului de sistem depinde de tipul unitii centrale. Cn calculatoarele contemporane generatorul de

sistem mai sincronizeaz unele semnale a!a ca: /Q7Q,, I4,, P1@DA

0?K semnal de ceas de la generatorul care asigur funcionarea :>.

/919@ semnal de iniializare. :nd semnalul este activ, se ntrerupe ndeplinirea oricrui program,

se !terge informaia din registrele interne ale :> !i se porne!te executarea programului DI17.

>rin aceasta se testeaz configuraia sistemului, starea teBnic a componentelor, se iniializeaz ndeplinirea

nucleului sistemului de operare.

6N@ semnal de cerere de ntrerupere. >rocesoarele contemporane au cteva tipuri de ntrerupere:

- simple#

- prioritare#

- de tip Bard#

- de tip soft.

A7?D semnal de cerere de acces direct la memorie. @a procesor el este transmis de la controlerul

de acces direct la memorie, care colecteaz aceste semnale de la dispozitivele externe.

Bitatea #etral a pro#esorului (08B- prezint partea principal a procesorului care asigur

ndeplinirea funciilor sale, operaii asupra datelor !i comand cu procesulo de prelucrare a datelor. Cn :>

se execut instruciunile !i se produc semnalele de comand pentru tot sistemul. 7e deosebesc dou tipuri de

:>:

a% :> pe baz de elemente discrete. 0!a tipuri de :> se ntlnesc n calculatoarele vecBi !i practic nu se

utilizeaz.

b% :> pe baz de microprocesoare.

7pecific pentru microprocesor este c el e executat sub form de unul sau cteva microcircuite integrate, cu

grad mare de integrare. 7unt 3 tipuri de microprocesoare:

- monocip, care sunt realizate ntr"un singur microcircuit#

- secionate, care sunt realizate sub form de o familie de microcircuite cu un grad mare de

integrare

- de tip /I7:, care au un set redus de instruciuni. 7unt foarte simple dup construcie. >e baza lor

se formeaz matricea de microprocesoare.

0otrolerul #u magistralele serve!te pentru desprirea fizic a magistralei de date, magistralei de

adrese !i magistralei de comand. 0cest controler demultiplexeaz magistrala de la intrare n MD !i M0.

1 cale important pentru transferul informaiei ntre :> !i restul sistemului este magistrala "e

sistem (M1%. >rin M7 se transmit adresele, datele !i semnalele de comand. De multe ori semnalele

transmise sunt parial multiplexate, adic se transmit prin acelea!i contacte.

0otrolerul "e sistem folosind informaia transmis prin M7 !i ni!te semnale speciale, produce

semnale de baz a M:. 0cestea sunt:

M/D (memorC rea"% semnal activ care comand cu operaiile de citire din memorie.

M.D ( memorC Drite% operaie de nscriere n memorie.

67/D ( 6E7 rea"% citirea de la un dispozitiv extern.

67.D ( 6E7 Drite% nscrierea la un dispozitv extern.

6N@+ (itrerupt a##ept% acceptarea ntreruperii, semnal de rspuns la cererea de ntrerupere.

A7?D+ (<ol" a##ept% acceptarea accesului direct la memorie, semnal de rspuns la cererea

accesului direct la memorie.

0ceste semnale formeaz baza magistralei de comand.

1.Microprocesoarele monocip

1. ,o%iuni (enerale

Mi#ropro#esorul prezint un dispozitiv care ndepline!te funcia :> !i este executat n form

de un microcircuit integrat sau cteva microcircuite integrate cu un grad nalt de integrare.

Mi#ropro#esoarele moo#ip sunt produse ntr"o singur capsul cu un numr relativ mare de

contacte. Din aceast categorie fac parte a!a microprocesoare ca:

1' microprocesoare de < bii I4,Q@"J<J<# I4,Q@"J<J$# $J<DMJ<0#

2' microprocesoare de = bii I4,Q@"J<J%# I4,Q@"J<*J%# I4,Q@"J<2J%# *J*<DMJ%*J3#

3' microprocesoare de >! bii I4,Q@"J<3J%# I4,Q@"J<4J%# >$# >%# >"pro# 0MD"J<4%.

Microprocesoarele monocip stau la baza tuturor calculatoarelor personale de uz general.

$articularitile M$ monocip%

Microprocesorul monocip este realizat sub form de un singur microcircuit cu un grad mare de

integrare#

Microprocesorul monocip posed o capacitate informaional fix a magistralelor#

Microprocesorul monocip posed un set fix de instruciuni.

2. Arhitectura +i principiul de func%ionare

al microprocesorului monocip 2ntel-3434

Mi#ropro#esorul 6N@9?-8080 este un microprocesor clasic, adic optim. Qste un microprocesor

de J bii !i se produce ntr"o capsul cu 4< terminale. Ql poate efectua prelucrarea datelor cu frecvena

maxim 2,$MPz !i posed o magistral de adres de *% bii, ceea ce permite de a adresa o memorie de %49D.

De asemenea acest microprocesor are un limba5 de programare ce permite de a executa K% de instruciuni.

4ecesit trei surse de alimentare: U$8# U*28# "$8. >ermite tratarea ntreruperilor !i poate lucra n regim de

acces direct la memorie +DM0-. 'r5itectura intern a acestui microprocesor este reprezentat n fig.*2%.

Descrierea funcional a blocurilor%

Cn microprocesor pot fi distinse 2 grupe de blocuri:

6' Modulul de operare. 0ici intr blocurile n care se efectueaz nemi5locit operaii.

66' ?locurile modulului de comand , n care intr blocurile care sunt destinate pentru formarea

semnalelor de comand.

0nalizm mai detaliat aceste dou module.

6' Modulul de operare conine o uitate aritmeti#o-logi# !i registre "e u& geeral. Cn 0@ se

efectueaz operaii aritmetice !i logice obin;ndu"se rezultatul /. 0@ conine registre, sumatoare, elemente

logice, adic el este un dispozitiv combinaional. Cn 0@ se pot efectua operaiile de adunare, scdere, HI,

4, 70, 70 : QV:@DQ/Q, operaii de deplasare bit cu bit. 1peranzii 0 !i D sunt transmi!i respectiv

din registrul temporar !i D din acumulatorul temporar. ,ot transportul de date are loc prin MD intern.

+#umulatorul serve!te pentru pstrarea unui operand nainte de operaie !i pentru fixarea rezultatului dup

operaie.

>lo#ul "e #ore#ie &e#imal serve!te pentru transformarea coninutului acumulatorului din cod binar

n cod binar"zecimal.

De exemplu: *<<*?MKN# <***?MEN. Cn format binar"zecimal avem: W*<<*XW<***X, dar n format regulat binar

obinem: W*<<*<***X ? M*$*N.

)ig'124' 'r5itectura intern a microprocesorului -)71.+<*<*

/egistrul "e !aioae este un registru paralel de J bii n care se pstreaz informaia suplimentar

despre rezultatul operaiei. Microprocesorul I4,Q@"J<J< folose!te numai $ fanioane +fig.*2E-.

)ig'125' 8anioanele utilizate 6n microprocesorul -)71. + <*<*

1' 8anionul @ este fanionul rezultatului zero# dac L?*, atunci s"a obinut rezultatul zero# dac L?<,

atunci rezultatul nu este zero.

. . .

Re7istru

instruc8iunii

Acumulator

Acumulator

tem5orar

Re7istru

tem5orar

Re7istru

.anioane

A%$

Bloc de

corec8ie

zecimal0

9:R3;1,%R3B

CD342!C,!In

crementorDecremento

r

%am5on

de date

%am5on

de date

#nitate de comand0

./ 8>6N 6N@ 6N@9

A7?D

A7?D+

/9+DF

.+6@ G

1

G

2

/919@

:12 2

1FN0

-* 2

,5re toate

/locurile

MD

(iter%

8b

8b

8b

8b

MD

(intern0)

8b

MA

(e(tern0)

14b

+

>

/

:,C4C!

2' 8anionul # fanion de semn# dac 7?*, atunci rezultatul este mai mic ca zero# dac 7?<, atunci

rezultatul este mai mare ca zero.

3' 8anionul de transfer C dac :?*, atunci rezult c n rezultatul operaiei a avut loc transferul din bitul

cel mai superior al acumulatorului. 0cest fanion se mai nume!te de suprancrcare# dac :?<, atunci

transferul nu a avut loc !i deci rezultatul obinut are J bii.

4' 8anionul de paritate $ dac >?*, atunci rezultatul conine un numr par de uniti# dac >?<, atunci

numrul de uniti este impar.

*' 8anionul semitransferului 9C dac P:?*, atunci a avut loc transferul din bitul 4 n bitul $# dac P:

?<, atunci transferul nu a avut loc.

>lo#ul "e registre conine J registre paralele de uz general n care pot fi nscrise datele prelucrate.

/egistrele =, L, D, :, D, Q, P, @ sunt registrele de memorie superoperativ, care permit de a efectua

operaiile de nscriere"citire ntr"un timp foarte scurt. /egistrele = !i L sunt inaccesibile programistic,

deoarece ele sunt utilizate de microprocesor, ns celelalte registre pot fi adresate cu a5utorul instruciunilor.

Qle pot fi folosite n calitate de perecBi de registre, deci obinem trei registre de *% bii +D:, DQ, P@-. Din

acest bloc de registre mai fac parte registrele specializate:

80 H contorul de program +de instruciuni-, care este un registru de *% bii !i serve!te pentru pstrarea

adresei instruciunii curente !i formarea adresei instruciunii urmtoare. 0dresa instruciunii urmtoare poate

fi format pe 2 ci:

a% prin incrementarea adresei precedente#

b% la instruciunile de salt.

18 indicatorul memoriei stiv, care este un registru de *% bii !i conine adresa celulei de v;rf a

memoriei stiv. Memoria stiv este o memorie cu acces serial. Cnscrierea informaiei poate fi fcut numai

printr"o celul +fig. *2J-, iar citirea informaiei decurge invers.

)ig'128' $rincipiul 6nscrierii :i citirii informaiei 6n memoria stiv

6#remetorul H "e#remetorul permite de a incrementa sau decrementa coninutul oricrui

registru.

66' Modulul de comand conine uitatea "e #oma" !i registrul istru#iuii. nitatea

de comand recepioneaz codul instruciunii, l decodific !i organizeaz ciclul instruciunii. :iclul

instruciunii reprezint intervalul de timp n decursul cruia se execut instruciunea. :iclul instruciunii este

mprit n cicluri ma!in !i poate conine p;n la $ cicluri ma!in. 6iecare ciclu ma!in poate avea p;n la $

tacte +vezi fig.*2K-. Cn decursul unui tact se execut o aciune elementar a procesorului.

)ig'12I' Ciclul instruciunii reprezentat sub form de diagrame 6n timp

C B

ABCBAABAA

%

1

%

2

%

&

Ciclu ma<in0 1 Ciclu ma<in0 2

Ciclu instruc8iunii

,=>C

>e parcursul executrii instruciunii, ea produce semnale de comand pentru toate blocurile interne

ale microprocesorului !i pentru celelalte uniti ale calculatorului. Mersul executrii instruciunii poate fi

modificat de semnalele speciale de la dispozitivele externe, a!a ca: /Q7Q,, I4,, P1@D, /Q0DY. Cn

procesul de executare a instruciunii : produce ni!te semnale speciale , care mpreun cu alte semnale

formeaz M:.

./ semnal de nscriere# dac =/?<, atunci are loc nscrierea datelor.

D>6N dac este activ, atunci rezult c MD se afl n stare de recepie a datelor.

6N@ semnal pentru cererea de ntrerupere de la un dispozitiv extern. De obicei acest semnal este

sincronizat de ctre generatorul de sistem.

6N@+ semnal ce indic permisul de ntrerupere dispozitivelor externe.

A7?D semnal recepionat de ctre :>, care reprezint o cerere de acces direct la memorie de la

dispozitivul extern.

A7?D+ semnal ce indic permisul accesului direct la memorie.

.+6@ semnal produs de :> !i indic c microprocesorul se afl n stare de a!teptare.

/9+DF semnal recepionat de unitatea de comand !i indic faptul c datele sunt gata de citire.

G

1

G

2

semnal de ceas produs de generatorul de sistem.

/919@ unicul semnal cu a5utorul cruia poate fi oprit orice program !i este un semnal de

iniializare. :nd semnalul este activ programul se ntrerupe !i se scrie adresa n program, dup care se

nscrie DI17 care testeaz ecBipamentul !i transmite diri5area sistemului de operare.

M>> IJ<J< formeaz ciclul instruciunii din urmtoarele cicluri de ma!in:

1' aducerea instruciei n M>:

2' citirea memoriei

3' nscrierea n memorie

4' citirea memoriei stiv

*' nscrierea n memoria stiv

4' citirea de la dispozitivul extern

5' nscrierea n dispozitivul extern

8' confirmarea ntreruperii

I' confirmarea instruciunii de oprire P0@,

10' confirmarea ntreruperii din starea de oprire P0@,

@a nceputul fiecrui ciclu de ma!in se transmite semnalul activ 7Y4: care este destinat pentru

controlerul de sistem.

8uncionarea microprocesorului%

Dup resetarea procesorului, ncontorul de program se nscrie adresa iniial. >e aceast adres n

/1M se afl instruciunile de trecere necondiionat la nceputul real al programului. :oninutul celulei date

este transmis n M> prin MD !i se fixeaz n registrul instruciunii. Cn procesul executrii instruciunii

coninutul >: se incrimenteaz !i astfel se formeaz adresa instruciunii urmtoare. Dac se ntlne!te o

instruciune de salt,n >: se nscrie adresa saltului. :nd se termin executarea instruciunii date, coninutul

>: este transmis prin M0. 0cest cod a5unge n memorie !i adreseaz urmtoarea celul. 0stfel are loc

nlnuirea procesului. :nd se transmite P0@, ,M> se opre!te,adic trece n regim de repaos. 7coaterea M>

din aceast stare este posibil doar prin aplicarea semnalului /Q7Q, sau I4,.

. /ro(ramarea microprocesorului 2,0#5 3434

Microprocesorul execut nemi5locit instruciunile reprezentate n limba5ul codurilor"ma!in. 0cest

limba5 nu este comod pentru programi!ti. 7e folose!te un limba5 special n care fiecare instruciune din forma

codurilor ma!in este nlocuit printr"o abreviatur. 0cesta este un limba5 de asamblare. 0stfel codul

*<<***<* va fi scris ca: mov :,D.

1% Modelul programistic al M$ conine elementele microprocesorului ce pot fi adresate prin

intermediul instruciunilor.

)ig'130' 1lementele microprocesorului ce pot fi

adresate prin intermediul instruciunilor

:oninutul acumulatorului mpreun cu coninutul registrului fanioanelor prezint cuvntul de stare a

al M>.

0ici mai intr registrele de uz general +D,:,D,Q,P,@- de J bii, cu memorie local. 0ceste registre se

pot utiliza n calitate de perecBi de registre +3 perecBi a cte *% bii- : D":,D"Q,P"@. >:"controlerul de

program care conine adresa instruciunii urmtoare. 7>" indicatorul memoriei stiv care conine adresa

celulei de vrf a memoriei stiv. :u a5utorul 7> se localizeaz memoria stiv n diferite locuri a memoriei

operative.

2% 1lemente ale programului 6n limba(ul de asamblare.

!.a. 8ormatul instruciunii modul de reprezentare a instruciunii n cadrul programului.

)ig' 131' Modul de reprezentare a instruciunii 6n cadrul programului

+"resa adresa instruciunii date n memorie#

A-#o" codul reprezentat n format Bexazecimal#

9ti#<eta conine o abreviatur pentru a marca unele instruciuni#

6stru#iuea este ns!i instruciunea n limba5ul de asamblare#

0ometarii conine o lmurire despre instruciunea dat.

!.b. $seudoinstruciunea prezint o instruciune fals care nu exist n setul de instruciuni. Qa nu este

executat de M>. :onine informaie suplimentar despre anumite momente a prgramului.

!.c. Macroinstruciunea este o instruciune inexistent care nlocuie!te un sector de program care se repet

de mai multe ori n programul dat. Macroinstruciunea trebuie nscris n formatul instruciunii !i nu aduce la

economie de memorie.

!.d. #ubrutina prezint un program sinestttor care se utilizeaz de mai multe ori n cadrul unui alt

program de baz. 0ceea!i operaie M se nscrie ca subrutin cu numele M

*

. @a executarea programului, cnd

se a5unge la subrutina M

*

, executarea programului se ntrerupe !i se execut un salt la acel loc unde se afl

subrutina dat. Dup terminarea executrii subrutinei,programul de baz se execut mai departe. 0stfel are

loc economisirea spaiului n memorie.

3% #etul de instruciuni al M$ -)71. <*<*.

@imba5ul de asamblare alM> IJ<J< conine cteva grupe de instruciuni:

Instruciuni pentru transfer de date#

Instruciuni pentru operaii aritmetice !i logice#

9:BCD34

2!C,!

Acumulator

R-ru .anioane

PS!

memoria !orturi 1?O

Memoria

sti@0

AdresaCod a'in(Etic)etaInstruciuneaCoentarii A00B

-16

-M1

-M$1 DC0'

-0C'DD

(M1 - nce5utul ciclului)

Instruciuni pentru salturi !i lucrul cu subrutina#

Instruciuni pentru lucrul cu memoria stiv#

Instruciuni cu funcii speciale.

3'1' -nstruciunile pentru transfer de date se mpart n cteva subgrupe:

a% Instruciune de transfer de tip Mregistru"registruN.

Qx: M18 0,D .

0ceast instruciune face transferul de date din registrul D n registrul0 +acumulatorul-. M18 0,M"

coninutul celulei de memorie cu adresa din perecBea de reegistre P,@ se transmite n acumulator +0-.

b% Instruciune de tipul: M8I 0,b.te. +D.te- este nscris n acumulator +b.te0-.

Qx: M8I 0,2< cifra 2< este nscris n acumulator.

#% Instruciune de ncrcare a perecBilor de registre: @VI D,2 b.tes.

Qx: @VI D,2<3< ncarc perecBea de registre D: cu codul 2<3< +2<3<D:-.

@VI 7>, 2<3< nscrierea n memoria stiv.

"% @D0, adr aceast instruciune nscrie n acumulator celule cu adresa indicat +M+adr-0-. adr

conine 4 simboluri.

7,0, adr stocBeaz coninutul acumulatorului n celula de memorie cu adresa indicat

+0M+adr--.

@D0V D coninutul celulei de memorie cu adresa ce se afl n perecBea de registre D: este nscris

n acumulator +M+D:-0-.

7,0V D coninutul acumulatorului este nscris n memorie pe adresa ce se afl n perecBea de

registre D: +0M+D:--.

@P@D adr coninutul celulei de memorie cu adresa dat este nscris n registrul @, iar coninutul

celulei de memorie cu o unitate mai mare +adr+*- se nscrie n registrul P.

7P@D adr coninutul registrului @ este transmis n memorie n celula cu adresa indicat, iar

coninutul registrului P este nscris n memorie n celula cu adresa incrementat.

3'2' -nstruciuni pentru operaii aritmetice :i logice.

a% Instruciuni pentru adunarea simpl:

0DD D instruciunea adun coninutul acumulatorului !i registrului D !i nscrie rezultatul n

acumulator.

b% 0dunarea cu transfer:

0D: D coninutul acumulatorului se adun cu coninutul registrului indicat !i cu fanionul de

transfer !i se nscrie n acumulator +0UDU:0-.

#% 7cderea simpl:

7D D din coninutul acumulatorului se scade coninutul registrului indicat !i rezultatul este nscris

n acumulator +0D0-.

"% 7cderea cu mprumut:

7DD D" din coninutul acumulatorului se scade coninutul registrului indicat !i coninutul fanionului

de transfer,rezultatul se nscrie n acumulator +0D:0-.

e% Incrementarea registrului:

I4/ : coninutul registrului indicat se adun cu o unitate !i se nscrie iar!i n registru +:U*:-.

3'3' -nstruciuni pentru salturi :i lucrul cu subrutina

a% Instruciuni de salt necondiionat.

ZM> adr instruciune de salt necondiionat. 0dresa este nscris n contorul de program. rmtoarea

instruciune dup instruciunea dat va ndeplini instruciunea cu adresa indicat.

b% Instruciunile de salt condiionat:

b.. instruciunile Z4L, ZL analizeaz fanionul rezultatului zero:

Z4L adr saltul se va efectua dac se ndepline!te condiia coninut n instruciune, adic dac rezultatul

nu este zero.

ZL adr saltul se efectueaz dac rezultatul este zero.

b.!. instruciunile Z4:, Z: utilizeaz fanionul transferului:

Z4: adr saltul se va efectua dac fanionul transferului :?*.

Z: adr " saltul se va efectua dac fanionul transferului :?<.

b.>. instruciunile Z>1, Z>Q utilizeaz fanionul paritii:

Z>1 adr " saltul se va efectua dac fanionul paritii >?<.

Z>Q adr " saltul se va efectua dac fanionul paritii >?*.

b.A. instruciunile Z>, ZM utilizeaz fanionul semnului:

Z> adr +5umping plus-, saltul se va efectua dac fanionul semnului 7?<, adic rezultatul este pozitiv.

ZM adr +5umping minus-, saltul se va efectua dac fanionul semnului 7?*, adic rezultatul este negativ.

>:P@ adr efectueaz scBimbul reciproc de date ntre contorul de program !i perecBea de registre P@.

#% Instruciuni pentru cBemarea subrutinei:

:0@@ adr cBemarea necondiionat a subrutinei. 0dresa adr este adresa de nceput a subrutinei +vezi

fig.*32-.

)ig'132' $rincipiul funcionrii subrutinei

:elelalte instruciuni sunt condiionate !i se analizeaz condiiile respective din instruciune. Dac

condiia dat se ndepline!te, atunci se trece la subrutin, iar dac nu, aceast instruciune se ignor.

"% Instruciuni de ntoarcere:

/Q, +return- reprezint o ntoarcere necondiionat !i este ultima din subrutin.

1 subrutin poate fi folosit de cte ori avem nevoie +fig.*33-. 7ubrutinele pot fi incluse una n alta.

)ig'133' $rincipiul folosirii subrutinei de c6teva ori

3'4. -nstruciuni de comand%

DI interzice ntreruperile.

QI permite ntreruperile.

41> este o instruciune goal, adic nu execut nici o instruciune. 7e folose!te pentru a ocupa unele

locuri n program.

P@, instruciune de oprire a programului.

3'*' -ncrementarea perec5ilor de registre:

I4V D coninutul registrelor DQ se mre!te cu * !i rezultatul se nscrie n DQ.

Decrementarea registrului:

D:/ D :oninutul registrului D se mic!oreaz cu *, cu nscrierea rezultatului n D.

Decrementarea perecBii de registre:

D:V D +D:-"*, iar rezultatul rm;ne n D:.

nitatea se scade sau se adun la codul inferior al registrului inferior.

D0D D adunarea dubl. :oninutul +P@- U +DQ- se nscrie n +P@-.

Instruciuni logice:

CA22

adrCA22

adr

R3,3%

$rogramul

principal

?aza

subrutinei

$rogramul

principal

,u/rutine

040 Q conform acestei instruciuni are loc operaia HI dintre coninutul acumulatorului !i registrul Q,

iar rezultatul se nscrie n acumulator.

1/0 Q operaia 70 dintre coninutul acumulatorului !i registrul Q, iar rezultatul se nscrie n

acumulator.

V/0 : operaia 70 cu QV:@DQ/Q dintre coninutul acumulatorului !i registrul :, iar rezultatul se

nscrie n acumulator.

:M> D din coninutul acumulatorului se scade coninutul registrului indicat +D-, iar rezultatul nu se

nscrie nicieri, ns dac +D-[+0-, atunci fanionul 7?*# dac +D-?+0-, atunci fanionul L?*# dac +D-\+0-nu

se nt;mpl nimic.

3'4' -nstruciuni pentru operaii aritmetice i logice cu numere nemi(locite%

0DI bait +0-U+baitul indicat- se nscrie n +0-.

0:I bait adunare cu mprumut.

3'5' -nstruciuni de rotaie 3de deplasare4%

/@: rotaie ciclic la st;nga +fig.*34 a-.

//: rotaie ciclic la dreapta +fig.*34 b-.

/0@ rotaie aritmetic spre st;nga +fig.*34 c-.

/0/ rotaie aritmetic spre dreapta +fig.*34 d-.

)ig'134' $rincipiul funcionrii instruciunii de rotaie

3'8' -nstruciuni speciale%

D00 transfer coninutul +0- din sistemul binar n sistemul binar zecimal.

:M0 negarea bit cu bit a coninutului acumulatorului.

7,: negarea fanionului de transfer :.

3'I' -nstruciuni pentru lucru cu porturile%

O60 )ait instruciune de transmitere a informaiei din acumulator n portul cu adresa dat.

I4 bait instruciune de citire din portul de intrare.

3'10' -nstruciuni pentru lucrul cu memoria stiv%

>7P D instruciune de nscriere n memoria stiv a coninutului perecBii de registre +D:-.

&. 6nitatea de comand" a M/

Bitatea "e #oma" (0B% prezint cea mai important parte a M> care asigur ndeplinirea

funciilor de comand. : prime!te codul operaiei !i pe baza lui produce toate semnalele de comand

necesare. Dup principiul de funcionare exist dou tipuri de uniti de comand:

1% nitate de comand cu logic cablat +fix-, adic logica cu configuraia ce nu poate fi scBimbat.

0ceste : se utilizeaz n microprocesoarele monocip de tipul IJ<J<.

2% nitate de comand cu microprogramare. 7e folosesc n microprocesoarele secionate.

C A

2

A E A

0

8anion de

transfer

C D

C A

2

A E A

0

C A

2

A E A

0

&.1. C6 cu lo(ic" ca)lat"

'r5itectura tipic a acestei :> este artat n fig.*3$.

)ig'13*' 'r5itectura tipic a C; cu logic cablat.

0B se nume!te #u logi# #ablat deoarece semnalele de comand sunt codificate ntr"un circuit

combinaional o scBem logic cu sectoare unde sunt codificate operaiile sau tactele.

M> formeaz codul de J bii al operaiei ce se fixeaz n /G :1>, la ie!irea cruia este cuplat D: care

decodific acest cod, transform acest cod ntr"un cod unitar, care poate avea maxim 2$% ie!iri" 2$% operaii.

De la circuitul combinaional, spre :,2 pleac un numr de tacte care sunt necesare pentru ndeplinirea

instruciunii date. 0cest numr se nscrie n D: de tacte !i dup f

G

" tacte codul se mic!oreaz cu o unitate.

,actele sunt decodificate !i pleac la circuitul combinaional. 6iecare poriune a circuitului combinaional

efectueaz o anumit operaie !i fiecare poriune este organizat dup c;teva tacte. 6iecare ie!ire a D:

tacte coordoneaz cu tactul respectiv din poriune. Cn procesul de lucru pot aciona semnalele fanioanelor,

instruciunilor de salt condiionat etc. Cn dependen de aceste semnale la ie!irea circuitului combinaional

vom avea diferite semnale de comand.

'vanta(ele%

8iteza mai mare de lucru +n comparaie cu : cu microprogramare-#

7etul de instruciuni este cunoscut !i nu este necesar de a elabora. 0ceasta permite de a utiliza

programele standarde existente.

)ea(unsurile%

are o structur rigid, complicat#

nu poate fi reprogramat.

&.2. C6 cu micropro(ramare

Qsena diri5rii prin microprogramare const n faptul c semnalele de comand care trebuie s fie

produse sunt nscrise ntr"o memorie fix. Cn procesul ndeplinirii instruciunii aceste semnale sunt citite ntr"

o ordine anumit, determinat de algoritmul executrii instuciunii date +curente-. >entru a nlnui

microinstruciunile fiecare celul a memoriei /1M conine nafar de semnalele de comand !i adresa

microinstruciunii urmtoare, care se utilizeaz n urmtorul tact. Datorit acestui fapt, unitile de comand

cu microprogramare au o structur regulat !i sunt universale.

t

1

t

2

.

.

.

.

.

.

RG

C1

Codul

1nstruc8iunii

C1

DC

o5era8ional

CT

tacte

DC

tacte

Circuit

co*inaional

ADD

ADC

MO$

.

.

.

,1>C

t

ultimul

t

1

t

2

... t

ultimul

,emnale

de

comand0

anioane <i semnale

s5eciale

>r. De tacte

0lt consecin este c aceste uniti de comand permit scBimbarea setului de instruciuni prin

!tergerea memoriei /1M !i nscrierea altor semnale de comand. 0ceasta este prioritatea principal a unitii

de comand cu microprogramare.

'r5itectura tipic a : cu microprogramare este reprezentat n fig.*3%.

)ig' 134' 'r5itectura tipic a C; cu microprogramare

$rincipiul funcionrii%

0vem un multiplexor cu 2 intrri. @a prima intrare vine codul instruciunii, iar la a doua intrare vine

adresa microinstruciunii urmtoare, care se transmite la /G de adrese a MI. :odul instruciunii reprezint un

cod binar, ce codific instruciunea dat. Multiplexorul permite de a transmite registrului ori codul

instruciunii, c;nd se ncepe executarea ei, ori adresa microinstruciunii urmtoare, n procesul executrii

instruciunii date. /egistrul de adrese fixeaz adresa microinstruciunii pe timpul executrii ei. Cnscrierea are

loc cu fiecare impuls de sincronizare.

/7M1 conine semnalele de comand.

/7M2 conine adresele microinstruciunilor.

/7M1 !i /7M2 sunt adresate concomitent cu acela!i cod de adres.

@murirea funcionrii acestei uniti poate fi analizat n fig.*3E.

)ig' 135' 1xplicaia funcionrii C; cu microprogramare

nde: numrul de bii a memoriei /1M*#

m numrul de bii a memoriei /1M2.

Cn acest volum, pentru fiecare instruciune sunt repartizate domeniile I

*,

I

2

.

'vanta(ele%

setul de instruciuni poate fi scBimbat prin renscrierea memoriilor /1M* !i /1M2.

)ea(unsurile%

viteza mai mic de lucru dect la : cu logic cablat#

necesitatea elaborrii setului de instruciuni pentru fiecare utilizare a procesorului#

imposibilitatea utilizrii programelor existente.

RG

de a drese a

microinstruc-

8iunii

adr.

Codul

instruc8iunii

M$+

R"M

semnale a

microinstruc-

8iunii

R"M

semnale a

microinstruc-

8iunii

Adresa MI urm0toare

.anioane

,emnal de

ceas

.

.

.

+

1

+

n

Semnale

MI

R"M ,123CIMIR"M 2

-

-

!

-

>

. . .

m

n

m

"

n

n

u

m

e

r

e

*. 6nitatea aritmetico-lo(ic" a microprocesorului (A56)

+?B reprezint blocul principal n care se efectueaz operaii aritmetice !i logice asupra datelor.

7tructura tipic a 0@ este dictat de tipul de operaii pe care ea trebuie s le execute. 1 structur posibil a

unei 0@ poate fi urmtoarea +vezi fig.*3J-.

'r5itectura tipic%

)ig' 138' 'r5itectura tipic a '.;

6iecare bloc este diri5at de semnalele produse de unitatea de comand +:-. :uv;ntul de date se

nscrie n /G* sau n /G2. Din 0 +/G*- se transmit la blocul de operaii logice + dac e nevoie de acestea-

dac nu, datele se transmit n blocul de deplasare. De la ie!ire rezultatul se scrie n acumulator. Dac, de

exemplu, avem de adunat 2 numere, numerele se nscriu unul n /G* !i altul n /G2 se transmit mai departe

!i este efectuat operaia respectiv, apoi rezultatul primit se nscrie n acumulator.

7.Microprocesoare sec%ionate

1. /articularit"%ile microprocesoarelor sec%ionate

Microprocesoarele monocip au urmtoarele nea5unsuri:

capacitatea fix a magistralelor de date !i adres#

setul fix de instruciuni#

este imposibil de utilizat numai unele blocuri ale microprocesorului.

0ceste nea5unsuri sunt licBidate n mi#ropro#esoarele se#ioate, care au urmtoarele particulariti:

Magistrala de date !i cea de adres nu au o capacitate fix din cauza c microprocesorul e compus

din secii elementare, care pot lucra paralel, astfel se formeaz o magistral de date cu capacitatea necesar

+ $JK secii, 2 bii, *J<4 secii, 4 bii#

Microprocesorul e format din moduluri cu funcii specializate:

modulul de comand#

modulul de operare.

-loc de

deplasare01

.

.

.

.

.

.

.

.

nn"1

RG,

acumula-

tor

RG2

-loc

co*inaional

lo.ic

1

.

.

.

.

nSM

A

B1

.

R

3

:

#

2

%

A

%

.

n1

.

.

.

n:1

>

n /i8i

o5erandul

A

n /i8i

o5erandul

B

,emnale de

comand0

Bloc de .ormare a .anioanelor

Rezultatul .inal

n

Modulurile sunt realizate pe microcircuite !i pot fi utilizate de aparte. Deci microprocesorul prezint un

ansamblu, un set de microcircuite, care pot fi interconectate fr mi5loace adugtoare.

Microprocesoarele secionate conin unitatea de comand cu microprogramare#

7etul de instruciuni nu este fix, el se elaboreaz pentru fiecare aplicare practic a

microprocesorului reie!ind din domeniul utilizrii.

)ea(unsurile%

4umrul mare de microcircuite necesar pentru formarea configuraiei unui microprocesor#

@ipsa iniial a setului de instruciuni. Qlaborarea setului de instruciuni este un lucru destul de

complicat.

2. Arhitectura +i principiul de func%ionare a M/ sec%ionat

7cBema ce ilustreaz arBitectura M> este reprezentat n fig.*3K.

)ig' 13I' 'r5itectura tipic a M$ secionat

M78 microoperaii

17 secii de operare

0vem 2 moduluri desprite. 6iecare modul este alctuit din mai multe microcircuite. Modulul de

operare este alctuit din secii de operare. 7eciile sunt conectate ntre ele. >rin MD2 se transmit instruciuni

care trebuiesc realizate. 1peranzii au numrul de bii nxm. Cn procesul executrii instruciunea se mparte n

mai multe tacte. Din /1M se transmite permanent MI pentru executarea instruciunii. /ezultatele sunt

strnse de MD*. 6anioanele sunt transmise la modulul de comand.

. Microprocesorul sec%ionat 134&

Mi#ropro#esorul se#ioat 1804 e destinat realizrii sistemelor specializate de comandm !i de

calcul. >rezint un set de microcircuite, circa *% tipuri pe care se poate implimenta un microprocesor de

configuraie diferit, n dependen de domeniul de utilizare. :apacitatea magistralei de date a unei secii de

operare elementare este de 4 bii. >oate funciona la o frecven de tact de *2 MPz. Microprocesorul este

alctuit din modulul de operare !i modulul de comand +microprogramare-.

Modulul de operare poate fi realizat pe 2 secii:

*J<4 DF:* secie de operare simpl#

*J<4DF:2 secie de operare mai perfecionat.

/ / /

,emnale

ale

microo5e-

ra8iilor

R"M

,emnale

ale

microo5e-

ra8iunii

Bloc de

.ormare a

MI

m

F

instruc8iunea

S",

,ec8ia de

o5erare

adresa

. . .

,emnale de

comand0

S"2 S"e

. . .

MA e

G/

n n n

. . .

Modulul de o5erare

.anioane

e

Gn

Modulul de o5erare

Date /MD0

Modulul de comand folose!te urmtoarele microcircuite:

*J<4 D'] bloc pentru determinarea modului de formare a adresei microinstruciuniiurmtoare#

*J<4 D'* bloc de formare a adresei MI urmtoare#

*J<4 ^&* registru specializat#

1e#ia "e operare 1804 >01

7cBema ce ilustreaz arBitectura acestei secii este reprezentat n figura *4<.

)ig' 140' 'r5itectura seciei de operare <*A ?C

0vem un bloc de deplasare, bloc de registre de uz general +*% registre-# 2 registre intermediare# un

selector de date, la interconectarea cruia poate s vin datele canalului a, b, c constant, iar la ie!irea lui

primim 2 grupe de date# unitatea aritmetico" logic +0@-# un selector de date de ie!ire. Datele din 0@ vin

n selector. @a ie!ire avem MD de ie!ire de 4 bii. Dloc special, numit _ are funcia de"a efectua operaii de

nmulire. 7cBema mai conine un bloc de deplasare ce serve!te pentru efectuarea operaiilor de deplasare n

st;nga sau dreapta. :analele :*, :2, :3, :4 sunt destinate pentru interaciunea cu seciile vecine la

operaiile de deplasare. 7elector de date " permite de a transmite n 0@ datele n diferite combinaii, !i

anume: la ie!ire selectorul are 2 canale a c;te 4 bii . @a ie!irea selectorului se obin numai 2 operanzi. Dac

datele nu trebuie transmise, atunci ele se nscriu n /G le din blocul de deplasare. 7elector de date de ie!ire

permite de a transmite la MD extern, sau rezultatul operaiei, sau coninutul unuia din /G"le de uz

general. :u fiecare din aceste blocuri diri5eaz semnalele microinstruciunilor. >entru aceast secie acestea

sunt n numr de 24 semnale.

Mo"ulul "e #oma" #u mi#roprogramare'

7erve!te pentru generarea semnalelor de comand pentru modulul de operare analizat mai

sus !i pentru celelalte blocuri ale sistemului. 7tructura modulului de comand a acestui microprocesor e

reprezentat n fig. *4*.

4

4

4

4

4

Bloc de

de5la-

sare

RG

121

RG

de uz

7eneral

16'

RG

A

RG

B

,elector

de date

A

B

A%$

,elector

de date

de ie<ire

C

'

C

&

4 4

4

O<O

n

0

*

0

2

f

a

n

i

o

a

n

e

C

2

C

1

Bloc de

de5la-

sare

1ntrare HIH

=

Date

de

ie<ire

4

Date nemiJlocite

n

0

n

D

)ig' 141' #tructura modulului de comand

0dresa MI urmtoare poate fi format:

prin incrimentare#

prin decrementare#

citit din MI precedent#

adresa de salt#

poate fi calculat prin adugarea unei constante.

8rogramarea mi#ropro#esoarelor se#ioate'

Deoarece M> secionate au o unitate de comand cu microprogramare, n mod iniial ele nu au limba5

de programare, nu au set de instruciuni. De aceia la etapa alctuirii programelor n prealabil trebuie de

efectuat microprogramarea lor " alctuirea setului de instruciuni. 1rice instruciune const din mai multe

microinstruciuni +MI-, se formeaz un microprogram +Micro>rog-. microinstruciuinea prezint un cod binar

ce conine semnalele de comand pentru toate blocurile modului de operare, modulului de comand !i

dispozitive externe.

Dup alctuire, Micro>rogramele se nscriu n memoria fix a modului de comand. Dup aceasta,

M> secionat devine analog cu M> monocip. 0ceste seturi de instruciuni seutilizeaz la alctuirea

programelor la fel ca !i n cazul M> lor monocip. 7cBimbarea setului de instruciuni aduce la 2 nea5unsuri :

cre!terea preului produselor programistice#

incompatibilitatea producerii programelor la diferii utilizatori ale aceluia!i microprocesor.

&. Microprocesoarele monocip a!ansate

1% M$ de < bii se utilizeaz mai ales n controlere, calculatoare, calculatoare personale !.a.m.d.

1 modificare a IJ<J< este M> IJ<J$.

a% M$ -<*<B

frecvena de tact 3 MPz

M> de J bii

poate adresa direct %4 9b M, 2$% port.

#c5ema funcional este prezentat n fig. *42.

R"M

1nstruc8iunii

-K& LM''

RG

s5ecializat

1A0' NL1K

Bloc de

.ormare a

adresei

1A0' OP1'

Bloc de

determinare

a modulului

.orm. adresei

1A0' OP&

1& ' '

'

.

a

n

i

o

a

n

e

,5re modulul

de o5erare

2A 2' &2 2A

'

Adresa

micro-

instruc8iunii

Codul

instruc8iunii

)ig' 142' #c5ema funcional a M$ -<*<B

+ adresa#

D date#

@/+8 ntrerupere fr mascare tip P0/D#

/1@ ntreruperi cu mascare, prelucrare dup vector#

16D port serie de intrare

17D port serie de ie!ire

+?9 demultiplexeaz magistrala de date !i de adres.

0cest M> produce singur semnalele pentru controlere. 0cest M> e compatibil cu cele din grupa $J<.

,ensiune de alimentare $8.

b% M$ @<* +firma Lilod-

Qste un M> compatibil cu IJ<J< !i dup Bard !i dup soft. :onine un sistem mai simplificat de

semnale de comand, este reprezentat n fig. *43.

A

MA

A

,

e

m

n

a

l

e

5

r

o

d

u

s

e

5

e

n

t

r

u

c

o

n

t

r

o

l

e

r

e

!

o

r

t

u

r

i

C

C

!

"1#17

"1'DDI3435'

B

E

'

<

'

F

E

'

<

D

F

E

D

<

'.17"'$

"#7

"#7!

"#7>

,"

-)7'16D

#2D"1#17

C.C

8i(. 1&. #c5ema funcional a M$ @<*

7emnal de ceas cu frecvena : LJ<0 : 6 ? J MPz

LJ<D : 6 ? % MPz

0rBitectura intern a LJ< se deosebe!te de a IJ<J< prin blocuri de registre. Dlocul de registre a LJ<

are nfi!area din fig.*44.

)ig' 144' ?locul de registre a M$ @<*

2% Microprocesoarele de = bii.

>rimul M> de *% bii a fost produs de firma I4,Q@ n *KEJ IJ<J%.

magistrala de date a fost mrit de 2 ori: MD ? *% bii

magistrala de adres M0 ? 2< bii

volumul memoriei ? *Mb

viteza de calcul ? 33<mii operaii Fsec

frecvena de tact 6 ? 4 JMPz

Cn *KEK se lanseaz M> IJ<JJ. 0re o magistral extern de date de J bii +n rest e acela!i cu IJ<J%-.

0pare primul calculator personal IDM >:FV,. 0vanta5ele M> IJ<J%FJJ:

cteva regimuri de lucru !i anume regimul minimal pentru sisteme simple

16

MA

A

8

-)7

)M-

"1#17634E'

B

0'

*

ED

F

0D

*

9'.7

MD

o5rire

adresare la memorie

adresare la 5orturi

Rem5ros50tarea a

memoriei dinamice

nscriere

citire

semnal de ceas

Qntreru5ere

cu mascare

Qntreru5ere

.0r0 mascare

A

,

ARRBCBRCRD3DR3R424R2R$ector de

ntreru5ereR; de re7enerare memorie/G

de regenerare memorieiR; de

indecsareContor de 5ro7ram1ndicatorul

mem.sti@eR9 de

indecsareR9 de

indecsareContor de 5ro7ramContor

de 5ro7ram1ndicatorul mem.sti@e1ndicatorul

mem.sti@e

regimul maximal pentru sisteme complicate

un set lrgit de instruciuni +fa de IJ<J<- au n componen instruciunea de nmulire a 2 numere

mai multe regimuri de adresare a datelor

segmentarea memoriei +dimensiunea maxim a segmentului este de %4 (b-. 7egmentarea a fost introdus

pentru a asigura compatibilitatea cu programele elaborate pentru M> IJ<J<.

'r5itectura M$ -<*<=%

0ici au fost introduse unele modificri !i deci este mai complicat +vezi fig.*4$-.

)ig' 14*' 'r5itectura M$ -<*<=

Descrierea blocurilor funcionale%

9B i >6B 2 blocuri principale

9B H modul de operare

>6B blocul de interfa a magistralelor

+?B asigur ndeplinirea tuturor instruciunilor !i instruciunilor de nmulire a 2 numere.

/egistru "e !aioae conine K fanioane.

68080 asigur comanda cu tot sistemul, execut;nd instruciuni c;te * bait.

/egistru "e u& geeral memorie local n M> !i are aspectul din fig. *4%.

)ig' 144' #tructura registrului de uz general

0vem 4 registre c;te *% bii.

A partea superioar

? partea inferioar.

0cest bloc poate fi folosit ca registre de J bii.

/egistru "e a"rese ndepline!te rolul controlului de program !i indicatorul memoriei stive. /egistru

de adrese are structura din fig. *4E.

. . .

. . .

,emnale de

comand0

,emnale

5entru sistem

MD intern0 ,7

A

A

A

20

<

16

16

%

16

%

-I$

E$

'

1

%

A1B A16

AD1- AD0

Codul

instruc8iunii

RG8e

de uz

7eneral

A%$

RG8e

de

adres0

RG8e

.anioane

C$

RG

instruc8i-

unii

SM

RG

de

se7mente

Rnd de

instruc-

8iuni

Inerfaa pentru

a.estral(

Bi8ii su5eriori

multi5le(a8i

Bi8ii in.eriori

multi5le(a8i

1- AK

0A4A2B4B2C4C2D4D2

)ig' 145' #tructura registrului de adrese

0vem $ registre de *% bii. Cn aceste registre se pstreaz adresa informaiei

n interiorul segmentului.

18 indic memoria stiv#

>8 indicatorul bazei +Daza codul care se folose!te la calcularea adresei instruciunii urmtoare-#

16 indexarea sursei#

D6 indexarea destinatarului#

I>+>:- controlul de program.

/egistru "e segmete + vezi fig.*4J - e asemntor cu registru de adrese, numai c n el se

conine adresa segmentului. 0vem 4 registre a c;te *% bii.

)ig' 148' #tructura registrului de segmente

01 segmentul codului instruciunii#

11 segmentul pentru memoria stiv#

D1 segmentul de date#

81 segment suplimentar.

0dresele logice care se folosesc n program se conin n registru de adrese de *% bii. :u a5utorul

registrului de segmente se formeaz adresa fizic de 2< bii prin adunare cu deplasare.

>rezena r;ndului de instruciuni care acioneaz ca o memorie casBe+memorie intermediar de vitez

mare-. tilizarea r;ndului de instruciuni +memoria casBe-, permite de a mri considerabil viteza de calcul

fr a mri frecvena de tact a M>, datorit excluderii timpului de a!teptare a instruciunii curente.

1-

0,!B!,1D11! (!,)

1-

0C,,,D,!,

S-ar putea să vă placă și

- Referat CalculatorDocument18 paginiReferat CalculatorStela Doinita Macovei100% (2)

- Curs Administrator ReteaDocument31 paginiCurs Administrator Retealiviuturcu75% (4)

- Sistemul de CalculDocument14 paginiSistemul de CalculIoana David AndreiÎncă nu există evaluări

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- Cifruri Bloc ExercitiiDocument28 paginiCifruri Bloc Exercitiicristina_anÎncă nu există evaluări

- PMDDocument34 paginiPMDPasan PetruÎncă nu există evaluări

- Sisteme Cu Microprocesoare ExempleDocument91 paginiSisteme Cu Microprocesoare ExempleBuzoianu StefanÎncă nu există evaluări

- SISTEM DE MONITORIZARE A TEMPERATURII - Florea Leonardo StefanDocument13 paginiSISTEM DE MONITORIZARE A TEMPERATURII - Florea Leonardo StefanLeonardo Florea50% (2)

- Comunicare de Tip USARTDocument12 paginiComunicare de Tip USARTMorosan DimitrieÎncă nu există evaluări

- Arhitectura Microprocesoarelor Burileanu Curs 2015-1-1Document78 paginiArhitectura Microprocesoarelor Burileanu Curs 2015-1-1Vlad NiculceaÎncă nu există evaluări

- Teorie PMDDocument44 paginiTeorie PMDNico100% (3)

- Curs 4Document37 paginiCurs 4Pasan PetruÎncă nu există evaluări

- Arhitectura Calculatoarelor C - 10-11Document15 paginiArhitectura Calculatoarelor C - 10-11Popa DaniÎncă nu există evaluări

- Adresare TCP/IPDocument9 paginiAdresare TCP/IPc_otescuÎncă nu există evaluări

- Luc4 UpDocument11 paginiLuc4 UpSmiley AndreiÎncă nu există evaluări

- Asembler, GeneralitatiDocument14 paginiAsembler, GeneralitatiMihai MoiseanuÎncă nu există evaluări

- Clasificarea Si Caracteristicile Unei Memorii, MEMORII ROM Si RAMDocument7 paginiClasificarea Si Caracteristicile Unei Memorii, MEMORII ROM Si RAMdragosvl0% (1)

- Panou PublicitarDocument11 paginiPanou PublicitarKasGikesÎncă nu există evaluări

- Calculatorul Este o Maşină Care Prelucrează Informaţiile AutomatDocument3 paginiCalculatorul Este o Maşină Care Prelucrează Informaţiile AutomatIuliana PrisecaruÎncă nu există evaluări

- Microelectronic ADocument8 paginiMicroelectronic Aiani_teodoraÎncă nu există evaluări

- Toate-Grilele RC 240121 112544Document92 paginiToate-Grilele RC 240121 112544luiza.busuioc.6Încă nu există evaluări

- Laborator3 MIPSDocument12 paginiLaborator3 MIPSMitzy MtzÎncă nu există evaluări

- Rolul Si Functiile Sistemelor de CalculDocument6 paginiRolul Si Functiile Sistemelor de CalculStefania StoicaÎncă nu există evaluări

- Completare Curs Circuite LogiceDocument8 paginiCompletare Curs Circuite LogiceAlin SârbuÎncă nu există evaluări

- Coprocesorul Matematic (Arhitectura CalculatoarelorDocument19 paginiCoprocesorul Matematic (Arhitectura CalculatoarelorCatalin CataÎncă nu există evaluări

- CURS8Document2 paginiCURS8Mihai PetriucÎncă nu există evaluări

- Arduino - EepromDocument10 paginiArduino - EeprombeinurÎncă nu există evaluări

- Magistrala SPIDocument10 paginiMagistrala SPIone_blanche6175Încă nu există evaluări

- Arhitectura Sistemelor de CalculDocument8 paginiArhitectura Sistemelor de CalculDru BarrettÎncă nu există evaluări

- 0 Lab 05Document27 pagini0 Lab 05Sorin ZubereÎncă nu există evaluări

- Proiectarea Cu MicroprocesoareDocument31 paginiProiectarea Cu MicroprocesoareAlexandru MihaiuÎncă nu există evaluări

- C7 MemoriiDocument22 paginiC7 MemoriiCristi SzaboÎncă nu există evaluări

- Proiect CSC Tema1 Lupu VargaDocument21 paginiProiect CSC Tema1 Lupu VargaMitru Carmen100% (1)

- ATESTATDocument36 paginiATESTATMarius OrânceanuÎncă nu există evaluări

- Proiectarea Unui Microsistem Electronic de ComandăDocument34 paginiProiectarea Unui Microsistem Electronic de ComandăAdrian Capatina100% (1)

- Curs TAPDocument85 paginiCurs TAPMarian SorynÎncă nu există evaluări