Documente Academic

Documente Profesional

Documente Cultură

Luc4 Up

Încărcat de

Smiley Andrei0 evaluări0% au considerat acest document util (0 voturi)

24 vizualizări11 paginiLuc4-uP

Titlu original

Luc4-uP

Drepturi de autor

© © All Rights Reserved

Formate disponibile

DOC, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentLuc4-uP

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

24 vizualizări11 paginiLuc4 Up

Încărcat de

Smiley AndreiLuc4-uP

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 11

Lucrarea 4

Proiectarea modulelor de memorie

1. Scopul lucrarii: prezentarea metodologiei de proiectare a modulelor de memorie pentru

sistemele bazate pe microprocesoare.

2. Consideratii teoretice:

2.1 Tipuri de memorii

Memoriile pot fi clasificate pe baza mai multor criterii:

a. dupa tipul de operatii permise:

- memorii ROM Read Only Memory - care pot fi numai citite (scrierea se face de

catre producator)

- memorii PROM Programable ROM memorii ROM care pot fi inscrise o singura

data de catre utilizator

- memorii U-!PROM Ultra iolet !rasable PROM memorii ROM care pot fi

sterse cu raze ultra"iolete si apoi rescrise de utilizator (numarul de stergeri este limitat

apro#. $%-$%% ori)& scrierea si stergerea necesita dispoziti"e speciale

- memorii !!PROM !lecrically !rasable PROM memorii !PROM ce pot fi sterse

pe cale electrica ( numarul de stergeri este mai mare apro#. $%%%-$%%%%)& nu necesita

dispoziti"e spaciale de scriere si stergere& ciclul de stergere'rescriere este mai lung decit un

ciclu normal de citire

- memorii ()*+, asemanatoare cu memoriile !!PROM dar realizate in alta

te-nologie

- memorii R*M Random *ccess Memory care pot fi citite si scrise in timpul

functionarii normale a sistemului

b.dupa te-nologia de realizare

- memorii bipolare realizate in te-nologie ..)& caracteristici: "iteza mare/ capacitate

mica/ consum mare/ pret relati" mare

- memorii MO+ statice si dinamice realizate cu tranzistoare MO+& caracteristici:

"iteza medie-mare/ capacitate foarte mare (mai ales cele dinamice)/ pret relati" mic/ integrare

usoara/ consum mic/ cele mai utilizate memorii in sistemele cu microprocesoare

- memorii 0MO+ realizate cu tranzistoare MO+ complementare& caracteristici:

consum redus (in regim de stocare a datelor poate sa pastreze informatiile la o tensiune mica

si un consum e#trem de mic)/ capacitate medie/ "iteza medie/ folosite pentru pastrarea

informatiilor de configurare

- memorii !0) realizate in te-nologie cu emitor cuplat& caracteristici: "iteza foarte

mare/ consum foarte mare/ capacitate mica/ dificil de utilizat in sisteme ..)

c. dupa modul de pastrare a datelor:

- memorii ROM pastreaza datele si dupa caderea tensiunii de alimantare

- memorii statice pastreaza datele atita timp cit sunt alimentate

- memorii dinamice pastreaza datele un timp limitat (apro#. 1ms)& necesita

reimprospatarea periodica a informatiilor (prin simularea unor cicluri de citire)

d. dupa pozitia ocupata in raport cu procesorul:

- memoria cac-e memorie de mare "iteza/ de capacitate mica/ intim legata de

procesor

2-$

- memoria principala (operati"a) memorie de capacitate medie-mare/ "iteza medie/

cu acces aleatoriu& ocupa spatiul de adresare fizic al procesorului& pentru a putea fi e#ecutate

modulele de program si date trebuie sa fie prezente in memoria principala

- memoria "irtuala este un concept abstract prin care spatiul fizic de adresare

accesibil direct pentru un program este e#tins peste memoria e#terna& mecanisme de

implementare: segmentarea si paginarea

- memoria e#terna memorie de capacitate foarte mare (teoretic infinita)/ de "iteza

mica/ cu acces semialeatoriu ( pe blocuri)& este implementata pe suport magnetic sau optic

(disc fle#ibil/ -ard-dis3/ disc optic)& se foloseste pentru pastrarea pe termen lung a

programelor si datelor

2.2 Accesul la locatiile de memorie

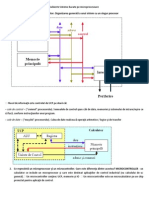

4n sistemele bazate pe microprocesoare modulele de memorie se conecteaza pe

magistra sistemului. *ccesul la locatiile de memorie se realizeaza prin cicluri de transfer

(cicluri masina)/ folosindu-se semnalele magistralei (semnale de adresa/ de date si de

comenzi). Modul de desfasurare a diferitelor tipuri de cicluri de transfer se reprezinta prin

diagrame de timp& diagrama prezinta e"olutia in timp a semnalelor de pe magistrala/ implicate

in transfer. Parametri de timp ai unui ciclu de transfer depind de tipul procesorului/ de

regulile de comunicatie pe magistrala si de tipul de circuite de memorie utilizate. 4n figura de

mai 5os s-au reprezentat diagramele de transfer pentru un ciclu de citire memorie si un ciclu

de scriere memorie.

0iclu de citire memorie

+emnale de adresa *dresa "alida

+. de c-da M!MR6

(citire memorie) (inalta impedanta)

+emnale de date 7ate "alide (citite)

tacces

tmemr

tciclu

0iclu de scriere memorie

+emnale de adresa *dresa "alida

+. de c-da M!M86

+emnale de date

tacces tmem9

tciclu

(igura $ 7iagrame de citire'scriere memorie

)a proiectarea unui modul de memorie trebuie sa se tina cont de urmatorii parametri de timp:

- timpul de acces la citire (tacces) inter"alul de timp intre momentul aparitiei adresei

"alide si momentul in care data citita este prezenta pe liniile de date& uneori timpul de acces se

masoara in raport cu momentul de aparitie al semnalului de comanda M!MR6& daca timpul de

2-1

acces al circuitului de memorie folosit este mai mare decit timpul permis pe magistrala atunci

interfata modulului de memorie trebuie sa prelungeasca ciclul de transfer prin dezacti"area pe

un timp limitat a semnalului R!*7: catre procesor.

- timpul de mentinere a semnalului de comanda M!MR6 acti" (tmemr)

- durata unui ciclu complect de citire sau scriere (tciclu)

- timp de acces la scriere (tacces) inter"alul de timp intre momentul in care adresa

este "alida si momentul de generare a comenzii de scriere& in acelasi mod ca si la citire/ daca

timpul de acces al circuitului de memorie folosit are un timp de acces mai mare atunci

interfata modulului trebuie sa dezacti"eze temporar semnalul R!*7: pentru prelungirea

ciclului de transfer& momentul acti"arii semnalului de scriere se masoara si in raport cu

momentul in care data este prezenta pe magistrala.

- timpul de mentinere a semnalului de scriere (tmem9) este de obicei mai mic decit

tmemr

Obser"atii:

- la citire data este generata dupa aparitia semnalelor de adresa si de comanda si se

mentine un timp scurt dupa dezacti"area acestora

- la scriere data trebuie sa apara pe magistrala inaintea semnalului de scriere si sa fie

"alida pe toata durata de acti"are a semnalului de comanda

- timpul de acces acopera intirzierile care apar intr-un circuit de memorie datorita

circuitelor de decodificare a adresei si de selectie a amplificatoarelor de intrare sau de iesire

- proiectantul trebuie sa aleaga circuite de memorie cu parametri de timp acoperitori

pentru restrictiile impuse pe magistrala& trebuie sa se ia in calcul si intirzierile produse de

circuitele de amplificare din interfata si de pe magistrala.

2.2 Metodologia de proiectare a memoriilor statice

Proiectarea unui modul de memorie se face pe baza unor parametrilor de proiectare

impusi:

- capacitatea memoriei

- modul de organizare ( unitatea elementara de acces la memorie: octet/ cu"int/

dublucu"int)

- tipul de magistrala pe care se conecteaza ( numar de semnale de date si de adrese/

tipuri de semnale de comanda/ parametri de timp pentru cicluri de transfer)

- amplasarea modulului de memorie in spatiul de adresare al procesorului / e#primata

prin adresa sa de inceput (trebuie sa fie un multiplu al capacitatii modulului)

- tipul de circuit de memorie disponibil (poate fi un parametru impus sau unul ales de

proiectant)

- alte cerinte speciale (e#: acces dual de pe doua magistrale/ reinprospatare controlata

centralizat/ implementarea unor mecanisme de detectie a erorilor/ etc.)

!tapele de proiectare ale modulului de memorie sunt:

- sc-ema bloc de principiu se "or e"identia: matricea de memorie/ blocul de

decodificare/ circuitele de amplificare si circuitul de comanda (daca este cazul)

- construirea unui submodul de memorie care respecta organizarea ceruta (pe octet/

cu"int/ dublucu"int)& pentru aceasta se alatura mai multe circuite de memorie pina se obtine

latimea dorita (legare in serie)

- construirea matricii de memorie prin atasarea mai multor submodule construite in

faza anterioara/ pina se obtine capacitatea dorita (legare in paralel)

- proiectarea blocului de decodificare& acest bloc trebuie sa genereze semnale de

selectie pentru submodule si pentru modulul de memorie luat ca intreg& decodificarea se face

pe baza semnalelor de adresa si de comanda

2-;

- proiectarea circuitelor de amplificare& se aleg circuite de amplificare unidirectionale

pentru adrese si comenzi si bidirectionale pentru date

- proiectarea circuitului de comanda& circuitul de comanda "a genera semnale pentru

selectia amplificatoarelor/ pentru "alidarea decodificarii/ pentru controlul sec"entei de citire si

de scriere/ pentru blocarea temporara a semnalului R!*7:/ etc.

- se "erifica respectarea restrictiilor de timp prin adunarea timpilor de intirziere pe

fiecare semnal in parte& critice din acest punct de "edere sunt semnalele de selectie (generate

de decodificator) si semnalele de control ale amplificatoarelor de date.

Pentru e#emplificare se prezinta modul de proiectare a unui modul de memorie a"ind

urmatorii parametri de proiectare:

- capacitatea: <$13cu"inte ($Mo)

- organizarea: pe cu"int ($= biti)/ cu posibilitate de adresare si pe octet

- caracteristicile magistralei (magistrala 4+*):

- 12 de linii de adresa

- $= linii de date

- semnale de comanda: MR706 (citire memorie) si M8.06 (scriere memorie)

- adresa de inceput: 0%.%%%%,

- se folosesc circuite de memorie de =2>?@biti

a. +c-ema bloc de principiu:

Mag. de adrese

Mag. de date *mp. *drese

Mag. de c-zi adr.

+el % +ubmodul % Matricea de

memorie

7ec. +el$ +ubmodul $

+el 1 +ubmodul 1

0. control

0itire'+cr. +ubmodul n

*mp.

date 7ate

+7 +*

(igura 1 +c-ema bloc a modulului de memorie

2-2

b.+c-ema unui submodul de memorie

*% 7% 7%

Mag. adrese *$ 7$ 7$

*$-*$= A.. =23?@biti

*$< 7B 7B

0+6

M8R6 8R6 Mag.

date

*% 7% 7@

*$ 7$ 7C

=23?@biti

*$< 7B 7$<

0+6

8R6

+el-i6

*% +el-i)6

+el-i,6

D,!6

+ubmodulul i (=2>?$= bitiE$1@>octeti)

(igura ; +c-ema submodul 4

c. Matricea de memorie

7%-$<

*%-$=/ D,!6

=23cu"

+el %6 +el

M8R6 M8R6

7%-$<

=23cu"

+el $6 +el

M8R6

AAA

(igura 2. Matricea de memorie 7%-$<

=23cu"

+el B6 +el

M8R6

2-<

d. Modulul de decodificare

*$B * O% +el-%6

*$@ D O$ +el-$6

*$C 0 O1 +el-16

*1% B2)+$;@ A.

*1$ (7ecodif.)

*11 !$6

*1; !16 OB +el-B6

!;

*dr. de inceput 0%.%%%%,

($$%%AA..D) F 7ecodificator

MR76 +el-modul6

M8R6

0ircuit de comanda

(igura < Modul de decodisicare si de comanda

e. Modulul de amplificare

G122 G12<

+*$ *$ +7% * D 7%

+*1 *1 +7$ 7$

+*@ *@ G122 +7B 7B

H%6 7ir

H$6 0+6

G122 G12<

+*C *C +7@ * D 7@

+*$% *$% +7C 7C

+*$= *$= +7$< 7$<

H%6 MR76 7ir

H$6 +el-modul6 0+6

G122

+*% *%

+D,!6 D,!6

MR706 MR76

M8R06 M8R6

H%6

H$6

(igura = Modulul de amplificare

2-=

2.3 Metodologia de proiectare a memoriilor dinamice

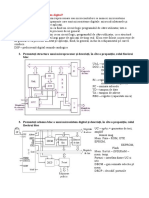

Proiectarea memoriilor dinamice este in principiu similara cu proiectarea memoriilor

statice/ cu urmatoarele amendamente:

- trebuie sa se adauge un mecanism de reimprospatare periodica a memoriei

- adresele trebuie multiple#ate (generarea sec"entiala pe aceleasi semnale a adresei de

linie si a adresei de coloana)

- trebuie sa se genereze semnale de "alidare a adresei de linie (R*+6 - Ro9 *ddress

+elect) si a adresei de coloana (0*+6 - 0olumn *ddress +elect)

- selectia circuitelor se face cu semnalele R*+6 si 0*+6 (e#ceptie fac circuitele de tip

!7O-7R*M care au semnal separat pentru selectia circuitului)

Pentru circuitele R*M dinamice/ multiple#area in timp a adreselor a fost necesara

pentru a reduce numarul de pini ai circuitului de memorie si implicit a dimensiunii acesteia.

7e notat ca circuitele dinamice au o capacitate relati" mare/ ceea ce impune un numar mare

de linii de adresa pentru selectie. Organizarea interna a unei memorii dinamice este sub forma

unei matrici/ cu linii si coloane& selectia unei locatii se face prin specificarea adresei sale de

linie si de coloana.

Reimprospatarea periodica a memoriei este necesara deoarece informatia este pastrata

un timp limitat dupa ultima operatie de citire sau scriere (condensatorul care pastreaza

informatia se descarca in timp). 0ontrolul procesului de reimprospatare poate sa se faca la

ni"elul modulului de memorie sau centralizat la ni"elul intregului sistem. 4ndiferent de

metoda aleasa trebuie sa se asigure ca ciclurile de reimprospatare sa nu se suprapuna peste

ciclurile obisnuite de citire sau scriere. Reimprospatarea se face simultan la ni"elul unei linii

intregi din matricea de memorie. 4n figurile de mai 5os s-au reprezentat diagramele de timp

pentru ciclurile de citire/ scriere si reimprospatare.

*drese *dr. linie *dr. coloana

R*+6

0*+6

8R6

7ate 7ate citite

tras-cas tcas

tacces

tciclu

(igura B 0iclu de citire

2-B

*drese *dr. linie *dr. coloana

R*+6

0*+6

8R6

7ate 7ate de scris

tras-cas tcas

tacces

tciclu

(igura @ 0iclu de scriere

*drese *dr. linie

R*+6

0*+6

8R6

(igura C 0iclu de reimprospatare

!#emplu de proiectare:

- capacitate: $= Mocteti

- organizarea: pe cu"int ($= biti)/ cu posibilitate de adresare si pe octet

- caracteristicile magistralei :

- 1@ de linii de adresa

- $= linii de date

- semnale de comanda: MR706 / M8.06/ Refres-6 (se considera ca

reimprospatarea se solutioneaza centralizat

- adresa de inceput: 7%%.%%%%,

- se folosesc circuite de memorie de $M?@biti

2-@

a. +c-ema de principiu:

Mag. de adrese

Mag. de date Mu#. *drese linie si coloana

Mag. de c-zi adr.

0*+%6 +ubmodul % Matricea de

memorie

7ec. 0*+$6 +ubmodul $

0*+16 +ubmodul 1

0. control R*+6

0itire'+cr. +ubmodul n

*mp.

date 7ate

+7 +*

(igura $% +c-ema bloc a modulului de memorie

b.+c-ema unui submodul de memorie

*% 7% 7%

*dr. linii'col. *$ 7$ 7$

*%-C A.. $M?@biti

*C 7B 7B

0*+6

R*+6 Mag

M8R6 8R6 date

*% 7% 7@

*$ 7$ 7C

$M?@biti

*C 7B 7$<

0*+6

R*+6 R*+6

8R6

0*+-i6

*% 0*+-i)6

0*+-i,6

D,!6

+ubmodulul i ($M?$= bitiE1Mocteti)

(igura $$ +c-ema submodul

c.Matricea de memorie

+c-ema este similara cu cea din figura 2 cu urmatoarele modificari:

- in loc de semnalele +el-i6 se folosesc semnalele 0*+i6

- in loc de adresele *$-$= se folosesc semnalele *%-C

2-C

- la fiecare submodul se conecteaza semnalul R*+6

7%-$<

*%-C/ D,!6 $Mcu"

R*+6 R*+6

0*+ %6 0*+6

M8R6 M8R6

7%-$<

$Mcu"

R*+6

0*+ $6 0*+6

M8R6

AAA

7%-$<

$Mcu"

R*+6

0*+ B6 0*+6

M8R6

(igura $1. Matricea de memorie

d. 0ircuitul de comanda si decodificare

*1$ * O% 0*+%6

*11 D O$ 0*+$6

*1; 0 O1 0*+16

*12 B2)+$;@ A.

*1< (7ecodif.)

*1= !$6

*1B !16 OB 0*+B6

!;

*dr. de inceput 7%%.%%%%,

($$%$AA..D) F 7ecodificator

MR76 +el-modul6

M8R6

R*+6

Refres-6

)inie de intirziere

*dr+el

0*+6

0ircuit de comanda

(igura $; Modul de decodificare si de comanda

2-$%

e.Modulul de amplificare si multiple#are

MUI G12<

+*$ *$ +7% * D 7%

+*1 O *1 +7$ 7$

A. 4%

+*$% *$% +7B 7B

+*$$ 7ir

+*$1 0+6

A.. 4$

+*1% G12<

*dr+el +el +7@ * D 7@

+7C 7C

+*% G122 *%

+D,!6 D,!6 +7$< 7$<

MR706 MR76

M8R06 M8R6 MR76 7ir

+el-modul6 0+6

(igura $2 Modul de amplificare si multiple#are

3. Mersul lucrarii

$. +e studiaza sc-emele si metodologia de proiectare din paragraful precedent.

1. +e proiecteaza urmatoarele tipuri de module de memorie:

- memorie !PROM (capacitate ;13o/ adresare pe octet/ magistrala de tip 4DM-P0 -

4+*/ adresa de inceput (%%%%,)

- memorie R*M statica (capacitate <$1>o/ adresare pe cu"int si octet/ magistrala de

tip 4DM-P0 *./ adresa de inceput *%%%%,)

- memorie 7R*M (capacitate =2Mo/ adresare pe octet/ cu"int si dublucu"int/

magistrala de tip 4DM-P0 G;@=/ adresa de inceput %)

Obser"atie: tipul circuitelor de memorie folosite este la alegerea proiectantului

4.Probleme

$. +a se proiecteze un circuit de comanda pentru un modul de memorie dinamica la care

reimprospatarea se solutioneaza local. 0ircuitul de comanda trebuie sa solutioneze situatiile

de conflict ce pot sa apara intre cererile procesor si cererile de reinprospatare. 4ndicatie:

circuitul de comanda trebuie sa fie un automat de stare.

1. +a se proiecteze cite un modul de memorie cu acces sec"ential de tip (4(O ((irst 4n (irst

Out) si respecti" )4(O ()ast 4n (irst Out).

;. +a se analizeze modul de implementare practica a modulelor de memorie la un calculator

personal (module +4MM/ 74MM) si sa se ridice sc-ema bloc

2. +a se proiecteze o sc-ema de generare si "erificare a bitului de paritate/ la ni"el de octet.

<. +a se caute pe 4nternet date de catalog (configurare pini/ sc-ema interna/ diagrame de timp)

pentru urmatoarele tipuri de memorii: !PROM/ !!PROM/ 0MO+-R*M/ 7R*M/ +7R*M/

!7O-7R*M/ etc.)

2-$$

S-ar putea să vă placă și

- Circuite de MemorareDocument7 paginiCircuite de MemorareSofei Adrian FlorinÎncă nu există evaluări

- Sisteme MultiprocesorDocument13 paginiSisteme MultiprocesorЖан ГанганÎncă nu există evaluări

- Tipuri de MemorieDocument9 paginiTipuri de MemorieFlorin CiudinÎncă nu există evaluări

- Examen PMP2Document23 paginiExamen PMP2Tatar DanielÎncă nu există evaluări

- Memorii SemiconductoareDocument25 paginiMemorii SemiconductoareSimona Alexandra100% (1)

- Asc Examen ModificatDocument59 paginiAsc Examen ModificatThe DanilaÎncă nu există evaluări

- CursArhCap9 1Document33 paginiCursArhCap9 1Victoria AbramovschiÎncă nu există evaluări

- Input Output Rom MoodleDocument15 paginiInput Output Rom MoodleMatei CatalinÎncă nu există evaluări

- Tema 5 ACRDocument37 paginiTema 5 ACRAlex RacuÎncă nu există evaluări

- Componentele Unui Calculator Partea IIDocument22 paginiComponentele Unui Calculator Partea IImihaitapadurariu9Încă nu există evaluări

- Sisteme Cu MicroprocesoareDocument11 paginiSisteme Cu MicroprocesoareAlecz AlexÎncă nu există evaluări

- Teorie PMDDocument44 paginiTeorie PMDNico100% (3)

- Sisteme Cu Microprocesoare ExempleDocument91 paginiSisteme Cu Microprocesoare ExempleBuzoianu StefanÎncă nu există evaluări

- Note de Curs Memoria, Hardisk-Urile, DVD-urileDocument28 paginiNote de Curs Memoria, Hardisk-Urile, DVD-urileadrian_stoÎncă nu există evaluări

- Arhitectura Calculatoarelor C - 10-11Document15 paginiArhitectura Calculatoarelor C - 10-11Popa DaniÎncă nu există evaluări

- 2020 2021 Capitol 1 Partea A II A Hardware 8 Files Merged 2Document277 pagini2020 2021 Capitol 1 Partea A II A Hardware 8 Files Merged 2Larisa Apostu100% (1)

- Cap5 Mem CompletDocument6 paginiCap5 Mem CompletNicola DianaÎncă nu există evaluări

- Initiere ITDocument190 paginiInitiere ITDaniel BușagăÎncă nu există evaluări

- Referat - Clopotel.ro Memoria CalculatoruluiDocument4 paginiReferat - Clopotel.ro Memoria Calculatoruluimaddaa_m100% (3)

- Componentele CalculatoruluiDocument12 paginiComponentele CalculatoruluiSorina Qheorqhita100% (1)

- Analiza Tipurilor de Memorie SRAM Şi DRAM: 1. Obiectivul LucrăriiDocument40 paginiAnaliza Tipurilor de Memorie SRAM Şi DRAM: 1. Obiectivul LucrăriiBenciu Florin ValentinÎncă nu există evaluări

- Bazele Tehnologiei InformatieiDocument18 paginiBazele Tehnologiei InformatieiBira BogdanÎncă nu există evaluări

- Caracteristici RISC, UltraSPARC II Si MagistraleDocument9 paginiCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoÎncă nu există evaluări

- Fisa de Documentare Tipuri de MemoriiDocument6 paginiFisa de Documentare Tipuri de MemoriiCristi NiculaiÎncă nu există evaluări

- 2021-2022 Capitol 1 - Partea A II-a - HardwareDocument66 pagini2021-2022 Capitol 1 - Partea A II-a - HardwareBogdan Piseru100% (1)

- Sisteme Cu MicroprocesoareDocument4 paginiSisteme Cu MicroprocesoareDiana NichiforÎncă nu există evaluări

- Initiere ITDocument119 paginiInitiere ITjulia007100% (1)

- Lectia 2cls9Document14 paginiLectia 2cls9Raluca MotrescuÎncă nu există evaluări

- Sisteme Pentru Achizitia DatelorDocument90 paginiSisteme Pentru Achizitia DatelorAndra MaddalinaÎncă nu există evaluări

- Structura Fizica A PC-uluiDocument13 paginiStructura Fizica A PC-uluiEduard FilipÎncă nu există evaluări

- Informatica 1Document9 paginiInformatica 1Ionut GheorghitaÎncă nu există evaluări

- Intrebari Examen SMPDocument35 paginiIntrebari Examen SMPTudorVasluianu100% (1)

- ASC Curs CompletDocument368 paginiASC Curs CompletkyoaÎncă nu există evaluări

- Curs ICDocument7 paginiCurs ICVanya BadanÎncă nu există evaluări

- Subiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareDocument36 paginiSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoaredetonatorulÎncă nu există evaluări

- Cursul Meu 10 6. Structura Hardware A Unui Sistem MecatronicDocument26 paginiCursul Meu 10 6. Structura Hardware A Unui Sistem MecatronicVadim EriomencoÎncă nu există evaluări

- Lucrarea 1 Structura FizicaDocument13 paginiLucrarea 1 Structura FizicaJoe CercelaruÎncă nu există evaluări

- Curs3 RamonaDocument24 paginiCurs3 RamonaMatei FloreaÎncă nu există evaluări

- MicroprocesoareDocument14 paginiMicroprocesoareDani BobÎncă nu există evaluări

- Referat Arhitectura MicroprocesoarelorDocument5 paginiReferat Arhitectura MicroprocesoarelorrobertexeÎncă nu există evaluări

- Arhitectura Sistemelor de CalculDocument41 paginiArhitectura Sistemelor de CalculVlad MuresanÎncă nu există evaluări

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- Subiecte SMP Modificate de MineDocument7 paginiSubiecte SMP Modificate de MineGabriel VasileÎncă nu există evaluări

- SMC Subiecte RezolvateDocument30 paginiSMC Subiecte Rezolvateandy tudoreanuÎncă nu există evaluări

- Lab 1 MDocument24 paginiLab 1 Mviorica88Încă nu există evaluări

- Cursuri Depanare Hard-SoftDocument15 paginiCursuri Depanare Hard-SoftflanjaÎncă nu există evaluări

- Arhitectura Generala A Sistemelor de CalculDocument51 paginiArhitectura Generala A Sistemelor de CalculDelia DoncaÎncă nu există evaluări

- Sisteme de OperareDocument38 paginiSisteme de Operaresorinc688636Încă nu există evaluări

- Operating SystemDocument40 paginiOperating SystemMichael Woodard100% (1)

- Rezolvari SMDocument16 paginiRezolvari SMconstantinescuana200Încă nu există evaluări

- Arhitectura Microprocesoarelor Burileanu Curs 2015-1-1Document78 paginiArhitectura Microprocesoarelor Burileanu Curs 2015-1-1Vlad NiculceaÎncă nu există evaluări

- Clasificarea Si Caracteristicile Unei Memorii, MEMORII ROM Si RAMDocument7 paginiClasificarea Si Caracteristicile Unei Memorii, MEMORII ROM Si RAMdragosvl0% (1)

- Memoria InternaDocument12 paginiMemoria InternamirelairimiaÎncă nu există evaluări

- Memoria Interna Si ExternaDocument41 paginiMemoria Interna Si ExternaDeekyDZÎncă nu există evaluări

- SD Curs-11Document32 paginiSD Curs-11Smiley AndreiÎncă nu există evaluări

- Tema LMSDocument2 paginiTema LMSSmiley AndreiÎncă nu există evaluări

- Subiecte Examen CIADocument4 paginiSubiecte Examen CIASmiley AndreiÎncă nu există evaluări

- Curs - 1 Comunicatii MobileDocument26 paginiCurs - 1 Comunicatii MobileSmiley AndreiÎncă nu există evaluări

- Generalitifi: Studiul RedresoarelorDocument4 paginiGeneralitifi: Studiul RedresoarelorSmiley AndreiÎncă nu există evaluări