Documente Academic

Documente Profesional

Documente Cultură

3SIE Metode IE 2

Încărcat de

Dragos Reclaru0 evaluări0% au considerat acest document util (0 voturi)

2 vizualizări30 paginicurs sie

Titlu original

3SIE-Metode-IE-2

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentcurs sie

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

2 vizualizări30 pagini3SIE Metode IE 2

Încărcat de

Dragos Reclarucurs sie

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 30

I/E programate

I/E prin întreruperi

Acces direct la memorie (DMA)

Procesoare de I/E

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 1

Principiul I/E prin DMA

Execuția transferurilor prin DMA

Configurații de sisteme care utilizează

transferuri prin DMA

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 2

Dezavantajul I/E programate și al celor prin

întreruperi: UCP este ocupată cu operațiile

de I/E

DMA elimină acest dezavantaj →

transferurile de date sunt executate direct

între memoria internă și sistemul de I/E

Este necesar un modul suplimentar →

controler DMA

Două metode de efectuare a transferurilor

prin DMA →

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 3

1. Prin suspendarea operațiilor efectuate de

UCP și trecerea magistralei în starea de

înaltă impedanță

Transfer “în rafală” (“data break”) sau pe

blocuri

Metoda este necesară, de ex., pentru

unitățile de discuri magnetice → transferul

datelor nu poate fi oprit sau încetinit

UCP este inactivă pentru perioade relativ

lungi de timp

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 4

2. Prin utilizarea intervalelor de timp în care

UCP nu accesează memoria

Transfer prin furt de ciclu (“cycle stealing”)

Blocurile lungi de date sunt transferate

printr-o secvență de tranzacții DMA

intercalate cu tranzacții ale UCP

Metoda reduce rata maximă de transfer, dar

reduce și interferența controlerului DMA la

accesul memoriei de către UCP

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 5

Puncte de suspendare ale activității UCP pentru

transferuri prin DMA și prin întreruperi

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 6

Principiul I/E prin DMA

Execuția transferurilor prin DMA

Configurații de sisteme care utilizează

transferuri prin DMA

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 7

UCP transmite controlerului DMA o

secvență de inițializare

Secvența de inițializare conține:

Direcția transferului (citire sau scriere)

Adresa dispozitivului de I/E implicat

Adresa de început a zonei de memorie cu

care se efectuează transferul

Numărul de octeți sau de cuvinte care

trebuie transferate

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 8

UCP eliberează magistrala și poate executa

alte operații

Controlerul DMA va genera adresele și

semnalele de comandă necesare

transferului

După un ciclu DMA se continuă cu alte

cicluri sau se redă controlul UCP

La terminarea transferului, controlerul

DMA generează o cerere de întrerupere

către UCP

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 9

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 10

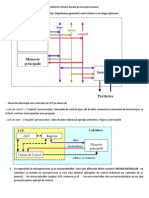

1. UCP încarcă registrele IOAR și DC cu valorile

inițiale necesare → instrucțiuni de I/E

2. Atunci când controlerul DMA este pregătit

pentru transfer, activează semnalul DMAREQ

La următorul punct de suspendare DMA,

UCP eliberează magistrala și activează

semnalul DMAACK

3. Controlerul DMA transferă datele direct cu

memoria principală; registrele IOAR și DC sunt

actualizate

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 11

4. Dacă registrul DC 0, dar dispozitivul de

I/E nu este pregătit, controlerul DMA

eliberează magistrala

UCP dezactivează semnalul DMAACK și preia

controlul asupra magistralei

5. Dacă registrul DC = 0, controlerul DMA

eliberează magistrala și transmite o cerere

de întrerupere către UCP

UCP răspunde prin oprirea dispozitivului de

I/E sau prin inițierea unui nou transfer

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 12

Principiul I/E prin DMA

Execuția transferurilor prin DMA

Configurații de sisteme care utilizează

transferuri prin DMA

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 13

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 14

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 15

I/E programate

I/E prin întreruperi

Acces direct la memorie (DMA)

Procesoare de I/E

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 16

Principiul I/E prin procesoare de I/E (PIE)

Execuția unui program de I/E

Procesoare de I/E Intel

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 17

Deși DMA eliberează UCP de numeroase

operații de I/E, pentru perifericele rapide vor fi

necesare numeroase cicluri de magistrală

În timpul acestor cicluri, UCP trece în starea de

așteptare

Furturile de ciclu vor satura magistrala

Se consumă un anumit timp pentru tratarea

întreruperilor

Modulele de I/E au fost îmbunătățite,

devenind procesoare de I/E (PIE)

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 18

Unele din aceste module de I/E se numesc

și canale de I/E

PIE dispun de un set de instrucțiuni

specializat pentru operații de I/E

UCP transmite o comandă PIE pentru a

executa un program de I/E (program de

canal) aflat în memorie

UCP poate specifica o secvență de operații

de I/E, fiind întrerupt numai la terminarea

întregii secvențe

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 19

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 20

UCP și PIE pot comunica între ele și direct

prin intermediul liniilor de control

Cerere DMA (DMAREQ)

Achitare DMA (DMAACK)

UCP poate atenționa PIE prin activarea

semnalului ATN (Attention) → execuția unui

program de I/E

PIE poate atenționa UCP prin activarea

semnalului IREQ → execuția unui program

de tratare a întreruperii

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 21

Principiul I/E prin procesoare de I/E (PIE)

Execuția unui program de I/E

Procesoare de I/E Intel

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 22

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 23

Principiul I/E prin procesoare de I/E (PIE)

Execuția unui program de I/E

Procesoare de I/E Intel

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 24

Destinate serverelor de înaltă performanță

Proiectate pentru a maximiza rata de

transfer a operațiilor de I/E ale serverelor

prin echilibrarea fluxului de date

Eliberarea procesorului principal de sarcina

executării operațiilor de I/E

Interceptarea întreruperilor generate de

echipamentele periferice

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 25

În subsisteme RAID (Redundant Array of

Independent Disks) → controlul

tranzacțiilor paralele și al algoritmilor de

compresie

Un controler dedicat are un cost mai ridicat

Tehnologii de la egal-la-egal ("peer-to-

peer")

Realizarea unei interfețe între unitățile de

discuri și rețeaua locală → fluxul de date

este gestionat de procesorul de I/E

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 26

IOP331, IOP333

Destinate aplicațiilor de comunicație, de

memorare sau de rețea care necesită

operații de I/E intensive

Conțin interfețe pentru magistrala PCI-X

(IOP331) sau PCI Express cu 8 căi (IOP333)

Accelerare prin hardware pentru aplicațiile

RAID 5

Informația de paritate este distribuită pe mai

multe unități de discuri

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 27

IOP341, IOP342

Conțin interfețe pentru magistralele PCI-X și

PCI Express (8 căi)

IOP348

Destinat pentru subsistemele de memorare

Controler SAS/SATA II pentru 8 porturi

SAS: Serial Attached SCSI

SATA: Serial ATA

Accelerare prin hardware pentru aplicațiile

RAID 6

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 28

Tehnica DMA permite efectuarea transferurilor

de I/E fără intervenția UCP

Două metode de efectuare a transferurilor prin

DMA: pe blocuri sau prin furt de ciclu

Procesoarele de I/E (PIE) dispun de instrucțiuni

specializate pentru operații de I/E

Un PIE poate executa o secvență de operații de

I/E fără întreruperea UCP

UCP și un PIE comunică printr-o zonă de

memorie și prin semnale de control

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 29

Principiul I/E prin DMA

Metoda transferului DMA pe blocuri

Metoda transferului DMA prin furt de ciclu

Execuția transferurilor prin DMA

Schema circuitelor pentru transferuri prin DMA

Principiul I/E prin PIE

Structura unui calculator cu PIE

Comunicația dintre UCP și PIE

Operații pentru execuția unui program de I/E

09.03.2023 Sisteme de intrare/ieșire și echipamente periferice (02-2) 30

S-ar putea să vă placă și

- Introducere PLCDocument45 paginiIntroducere PLCGeta IvanÎncă nu există evaluări

- Ccna 2Document17 paginiCcna 2ralluca123Încă nu există evaluări

- Circuite de Interfata Ale CalculatoruluiDocument7 paginiCircuite de Interfata Ale CalculatoruluiAlex AndruÎncă nu există evaluări

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- Structuri MecatroniceDocument20 paginiStructuri MecatroniceAnton Valentin100% (2)

- S7 300Document0 paginiS7 300expertcontabilÎncă nu există evaluări

- Sisteme Cu Microprocesoare ExempleDocument91 paginiSisteme Cu Microprocesoare ExempleBuzoianu StefanÎncă nu există evaluări

- PLC OmronDocument26 paginiPLC OmronGeta IvanÎncă nu există evaluări

- PMD SubiecteDocument22 paginiPMD SubiecteAdriana PadureÎncă nu există evaluări

- 2SIE Metode IE 1Document50 pagini2SIE Metode IE 1Dragos ReclaruÎncă nu există evaluări

- Curs 5Document70 paginiCurs 5irinel cbnÎncă nu există evaluări

- 4SIE Magistrale 1Document28 pagini4SIE Magistrale 1Dragos ReclaruÎncă nu există evaluări

- Interfete de Intrare-Iesire. Porturi I/ODocument10 paginiInterfete de Intrare-Iesire. Porturi I/Ovali29Încă nu există evaluări

- M&M CursDocument73 paginiM&M CursalbudfÎncă nu există evaluări

- Referat Sisteme de OperareDocument8 paginiReferat Sisteme de OperareDrăgulin Lucian50% (2)

- 6SIE Magistrale 3Document70 pagini6SIE Magistrale 3Dragos ReclaruÎncă nu există evaluări

- SMP SubiecteDocument4 paginiSMP SubiecteIonut CarstovÎncă nu există evaluări

- Asc Examen ModificatDocument59 paginiAsc Examen ModificatThe DanilaÎncă nu există evaluări

- Subiecte SMP Modificate de MineDocument7 paginiSubiecte SMP Modificate de MineGabriel VasileÎncă nu există evaluări

- ASC 3 Structura Unui Calculator (II)Document35 paginiASC 3 Structura Unui Calculator (II)Alis Madalina EneÎncă nu există evaluări

- Curs SM 4Document27 paginiCurs SM 4Lavro IonutÎncă nu există evaluări

- Sisteme Cu Microprocesoare Unitatea de Invatare 6Document33 paginiSisteme Cu Microprocesoare Unitatea de Invatare 6samycatalinÎncă nu există evaluări

- Arhitectura Calculatoarelor: Capitolul 3 Unitatea Centrală de PrelucrareDocument28 paginiArhitectura Calculatoarelor: Capitolul 3 Unitatea Centrală de PrelucrareMindhunter GamerÎncă nu există evaluări

- Controller UlDocument16 paginiController UlnicuboyÎncă nu există evaluări

- Lab 1 MDocument24 paginiLab 1 Mviorica88Încă nu există evaluări

- Introducere in Arhitectura CalculatoarelorDocument20 paginiIntroducere in Arhitectura CalculatoarelorBCOÎncă nu există evaluări

- Microprocesoare-Nr 4Document9 paginiMicroprocesoare-Nr 4sevastian_88626055Încă nu există evaluări

- Cap 2Document65 paginiCap 2VerneeM6Încă nu există evaluări

- 2 Magistrale PDFDocument14 pagini2 Magistrale PDFAndrei VieruÎncă nu există evaluări

- Caracteristici RISC, UltraSPARC II Si MagistraleDocument9 paginiCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoÎncă nu există evaluări

- Gestiunea Sistemului de Intrare-Iesire SO 02 12 2009Document17 paginiGestiunea Sistemului de Intrare-Iesire SO 02 12 2009Cuta LiviuÎncă nu există evaluări

- LaboratorSM 1 2 3Document28 paginiLaboratorSM 1 2 3Felice LazarÎncă nu există evaluări

- Microprocesoare 13Document17 paginiMicroprocesoare 13neacsu92Încă nu există evaluări

- Micro ControllerDocument13 paginiMicro ControllerCatalin LazarÎncă nu există evaluări

- Initiere RouterDocument9 paginiInitiere RoutervadancorneliuÎncă nu există evaluări

- Curs 3 Arhitectura ADSP 2181Document19 paginiCurs 3 Arhitectura ADSP 2181Sanda RuxandraÎncă nu există evaluări

- SMC Subiecte RezolvateDocument30 paginiSMC Subiecte Rezolvateandy tudoreanuÎncă nu există evaluări

- Subiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareDocument36 paginiSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoaredetonatorulÎncă nu există evaluări

- Curs 3 - Conectarea Memoriei Si A Dispozitivelor de I-EDocument19 paginiCurs 3 - Conectarea Memoriei Si A Dispozitivelor de I-EDHM1305Încă nu există evaluări

- 13SIE Adaptoare Grafice 1Document64 pagini13SIE Adaptoare Grafice 1Dragos ReclaruÎncă nu există evaluări

- Multiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaDocument2 paginiMultiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaCirnaROÎncă nu există evaluări

- Structura Tipica de Microprocesor Pe 8 Biti-M Ionita-2023Document13 paginiStructura Tipica de Microprocesor Pe 8 Biti-M Ionita-2023AgerSaboiÎncă nu există evaluări

- Sistemul de Comutaţie EwsdDocument6 paginiSistemul de Comutaţie Ewsdso100% (1)

- Automate ProgramabileDocument9 paginiAutomate ProgramabileRosu AlexandruÎncă nu există evaluări

- C6 MCDocument4 paginiC6 MCBodeaGabrielaÎncă nu există evaluări

- Proiect AFDocument15 paginiProiect AFIon CaimacanÎncă nu există evaluări

- Cursul Meu 10 6. Structura Hardware A Unui Sistem MecatronicDocument26 paginiCursul Meu 10 6. Structura Hardware A Unui Sistem MecatronicVadim EriomencoÎncă nu există evaluări

- Lab.1 MPDocument10 paginiLab.1 MPCristinaÎncă nu există evaluări

- Curs 9Document12 paginiCurs 9george georgeÎncă nu există evaluări

- Raport ProiectDocument20 paginiRaport ProiectSergiu CiupercaÎncă nu există evaluări

- Laborator 3 4Document4 paginiLaborator 3 4Ady MokanuÎncă nu există evaluări

- ECAROMDocument3 paginiECAROMRăzvan DincăÎncă nu există evaluări

- Curs 2 - PrezentareDocument43 paginiCurs 2 - PrezentareCosti AndreiÎncă nu există evaluări

- Curs SAIPDocument114 paginiCurs SAIPLaura ElenaÎncă nu există evaluări

- Lucrarea de CursDocument26 paginiLucrarea de CursAlexandru DumbravaÎncă nu există evaluări

- PM CopybookDocument53 paginiPM CopybookHiro AssassinÎncă nu există evaluări