Documente Academic

Documente Profesional

Documente Cultură

Analiza Via C3 Ezra-T

Încărcat de

delaware4parker0 evaluări0% au considerat acest document util (0 voturi)

8 vizualizări10 paginiTitlu original

Analiza via C3 Ezra-T

Drepturi de autor

© © All Rights Reserved

Formate disponibile

DOC, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

8 vizualizări10 paginiAnaliza Via C3 Ezra-T

Încărcat de

delaware4parkerDrepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 10

Analiza procesorului

VIA C3 Ezra-T

Your Name Here

Grupa 443A

CUPRINS:

1. Introducere

2. Concepte majore ale arhitecturii VIA

C3 Ezra-T

3. Arhitectura generală şi funcţii ale

acesteia

4. Descrierea componentelor cheie ale

arhitecturii Ezra-T

5. Aplicaţii

6. Bibliografie

1. INTRODUCERE

ţ

Microprocesorul C3 Ezra-T este diferit ca arhitectură de orice

alt microprocesor x86. Unicitatea acestui microprocesor constă în

arhitectura să ce permite o mărime a capsulei semnificativ mai

mică, folosind mai puţină putere decât orice alt microprocesor x86.

Microprocesorul VIA C3 are nuclee ce îmbunătăţesc performanţa

(ca MHz dar şi ca instrucţiuni per tact) şi reduce şi mai mult

mărimea pastilei şi puterea disipată faţă de microprocesorul

obişnuit VIA C3 Samuel.

Arhitectura VIA C3, este bazată pe, şi exploateaza direct,

necesităţile de bază ale aplicaţiilor actuale pentru x86. Deşi simple,

aceste concepte nu au fost exploatate în alte arhitecturi.

2. Conceptele majore are arhitecturii VIA C3

I. Doar câteva instrucţiuni x86 domină timpii de execuţie. Intr-

o aplicatie tipica peste 90% din timpul de execuţie este

datorat unor instrucţiuni de baza x86.

Majoritatea instrucţiunilor nu au un impact semnificativ

asupra performanţei. Arhitectura VIA C3, optimizează performanţa

pentru instrucţiunile des folosite, minimizând şi spaţiul alocat pe

chip pentru instrucţiunile rar întâlnite.

Rezultatul în execuţia instrucţiunilor des folosite este la fel

de bună sau mai bună cu a microprocesoarelor similare. De

exemplu pe VIA C3, instrucţiunea load-ALU durează un singur

tact, comparat cu mai multe pe alte microprocesoare.

îmbunătaţirea frecvenţei de ceas are impact mai mare decât

imbunătăţirea CPI (instrucţiuni per tact)

II. Performanţa memoriei este factorul limită în performanţa CPI

In PC-urile moderne busul procesorului este încet comparativ cu

frecvenţa internă. Deci accesul catre memoriile off-chip domină

CPI-ul procesorului şi nu performanţa instrucţiunilor interne.

Microprocesorul VIA C3 adresează acest fenomen prin:

1. Marirea cacheului L1

2. Marirea TLB

3. Prefetching agresiv

4. Cache L2 eficient

III. Diferite segmente ale pieţei au nevoie de diferite

caracteristici ale unui microprocesor

Pentru microprocesoarele cu nucleu Via Ezra-T ţinta sunt

sistemele de operare şi aplicaţiile acestora. Mai exact, sistemele

dektop low-end şi mobile PCs. Deci microprocesorul trebuie să

livreze performanţă ridicată dar la un preţ scăzut. Aceste optimizări

sunt bazate pe analize exhaustive ale comportamentului pieţei

hardware şi software.

IV. Procesoarele Via sunt optimizate ca mărime pentru pastile

mici. Acest fapt reduce atât costurile cât şi consumul de

putere şi fiabilitatea.

3. ARHITECTURA GENERALA SI FUNCTII

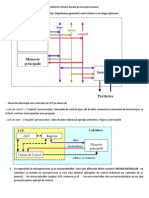

Figura de mai jos ilustreaza structura pipeline de baza a

familiei Via Ezra-T. La un nivel înalt, există 4 grupuri funcţionale

mari : I-fetch, decodare şi traducere, execuţie şi caching de date

Componentele I-fetch aduc octeţii instrucţiunii x86 din I-

cache sau de pe busul extern. Bufferul mare permite ca fetchingul

să continue asincron fată de alte operaţii.

Porţiunea de decodare şi traducere converteşte instrucţiunea

x86 intr-o formă de octeţi pentru execuţia internă.

Ramificările sunt deasemenea identificate, prezise, şi ţinta lor

este adusă inainte de execuţie. Marimea bufferului permite

decodarea şi traducerea asincronă fată de alte operaţii.

Componenta de execuţie transmite, execută şi scoate din uz

instrucţiunile interne.

Cacheul de date se ocupă de încărcarea şi stocarea eficientă a

datelor executate la şi de la memoria cache, bus şi componentele

interne.

La un anumit nivel arhitectura Via C3 pare simpla:

instrucţiunile sunt cerute, executate şi scoase din uz. Numai o

singura instrucţiune poate fi ceruta per tact, şi majoritatea miss-

urilor din cache provoacă încetinirea pipelineului. De fapt

arhitectura este super optimizată pentru obţinerea unei performanţe

ridicate, în domeniul tintă.

Funcţiile importante pentru performanţă sunt:

frecvenţa mare de ceas, facilitată de pipelineul cu 12

nivele

Cache şi TLB mari, onchip: nucleul Via Ezra-T

implementeaza cache şi TLB de nivel mare, care reduce

semnificativ încetinirea datorită traficului ridicat. Acestea

sunt mai mari decât ale oricărui alt microprocesor x86:

o 2 cacheuri L1 de 64KB cu asociativitate în 4 direcţii

o Un buffer L2, de 64KB 4 directional

o 2 TLB-uri cu 128 de intrari

Functii pentru minimizarea conflictelor de acces la

magistrala:

o Cache lock

o Implementarea instrucţiunilor x86 de prefetch

(3Dnow!)

o Data prefetch în D-cache

o Prefetch implicit al instrucţiunilor în I-cache

o Execuţie asincrona, cu coada lunga pentru a pemite

aducerea, executia, decodarea şi traducerea

instrucţiunilor

Implementarea unui bus performant:

o Pană la 8 tranzactii pot fi initiate de microprocesor

o Priorizarea busului

o Bus cu frecvenţe de 100MHz şi 133MHz

Performanţa bună pentru instrucţiunile des folosite:

Instrucţiunile complexe sunt executate rapid. în particular,

pipelineul este aranjat pentru a permite execuţia într-un singur

ciclu a instrucţiunilor ce folosesc mulţi regiştri. Multe instrucţiuni

folosesc mai putine cicluri de tact decât pe alte microprocesoare.

4. Descrierea componentelor cheie ale

arhitecturii Ezra-T

ADUCEREA INSTRUCTIUNILOR (FETCH)

Primele 3 stagii ale pipelineului (I, B, V) aduc instrucţiunile

din I-cache sau busul extern în bufferul de decodare. Pe fiecare

tact, o nouă instrucţiune este adusa din I-cache şi fie 16 octeti (I-

cache) fie 8 octeti (bus) ai instrucţiunii sunt livrati pentru decodare.

DECODAREA INSTRUCŢIUNILOR

Octetii instrucţiunilor sunt tradusi într-un format intern de

către 2 stagii ale pipelineului (F şi X). Aceste unităti sunt la rândul

lor formate din pipelineuri, astfel incat, în general, o instrucţiune

x86 e decodata şi tradusă la fiecare ciclu de ceas.

Stagiul F decodează şi formatează o instrucţiune x86 într-un

format intermediar. Acest proces necestia un singur tact petru

fiecare instrucţiune x86.

Stagiul X traduce forma intermediară a instrucţiunii în

formatul intern de micro-instrucţiuni ale microprocesorului.

PREZICEREA SALTURILOR

Nucleul Ezra-T are implementat un mod unic şi sofisticat de

prezicere a salturilor. Diferite mecanisme prezic toate tipurile de

salturi: jump, call, return, salturi “far”. Aceste tipuri de salturi

reprezintă aproape 25% din instrucţiunile executate. Predictia are

loc cand ramificarea e decodată în stagiul F.

Daca are loc o prezicere, se face fetch asupra tintei saltului.

Aceast fetch poate avea intarzieri de pană la 2 cicluri de ceas.

UNITATEA DE PRELUCRARE A INTREGILOR

Micro-instrucţiunile sunt executate într-un pipeline cu 7 stagii ce e

similar ca structură cu cel de 4 stagii RISC, avand stagii în plus

pentru încarcari în şi din memorie. Aceste micro-instrucţiuni şi

unitatile de execuţie asociate lor sunt foarte optimizate pentru

arhitectura x86.

Stagiile de execuţie ale unitătii cu intregi sunt :

1. Stagiul de decodare (R): micro-instrucţiunile sunt

decodate, registrele de lucru cu intregii sunt accesate,

şi dependentele evaluate.

2. Stagiul de adresare (A) : adresele din memorie sunt

calculate şi trimise catre D-cache.

3. Stagiul de acces la cache (D,G): Cacheul de tip D şi

D-TLB sunt accesate şi datele sunt incarcate dupa un

aliniament, la sfarstiul stagiului G.

4. Stagiul de execuţie : Unitatea ALU de lucru cu

intregii face operatiile. Toate functiile de baza ALU

durează un singur tact. Instrucţiunile de branch sunt

evaluate, şi daca au fost incorect prezise, adresa este

corectata.

5. Stagiul de stocare (S) : Datele ce trebuie stocate

sunt luate şi puse în bufferul aferent.

6. Stagiul de write-back(W): Rezultatele operatiilor

sunt puse în register.

UNITATEA DE LUCRU IN VIRGULA MOBILA

In plus fata de unitatea de lucru cu intregii, mai există o

unitate de lucru în virgula mobilă pe 80 de biti, ce poate executa

instrucţiuni x86 în virgula mobilă în paralel cu cele cu intregi.

Deoarece nucleul VIA Ezra-T nu este făcut pentru aplicatii

mainstream şi deci nu operatiile în virgula mobilă nu-s o prioritate,

această unitate functionează la jumatate din frecvenţa de tact a

procesorului.

5. Aplicatii ale nucleului Ezra-T

Nucleul VIA Ezra-T stă la baza mai multor familii de

procesoare pentru desktop, cu diferite modificări. Acest nucleu se

poate gasi fie în microprocesorul VIA C3 Samuel 2, fie în VIA C3

Ezra.

6. BIBLIOGRAFIE:

1. http://www.via.com.tw/

2. VIA C3 datasheet

S-ar putea să vă placă și

- Arhitectura Sistemelor de Calcul (ASC)Document13 paginiArhitectura Sistemelor de Calcul (ASC)Eduard StanescuÎncă nu există evaluări

- Caracteristici RISC, UltraSPARC II Si MagistraleDocument9 paginiCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoÎncă nu există evaluări

- 8 Multiprocesoare Pe UnDocument63 pagini8 Multiprocesoare Pe UnCezar EnacheÎncă nu există evaluări

- Procesorul (CPU)Document12 paginiProcesorul (CPU)Robert CincaÎncă nu există evaluări

- Proiect: Proiectarea Unui Microprocesor RISCDocument24 paginiProiect: Proiectarea Unui Microprocesor RISCCristian PlescaÎncă nu există evaluări

- Intrebari Centralizate UPDocument22 paginiIntrebari Centralizate UPCristi CiorteaÎncă nu există evaluări

- Arhitect. Calculatoarelor 1Document10 paginiArhitect. Calculatoarelor 1festival23Încă nu există evaluări

- Raspunsuri ACDocument10 paginiRaspunsuri ACAnastasiaÎncă nu există evaluări

- Raspunsuri ACDocument10 paginiRaspunsuri ACAnastasia GhermanÎncă nu există evaluări

- ProcesorulDocument24 paginiProcesorulAndreea Sascău100% (1)

- Arhitectura Calculatoarelor 2004/2005 Cursul 12: 4.2.6 Operaţiuni Pe MagistralăDocument9 paginiArhitectura Calculatoarelor 2004/2005 Cursul 12: 4.2.6 Operaţiuni Pe Magistralăpepa131255Încă nu există evaluări

- Atestare 2Document20 paginiAtestare 2Elena ChicuÎncă nu există evaluări

- ProcesorDocument6 paginiProcesorMariana OrheiÎncă nu există evaluări

- Sisteme Cu Microprocesoare Unitatea de Invatare 5Document12 paginiSisteme Cu Microprocesoare Unitatea de Invatare 5samycatalinÎncă nu există evaluări

- CristianAxenie Assembly Programming Course LabDocument403 paginiCristianAxenie Assembly Programming Course LabMu sicÎncă nu există evaluări

- Referat MicroprocesoareDocument13 paginiReferat MicroprocesoareGîrneț Mihail100% (2)

- MicroprocesoareDocument14 paginiMicroprocesoareDani BobÎncă nu există evaluări

- SMC Subiecte RezolvateDocument30 paginiSMC Subiecte Rezolvateandy tudoreanuÎncă nu există evaluări

- Ac ExamDocument92 paginiAc ExamNegru TatianaÎncă nu există evaluări

- Arhitectura Calculatoarelor C - 7Document10 paginiArhitectura Calculatoarelor C - 7Popa DaniÎncă nu există evaluări

- Microprocesoare 13Document17 paginiMicroprocesoare 13neacsu92Încă nu există evaluări

- Sisteme Cu Microprocesoare ExempleDocument91 paginiSisteme Cu Microprocesoare ExempleBuzoianu StefanÎncă nu există evaluări

- Referat Arhitectura MicroprocesoarelorDocument5 paginiReferat Arhitectura MicroprocesoarelorrobertexeÎncă nu există evaluări

- Familia ATMEL AVR 8bitiDocument21 paginiFamilia ATMEL AVR 8bitiMarlena NeștianÎncă nu există evaluări

- MicrocontrolereDocument22 paginiMicrocontrolereAlexandru-Iulian IfrimÎncă nu există evaluări

- Rezolvari SMDocument16 paginiRezolvari SMconstantinescuana200Încă nu există evaluări

- ATMELDocument20 paginiATMELAnghel NicolaeÎncă nu există evaluări

- Sisteme de Calcul Si Retele de CalculatoareDocument98 paginiSisteme de Calcul Si Retele de CalculatoaremihacamifÎncă nu există evaluări

- Curs - 3 - Sisteme Reconfigurabile de CalculDocument10 paginiCurs - 3 - Sisteme Reconfigurabile de CalculTrepadus GeorgeÎncă nu există evaluări

- Subiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareDocument36 paginiSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoareSubiecte Sisteme Bazate Pe MicroprocesoaredetonatorulÎncă nu există evaluări

- Cursul 3 - Multitasking. Segmentare. Paginare Si Memoria Cache. Arhitectura Procesoarelor Intel. Sistemul de Intreruperi.Document23 paginiCursul 3 - Multitasking. Segmentare. Paginare Si Memoria Cache. Arhitectura Procesoarelor Intel. Sistemul de Intreruperi.Patric PopaÎncă nu există evaluări

- 11.ATMEL AVR 8biti Partea I - Curs MC 17.12.2010Document9 pagini11.ATMEL AVR 8biti Partea I - Curs MC 17.12.2010Chira CristinaÎncă nu există evaluări

- Arhitectura Calculatoaarelor C - 9Document10 paginiArhitectura Calculatoaarelor C - 9Popa DaniÎncă nu există evaluări

- ProblemeDocument13 paginiProblemeRexy RexÎncă nu există evaluări

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- PAPR - Subiect de Examen v2Document4 paginiPAPR - Subiect de Examen v2Laurentiu NitulescuÎncă nu există evaluări

- Ciclul Fetch ExecuteDocument11 paginiCiclul Fetch ExecuteRobert IordacheÎncă nu există evaluări

- Descrierea Generala A Unui Ruter PDFDocument22 paginiDescrierea Generala A Unui Ruter PDFserafimvaÎncă nu există evaluări

- ArhitecturiDocument9 paginiArhitecturiLucia NegruÎncă nu există evaluări

- MicroprocesoareDocument12 paginiMicroprocesoareAndrei DenisÎncă nu există evaluări

- Microcontrolerele AVR Pe 8 BitiDocument19 paginiMicrocontrolerele AVR Pe 8 BitiolgaÎncă nu există evaluări

- Teorie ExamenDocument26 paginiTeorie ExamenRazvy RăzvanuÎncă nu există evaluări

- Referat Seceleanu AndreiDocument12 paginiReferat Seceleanu AndreiAlexINFINITEÎncă nu există evaluări

- Bazele Electronicii Adrian Graur PDFDocument21 paginiBazele Electronicii Adrian Graur PDFCiprian GrumăzescuÎncă nu există evaluări

- Subiecte SMP Modificate de MineDocument7 paginiSubiecte SMP Modificate de MineGabriel VasileÎncă nu există evaluări

- Asi Msi 10Document35 paginiAsi Msi 10Razvan IonutÎncă nu există evaluări

- ACR Examen FinalDocument14 paginiACR Examen FinalCаша КушниренкоÎncă nu există evaluări

- Familia ATMEL AVR 8bitiDocument21 paginiFamilia ATMEL AVR 8bitiRadu BereczkiÎncă nu există evaluări

- 02 Evolutia Arhitecturilor Sist MicroprocesorDocument11 pagini02 Evolutia Arhitecturilor Sist MicroprocesorCM MaryÎncă nu există evaluări

- Proceso RulDocument12 paginiProceso Rulaviorel_alexandruÎncă nu există evaluări

- Unitatea Centrală de PrelucrareDocument3 paginiUnitatea Centrală de Prelucrarealexandranegrea435Încă nu există evaluări

- SIcurs2 PDFDocument68 paginiSIcurs2 PDFLoredana AlexandruÎncă nu există evaluări

- Cursuri Depanare Hard-SoftDocument15 paginiCursuri Depanare Hard-SoftflanjaÎncă nu există evaluări

- Initiere RouterDocument9 paginiInitiere RoutervadancorneliuÎncă nu există evaluări

- Componentele Unui CalculatorDocument6 paginiComponentele Unui Calculatorjohn_vi_2000Încă nu există evaluări

- Referat Studentie Ro-13460Document6 paginiReferat Studentie Ro-13460Andrei PopaÎncă nu există evaluări

- Masurarea A 4 TemperaturiDocument9 paginiMasurarea A 4 TemperaturiDragomirescu CosminÎncă nu există evaluări

- Baza de Date - SD ENERGDocument11 paginiBaza de Date - SD ENERGdelaware4parkerÎncă nu există evaluări

- Baza de Date Teze SD - ETTIDocument21 paginiBaza de Date Teze SD - ETTIdelaware4parkerÎncă nu există evaluări

- Baza de Date Teze SD - IMMDocument7 paginiBaza de Date Teze SD - IMMdelaware4parkerÎncă nu există evaluări

- Baza de Date Teze - SD TRDocument3 paginiBaza de Date Teze - SD TRdelaware4parkerÎncă nu există evaluări

- Baza de Date Teze - SD ISBDocument6 paginiBaza de Date Teze - SD ISBdelaware4parkerÎncă nu există evaluări