Documente Academic

Documente Profesional

Documente Cultură

Suport Curs (Bazele Logice Ale Calculatoarelor) Prof. A.florea

Încărcat de

Ciucur Mircea MihaiTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Suport Curs (Bazele Logice Ale Calculatoarelor) Prof. A.florea

Încărcat de

Ciucur Mircea MihaiDrepturi de autor:

Formate disponibile

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

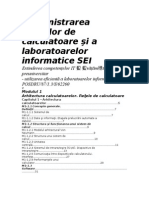

CUPRINS

CUPRINS................................................................................................................. 1

1. INTRODUCERE N SISTEMELE DE PROCESARE A INFORMAIEI .. 4

1.1. CALCULATORUL DISPOZITIV UNIVERSAL DE CALCUL _____________ 8

1.2. STRUCTURA UNUI SISTEM DE CALCUL. PRINCIPII DE BAZ_________ 15

1.3. EXERCIII I PROBLEME _________________________________________ 23

2. REPREZENTAREA INFORMAIILOR. CONVERSII DE VALORI

NTRE SISTEME DE NUMERAIE. ARITMETIC BINAR. OPERAII

LOGICE ................................................................................................................ 25

2.1. REPREZENTAREA INFORMAIILOR N SISTEMELE DE CALCUL ______ 25

2.1.1. REPREZENTAREA INFORMAIILOR NUMERICE FR SEMN. SISTEME DE

NUMERAIE _____________________________________________________________ 29

2.1.2. REPREZENTAREA NUMERELOR CU SEMN _____________________________ 33

2.1.3. REPREZENTAREA NUMERELOR N VIRGUL FLOTANT. FORMATUL IEEE

754 ______________________________________________________________________ 36

2.1.4. REPREZENTAREA INFORMAIILOR ALFANUMERICE STANDARDUL ASCII

_________________________________________________________________________ 40

2.1.5. REPREZENTAREA INFORMAIILOR MULTIMEDIA______________________ 41

2.2. CODIFICAREA INFORMAIEI _____________________________________ 43

2.2.1. CODURI ZECIMALE__________________________________________________ 43

2.2.2. CODURI PENTRU DETECTAREA I CORECTAREA ERORILOR____________ 44

2.3. OPERAII LOGICE PE BII. FUNCII LOGICE. _______________________ 45

2.3.1. FUNCIA I LOGIC (AND)_____________________________________________ 45

2.3.2. FUNCIA SAU LOGIC (OR)____________________________________________ 46

2.3.3. FUNCIA NOT LOGIC ________________________________________________ 46

2.3.4. FUNCIA SAU EXCLUSIV (XOR)_______________________________________ 46

2.4. EXERCIII I PROBLEME _________________________________________ 47

3. STRUCTURI LOGICE DIGITALE. TRANZISTORI. PORI LOGICE.

STRUCTURI LOGICE COMBINAIONALE. UNITATEA ARITMETICO-

LOGIC................................................................................................................ 50

3.1. TRANZISTORUL _________________________________________________ 50

3.2. PORI LOGICE___________________________________________________ 53

3.2.1. INVERSORUL CMOS _________________________________________________ 53

3.2.2. POARTA NOR (NOT OR) ______________________________________________ 53

3.2.3. POARTA NAND (NOT AND) ___________________________________________ 54

3.3. STRUCTURI LOGICE DIGITALE____________________________________ 56

3.3.1. STRUCTURI LOGICE (CIRCUITE) COMBINAIONALE ___________________ 56

3.3.2. PROIECTAREA UNEI UNITI DE CALCUL ARITMETICO-LOGIC _________ 65

3.4. EXERCIII I PROBLEME _________________________________________ 70

4. ELEMENTE PRIMARE DE MEMORARE. REGITRII. MEMORII.

AUTOMATE CU NUMR FINIT DE STRI .................................................. 78

4.1. STRUCTURI LOGICE SECVENIALE _______________________________ 78

4.1.1. BISTABILUL R-S_____________________________________________________ 79

4.1.2. BISTABILUL DE TIP D (DELAY)._______________________________________ 81

4.1.3. REGITRII. __________________________________________________________ 82

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

2 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

4.1.4. MEMORIA __________________________________________________________ 85

4.2. AUTOMATE SECVENIALE I PROGRAMABILE_____________________ 92

4.3. EXERCIII I PROBLEME ________________________________________ 100

5. MODELUL ARHITECTURAL VON NEUMANN. COMPONENTE DE

BAZ. PRINCIPIILE PROCESRII INSTRUCIUNILOR....................... 104

5.1. COMPONENTELE DE BAZ ALE MODELULUI ARHITECTURAL VON

NEUMANN ________________________________________________________ 104

5.2. PRINCIPIILE PROCESRII INSTRUCIUNILOR _____________________ 108

5.2.1. CICLUL INSTRUCIUNII_____________________________________________ 109

5.2.2. TIPURI DE INSTRUCIUNI ___________________________________________ 112

5.2.3. CEASUL PROCESORULUI____________________________________________ 114

5.3. EXERCIII I PROBLEME ________________________________________ 115

6. LC-3 ARHITECTURA SETULUI DE INSTRUCIUNI. CALEA

FLUXULUI DE DATE. ORGANIZAREA MEMORIEI LA LC-3 [Patt03]. 119

6.1. LC-3 ARHITECTURA SETULUI DE INSTRUCIUNI_________________ 119

6.1.1. LC-3 ISA: ORGANIZAREA MEMORIEI I SETUL DE REGITII GENERALI _ 120

6.1.2. LC-3 ISA: FORMATUL INSTRUCIUNII I SETUL DE INSTRUCIUNI _____ 121

6.1.3. LC-3 ISA: APLICAII REZOLVATE ____________________________________ 141

6.2. FLUXUL DE DATE LA LC-3 ISA___________________________________ 145

6.3. EXERCIII I PROBLEME ________________________________________ 148

7. LIMBAJUL DE ASAMBLARE AFERENT ARHITECTURII LC-3.

ASAMBLORUL. ETAPELE GENERRII CODULUI MAIN. TABELA

DE SIMBOLURI................................................................................................. 156

7.1. MOTIVE PENTRU A PROGRAMA N LIMBAJ DE ASAMBLARE _______ 156

7.2. SINTAXA ASAMBLOR LC-3 [Patt03] _______________________________ 158

7.2.1. CORESPONDENA LIMBAJ DE ASAMBLARE LC-3 LIMBAJ MAIN

SPECIFIC LC-3 ISA _______________________________________________________ 162

7.2.2. APELURI SISTEM___________________________________________________ 163

7.3. PROCESUL DE ASAMBLARE ETAPELE GENERRII CODULUI MAIN

___________________________________________________________________ 164

7.3.1. GENERAREA TABELEI DE SIMBOLURI (TS) ___________________________ 165

7.3.2. OBINEREA CODULUI N LIMBAJUL MAIN_________________________ 166

7.3.3. CREAREA LEGTURILOR NTRE MODULE, NCRCAREA I LANSAREA N

EXECUIE ______________________________________________________________ 169

7.4. EXERCIII I PROBLEME ________________________________________ 170

8. NTRERUPERI SOFTWARE LA NIVEL LOW. APELURI DE

SUBRUTINE DIRECTE I INDIRECTE. REVENIRI. SALVAREA I

RESTAURAREA REGITRIILOR. STRATEGIILE CALLER-SAVE

RESPECTIV CALLEE SAVE........................................................................ 177

8.1. NTRERUPERI. DEFINIIE. CLASIFICARE __________________________ 177

8.2. NTRERUPERI SOFTWARE LA NIVEL LOW INSTRUCIUNILE TRAP _ 178

8.2.1. RUTINELE DE TRATARE AFERENTE APELURILOR SISTEM LA LC-3 ISA _ 179

8.2.2. SALVAREA I RESTAUREA REGITRILOR N CAZUL RUTINELOR DE

SERVICIU_______________________________________________________________ 190

8.3. SUBRUTINE ____________________________________________________ 192

8.3.1. MECANISMUL DE APEL SUBRUTINE I REVENIRE ____________________ 193

8.3.2. TRANSFERUL PARAMETRILOR CTRE I DE LA SUBRUTINE___________ 198

8.3.3. SALVAREA I RESTAUREA REGITRILOR N CAZUL SUBRUTINELOR.

RUTINE (FUNCII) DE BIBLIOTEC _______________________________________ 199

8.4. EXERCIII I PROBLEME ________________________________________ 200

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 3

9. STIVA STRUCTUR. PRINCIPIU DE FUNCIONARE. OPERAII

AFERENTE (PUSH & POP).............................................................................. 208

9.1. STRUCTURA DE DATE DE TIP STIV _____________________________ 208

9.1.1. PRINCIPIU DE FUNCIONARE _______________________________________ 208

9.1.2. IMPLEMENTARE HARDWARE I SOFTWARE. _________________________ 208

9.1.3. OPERAII AFERENTE (PUSH & POP) __________________________________ 211

9.1.4. MODUL DE LUCRU PRIN NTRERUPERI HARDWARE. __________________ 214

9.2. OPERAII ARITMETICE FOLOSIND STIVA _________________________ 222

9.3. CONVERSIA INFORMAIEI DIN FORMAT ASCII N ZECIMAL ________ 225

9.3.1. CONVERSIA DIN ASCII N BINAR ____________________________________ 226

9.3.2. CONVERSIA DIN ZECIMAL N ASCII __________________________________ 230

9.4. EXERCIII I PROBLEME ________________________________________ 233

10. FACILITI ALE MAINII PENTRU IMPLEMENTAREA N

HARDWARE A FUNCIILOR DIN PROGRAMELE DE NIVEL NALT.

STIVA DE DATE AFERENT FUNCIILOR.............................................. 237

10.1. OBINEREA CODULUI OBIECT PENTRU O ARHITECTUR DAT ___ 237

10.1.1. DESCRIEREA COMPONENTELOR UNUI COMPILATOR ________________ 238

10.1.2. ETAPELE PARCURSE PENTRU RECOMPILAREA INSTRUMENTELOR

SIMPLESCALAR 3.0 [Flo05] ________________________________________________ 246

10.2. IMPLEMENTAREA GESTIUNII STIVELOR DE DATE ASOCIATE

FUNCIILOR C _____________________________________________________ 249

10.2.1. SUBPROGRAME. GENERALITI. FUNCII C_________________________ 249

10.2.2. STIVA DE DATE AFERENT FUNCIILOR [Patt03, Vin03] _______________ 256

10.3. EXERCIII I PROBLEME _______________________________________ 260

11. INTRODUCERE N RECURSIVITATE. COMPARAIA DINTRE

RECURSIV I ITERATIV N ALEGEREA ALGORITMULUI DE

REZOLVARE A PROBLEMELOR. AVANTAJE / DEZAVANTAJE........ 265

11.1. SCOP I COMPETENE NECESARE_______________________________ 265

11.2. RECURSIVITATEA _____________________________________________ 265

11.2.1. STIVA DE DATE ASOCIAT UNEI FUNCII [Patt03] ____________________ 266

11.3. IMPLEMENTAREA RECURSIVITII LA NIVELUL STIVEI DE DATE _ 274

11.4. TIPURI DE FUNCII RECURSIVE. ELIMINAREA RECURSIVITII ___ 277

11.5. EXERCIII I PROBLEME _______________________________________ 278

12. POINTERI I TABLOURI. TRANSFERUL PARAMETRILOR PRIN

REFERIN. POINTERI SPRE FUNCII .................................................... 282

12.1. INTRODUCERE ________________________________________________ 282

12.2. SEMNIFICAIE I DECLARARE__________________________________ 284

12.3. ALOCAREA I ACCESAREA DE VARIABILE. LEGTURA DINTRE

NIVELUL HIGH I LOW VZUT PRIN INTERMEDIUL MODURILOR DE

ADRESARE ________________________________________________________ 287

12.4. TRANSFERUL PARAMETRILOR PRIN REFERIN LA APELUL

FUNCIILOR_______________________________________________________ 290

12.5. POINTERI SPRE FUNCII________________________________________ 295

12.6. TABLOURI. RELAIA DINTRE POINTERI I TABLOURI_____________ 302

12.6.1. FUNCII CU PARAMETRI DE TIP TABLOU (VECTOR)__________________ 305

12.7. EXERCIII I PROBLEME _______________________________________ 307

BIBLIOGRAFIE................................................................................ 311

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

1. INTRODUCERE N SISTEMELE DE

PROCESARE A INFORMAIEI

tiina Calculatoarelor constituie unul din cele mai dinamice

domenii ale tiinelor inginereti. Dezvoltarea fr precedent a domeniului

Calculatoare i tehnologia informaiei ca o component fundamental a

societii actuale (societate informaional), aflat ntr-o continu schimbare

i progres, este evident i face parte integrant din realitatea pe care o

trim. Evoluia exploziv a tehnologiilor de nalt performan, coroborat

cu acumulri teoretice i experimentale, au fcut posibil ptrunderea n cele

mai diverse domenii ale vieii sociale, economice, industriale, culturale, a

ceea ce poart n mod generic numele de sistem de calcul / calculator,

tehnic / echipament de calcul. Importana informaiei i a sistemelor de

comunicaii cu infrastructura aferent pentru societate i economie se

accentueaz odat cu valoarea i cantitatea informaiei transmis i stocat

pe aceste sisteme. n acest context apare n mod stringent necesitatea

mbuntirii performanelor sistemelor de calcul actuale att din punct de

vedere cantitativ ct mai ales din punct de vedere calitativ. De asemenea,

prezentul tehnologiei informaiei, ca s nu mai spunem de viitor, centrat pe

Internet i tehnologia World Wide Web, impun ca alturi de performana n

sine, fiabilitatea, disponibilitatea i scalabilitatea s devin criterii eseniale,

ceea ce implic iari necesitatea unei noi viziuni pentru proiectantul de

sisteme de calcul. Criticalitatea n societatea informaional, unde informaia

circul prin cyberspaiu

1

fr constrngeri de distan sau vitez, se

datoreaz n egal msur dependenei sporite de informaie, sistemelor care

o furnizeaz dar i vulnerabilitii crescnde pe fondul unui spectru larg de

ameninri de genul rzboiului i polurii informaionale (rzboi cibernetic,

etc.).

ntr-adevr, calculatoarele au fcut progrese importante iar

microprocesoarele sunt principalele rspunztoare pentru aceast cretere

deosebit a performanei. Performana microprocesoarelor a evoluat n

1

Conform enciclopediei Wikipedia [Wik], termenul de cyberspaiu (Cyberspace)

reprezint o metafor atribuit reelelor de sisteme electronice de calcul care permit

stocarea de date i comunicarea online. Dei n anumite lucrri, cyberspaiul este folosit

cu sensul de Internet, termenul trebuie neles ca i un spaiu care cuprinde, identitile i

obiectele care exist n reelele de calculatoare i sunt folosite de indivizii umani n diverse

scopuri [Chi04].

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 5

ultimii 10 ani ntr-un ritm exponenial, cu o rat aproximativ de 60% pe an.

Cercettorii susin c progresele arhitecturale au o pondere mai mare dect

cele tehnologice. Tendinele tehnologice se refer la creterea gradului de

integrare al tranzistorilor pe cip, creterea frecvenei ceasului procesorului,

diminuarea timpul de acces la memorie, reducerea costurilor de

implementare hardware la aceeai putere de calcul ori capacitate de

memorare etc. Tendinele arhitecturale urmresc exploatarea i creterea

paralelismului la nivelul instruciunilor att prin tehnici statice ct i

dinamice sau hibride (cazul arhitecturii IA-64, procesorul Intel Itanium), o

ierarhizare a sistemului de memorie prin utilizarea unor arhitecturi evoluate

de memorii tip cache, reducerea latentei cii critice de program, etc.

n cadrul unor prestigioase conferine tiinifice internaionale dedicate

microarhitecturilor avansate de procesare a informaiei (1999-2007) se

agreeaz tot mai mult ideea potrivit creia pentru a continua i n viitor

creterea exponenial a performanei microprocesoarelor, sunt necesare

concepte noi, revoluionare chiar, pentru depirea limitrilor paradigmei

actuale din punct de vedere conceptual. Exist nc o puternic tendin de

specializare ngust care face adesea ca abordarea domeniului s fie una

nchis n tipare preconcepute. Abordri recente, arat ns c sinergia unor

instrumente aparent disjuncte ale tiinei calculatoarelor converge spre

realizri novatoare ale acestui domeniu de cercetare (arhitectura

calculatoarelor i inteligena artificial). Alte posibile soluii constau n

abordri integratoare de gen hardware-software, tehnologie-arhitectur,

algoritmi, concepte, metode.

Cercetrile n domeniul tiinei Calculatoarelor trebuie s aib un

caracter fundamental, i se recomand a se efectua n universiti

ntruct implic investigarea unor aspecte noi, neimplementate n

actualele microprocesoare. Comunitatea academic i industrial

internaional investete bugete importante n cercetarea arhitecturilor

noi de calcul. Astfel de exemplu, programe de cercetare europene de tip

FP6 (HiPEAC - High-Performance Embedded Architecture and

Compilation) sunt finanate de ctre Uniunea Europeana cu fonduri de

milioane de euro. Abordarea cantitativ i calitativ a acestui domeniu

de studiu i cercetare n Romnia reprezint o necesitate formativ dar

i o necesitate legat de meninerea cercetrii tiinifice romneti n

cadrul tendinelor i standardelor actuale de calitate din Europa de

Vest, Japonia i SUA. Consider c mediul universitar este ideal pentru

dezvoltarea unor asemenea cercetri fundamentale cu privire la

tehnologia informaiei, inclusiv prin diseminarea rezultatelor ctre

studenii anilor terminali i celor masteranzi.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

6 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

Aceast lucrare reprezint o introducere axat pe nelegerea

principiilor fundamentale ale tiinei i ingineriei calculatoarelor i este

destinat n primul studenilor din anul I ai studiilor de licen, dar i celor

care doresc s ptrund n tainele calculatoarelor i care vd n acestea nu

doar simple instrumente de lucru. Cartea de fa, bogat n aplicaii practice,

se bazeaz n parte pe structura lucrrilor Introduction to Computing

Systems: from bits & gates to C & beyond [Patt03] i Computer Organisation

and Design: The Hardware/Software Interface [Pat05], cri folosite ca

referin la cursul de Introducting to Computing Systems introdus pentru

prima dat n universitile americane n toamna anului 1995 de ctre

Profesorul Kevin Compton de la Universitatea Michigan. n acest moment

este predat n mai bine de 75 de universiti americane i la cursuri nrudite

de gen: Introduction to Computing for Biomedical Engineers, Computer

Systems and Programming in C, abordarea optim fiind de 2 semestre. De

asemenea, mai sunt folosite drept referine o suit de peste 30 de lucrri

cri i articole tiinifice att din domeniul software (centrate pe limbaje

i tehnici de programare, compilatoare, structuri de date) ct i hardware

(focalizate pe circuite digitale, automate secveniale, microarhitecturi de

procesare) cu scopul de a exemplifica mai bine necesitatea abordrii

integratoare hardware-software a domeniului tiinei i ingineriei

calculatoarelor. Accentul n lucrarea de fa nu este pus pe memorarea

detaliilor tehnice ci pe interfaa dintre ceea ce software-ul necesit i

respectiv ceea ce hardware-ul poate executa. Sunt prezentate noiuni

introductive dar cu caracter fundamental aferente mai multor discipline din

domeniul tiinei calculatoarelor: limbaje de programare, algoritmi i

structuri de date, compilatoare, sisteme de operare, respectiv arhitectura

calculatoarelor, sisteme cu microprocesoare.

U Abordarea bottom-up a crii este axat pe dou componente:

Structura de baz a calculatoarelor folosind simulatorul LC-3

(Little Computer

www.ece.utexas.edu/~ambler/ee306/Software&Doc/LC3WinGuide.pdf)

dezvoltat la Catedra de Calculatoare i Inginerie Electric,

Universitatea din Austin, Texas. Se pornete de la tranzistoare MOS,

pori logice, bistabili, structuri logice (Multiplexoare, Decodificatoare,

Sumatoare, memorii). Se continu cu modelul de execuie von

Neumann, cu arhitectura unui calculator (procesor) simplu LC-3, cu

limbajul de asamblare aferent acestui procesor. Sunt studiate de

asemenea: interfaa cu tastatura i monitorul, apelurile sistem

(ntreruperi software reprezentnd servicii ale sistemului de operare

prin instruciuni dedicate), modurile de adresare pentru instruciunile

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 7

cu referire la memorie (load / store), mecanismul de apel i revenire

din subrutin.

Exemplificarea la nivelul limbajului C i legtura sau implicaiile

n hardware a structurilor de control, a diverselor tehnici de

alocare a memoriei, lucrul cu stiva, apel de funcii i revenire,

stivele de date aferente funciilor, transmiterea parametrilor n

cazul apelului, recursivitate (care pare magic, dincolo de

nelegere), tablouri i chiar structuri elementare de date. Se va insista,

de asemenea, pe lucrul cu pointeri; pe modul n care C-ul (limbajul,

compilatorul) aloc i acceseaz variabile. Se va exemplifica

artndu-se diferena dintre adresa unei locaii de memorie (p din

declaraia int *p;) i coninutul acesteia (*p din aceeai declaraie).

Se va demonstra ineficiena la nivelul arhitecturii a modului de

adresare indirect memorie (la o adres n memorie se afl adresa

operandului care va fi folosit **cap, n cazul transmiterii de

parametrii unei funcii prin referin).

Aspectul novator al abordrii va consta n prezentarea interfeei

arhitectur (ISA, limbaj de asamblare specific) aplicaie de nivel nalt

(incluznd compilatorul ca i generator de cod pentru respectiva

arhitectur).

U Ce este LC-3 ?

Simulator care descrie funcionarea unei arhitecturi pe 16 bii;

Arhitectura nglobeaz cele mai importante caracteristici ale

procesoarelor Intel 8088 folosit n primul sistem IBM PC n 1981,

Motorola 68000 folosit la Macintosh 1984, sau Intel Pentium III

integrat n sistemele anilor 2000. Simulatorul permite execuia

programelor scrise n limbaj de asamblare LC-3, depanare interactiv

stabilire de puncte de ntrerupere, execuie pas cu pas, vizualizare

coninut regitrii. n urma etapei de asamblare codul surs asamblare

este translatat n limbaj main. De asemenea, poate fi vizualizat i

fiierul care conine tabela de simboluri.

Include porturi de I/O, interfaare cu tastatura i monitorul, apeluri

sistem (ntreruperi software reprezentnd servicii ale sistemului de

operare prin instruciuni), salturi condiionate pe coduri de condiie

=0, 0, set minimal de instruciuni, moduri de adresare pentru

instruciunile cu referire la memorie (load / store) indirect registru,

indexat, mecanism de apel i revenire din subrutin (recursivitatea

determin necesitarea salvrii adresei de revenire n programul apelant

n momentul apelului).

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

8 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

Simulatorul arhitecturii LC-3 permite testare / depanare a programelor

scrise n limbaj de asamblare, stabilire de puncte de ntrerupere. De la

adresa http://users.ece.utexas.edu/~ambler/ee306/software&doc.htm

pot fi descrcate n mod gratuit pentru utilizare n scop didactic att

simulatorul LC-3 (LC301.exe), un simulator realizat n Macromedia

Flash Player versiunea 6, care descrie operaiile de citire scriere

dintr-o memorie cu 4 locaii avnd 3 bii fiecare (memory.exe),

precum i ghidul de utilizare al simulatorului LC-3.

1.1. CALCULATORUL DISPOZITIV UNIVERSAL DE

CALCUL

Universalitatea

Un sistem de calcul

2

(calculatorul) trebuie s ofere urmtoarele

funcionaliti:

cum s adune / scad dou numere

cum s nmuleasc / mpart dou numere

cum s ordoneze alfabetic

nu trebuie proiectat sau cumprat un calculator nou pentru fiecare

nou operaie care trebuie rezolvat.

dac este definit un alt set de instruciuni acelai calculator trebuie

s opereze cu ele.

Istoric

Exceptnd abacul (strmoul socotitoarei folosit pentru prima dat,

cu peste 2000 de ani n urm n China), se poate spune c mainile de calcul

au aprut cu mult (300 de ani) naintea calculatoarelor de azi. Acestea pot

fi clasificate n:

Dispozitive analogice (msurarea unor cantiti fizice cum ar fi

tensiune, curent). Maini de adunat, nmulit folosind diverse rigle

2

Conform enciclopediei Wikipedia [Wik], termenul de sistem de calcul reprezint o

combinaie de componente hardware i software. Un sistem de calcul tipic conine o

memorie i un set de stri care definesc legtura dintre intrrile i ieirile sistemului. Pe

parcursul acestei lucrri s-a folosit pentru simplitate n loc de sistem de calcul noiunea de

calculator. Pe lng calculator ns, sisteme de calcul mai pot fi: sisteme dedicate din

aparatele electrocasnice, din automobile, dispozitive PDA (Personal digital assistants), etc.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 9

gradate logaritmice. Sunt caracterizate de acuratee sczut (Ex:

ceasul).

Dispozitive digitale (calculeaz manipulnd un set finit de digii

sau caractere).

U Prima main de calcul funcional a fost construit de ctre Blaise

Pascal n anul 1642. Reprezenta o socotitoare mecanic, construit din

roi dinate i o manivel, cu care se puteau efectua adunri i scderi.

U n anul 1674, Gottfried von Leibniz a construit o main de calcul care

pe lng adunri i scderi efectua i nmuliri i mpriri. Cutnd s

simplifice mecanismele de efectuare a calculelor a considerat cel mai

potrivit sistemul binar de numeraie.

U Charles Babbage a proiectat n 1840 prima main analitic de uz

general, care (dac ar fi fost posibil construirea ei) ar fi fost

programabil, avnd patru componente principale: magazia (memoria),

moara (unitatea de calcul), seciunea de intrare (cititorul de cartele) i

seciunea de ieire (perforatorul sau imprimanta).

U n 1854 matematicianul englez George Boole a inventat calculul logic

care folosete numai dou valori (adevrat i fals) cu care se pot efectua

operaii de tip And, Or, Not. Aceste funcii (operatori), numite ulterior

algebr boolean, pot fi uor simulate cu ajutorul unei reele de

comutatoare.

U Konrad Zuse (student german) a creat la sfritul anilor 1930 o serie de

maini de calcul folosind relee electromagnetice.

U Calculatoarele electronice au fost iniial propuse sub forma unui aparat

abstract (descriere matematic) care poate realiza sau simula orice tip

de main mecanic. Forma teoretic a fost introdus de Alan Turing n

1936 la Universitatea Cambridge sub denumirea de maina Turing

universal.

Primele calculatoare construite erau foarte diferite de cele de astzi.

Nu doar ca dimensiuni i capacitate (care depind doar de tehnologie), ci

referitor la structura lor fundamental. Acele calculatoare erau construite

pentru a rezolva o singur problem; nu erau universale. Ele constau dintr-o

colecie de uniti funcionale, care puteau face calcule simple.

Programatorii aveau sarcina de a conecta unitile funcionale ntre ele cu

fire (srme), pe care le inserau manual n tot felul de mufe. De exemplu,

dac vroiau s calculeze (a+b)

2

, programatorii luau o unitate care fcea

adunri i una care fcea nmuliri i le cuplau ca n figura 1.1.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

10 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

Figura 1.1. Implementarea n hardware a expresiei (a+b)

2

. Variabilele devin srme,

iar operaiile sunt executate de uniti funcionale

Ideea de a descrie un program folosind un limbaj (i nu prin conexiuni

ntre uniti funcionale) este mai veche; n 1936 Alan Turing folosise

noiunea de main Turing universal (U) pentru a descrie un calculator

universal, care poate executa orice program. Programele erau stocate n

memoria calculatorului, reprezentate ca iruri de numere. Maina Turing (T)

este un calculator abstractizat

(figurahttp://www.cs.cmu.edu/~mihaib/articles/complex/complex-html.html

- turing 1.2) compus din urmtoarele piese [Bud99]:

Figura 1.2. Maina Turing

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 11

1.

n caracter din alfabetul nostru; banda este iniial plin

cu spaii, mai puin partea de la nceput, unde este scris irul cu

le de intrare memorie cu acces linear;

2. e poate mica deasupra benzii, la

n

itate de control, care conine un numr finit de reguli. Unitatea

c are moment dat ntr-o stare; strile posibile

t n numr finit. Fiecare regul are forma

scriu pe band litera Y;

m itire/scriere n direcia D.

n pofid aina Turing poate calcula orice poate fi

calculat cu cele mai performante supercomputere. Un algoritm de calcul este

descris de o astfel de main, prin toate strile posibile, i toate aceste reguli,

numi

e c

ma

ime orice algoritm, s ofere ceva care s fie construibil, i s

poat

Din cauza asta logi

Turing este modelul cel m de calcul care poate fi propus; acest

enun

Church. Ace

nainte de a putea analiza orice alt lucru privitor la teoria complexitii.

O band infinit de hrtie cu ptrele; n fiecare ptrel se poate

scrie exact u

date

Un cap de citire-scriere, care s

st ga sau la dreapta;

3. O un

de ontrol este la fiec

sun fixate dinainte, i sunt

urmtoare:

Dac

sunt n starea Q1;

sub capul de citire este litera X;

atunci:

trec n starea Q2;

ut capul de c

a simplitii ei, m

te reguli de tranziie, care indic cum se trece de la o stare la alta.

De exemplu:

if ((stare_veche==Qi)&&(intrare==Ti))

{

ieire=Oj;

stare_nou=Qj;

}

Orice alte modele de calcul care au fost propuse de-a lungul timpului,

au fost dovedite a fi mai puin expresive, sau tot att de expresive ct maina

Turing. Nimeni nu a fost n stare, pn n prezent, s demonstrez

ina Turing are limitri: adic, dispunnd de operaii elementare

capabile s expr

face lucruri pe care maina Turing nu le poate face.

cianul Alonzo Church a emis ipoteza c maina

ai general

, care nu este demonstrabil n sens matematic, se numete Teza lui

sta este un postulat asupra cruia trebuie czut de acord

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

12 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

Complexitatea unui model de calcul prin prisma modelului Turing, se

definete prin:

Timpul de calcul pentru un ir dat la intrare, este numrul de mutri

fcut de maina Turing nainte de a intra n starea

terminat;

Spaiul consumat pentru un ir de intrare, este numrul de csue de

t de timpul de

execu

Cnd se spune c maina Turing este la fel de puternic ca orice alt

la fel de repede ca orice alt

mode

mai asemntor cu o memorie RAM obinuit.

i; maina Turing universal [Bud99]

este ech

De fapt i o main

Turin

calculato

sunt pro

Pe

lucruri:

Descrierea oricrei maini Turing (T) este finit, i poate fi fcut

cu alfabetul nostru. Dac am o main Turing, pot enumera strile

ei i regulile de tranziie sub forma unui ir de caractere;

Maina universal (U) primete dou intrri pe band: una este

descrierea mainii de simulat (ce trebuie s calculeze), iar a doua

este intrarea pentru care trebuie s simuleze m ina. Maina

universal apoi urm le m inii simulate,

folosind pro

pe band pe care algoritmul le folosete n timpul execuiei

sale.

Anticipnd puin complexitatea unui algoritm este da

ie al acestuia n situaia cea mai defavorabil. Timpul de execuie al

unui algoritm pentru un anumit set de date de intrare este determinat de

numrul de operaii primitive sau "pai" executai i se calculeaz ca suma

tuturor timpilor de execuie corespunztori (pas = linia i din pseudocod

executat ntr-o durat (presupus) constant de timp ci).

model de calcul, nu nseamn c poate calcula

l de calcul, ci c poate calcula aceleai lucruri.

Se pot imagina tot felul de modificri minore ale mainii Turing, care

o vor face s poat rezolva anumite probleme mai repede. De exemplu,

putem s ne imaginm c maina are dreptul s mute capul la orice csu

dintr-o singur micare, fr s aib nevoie s mearg pas-cu-pas; atunci

banda s-ar comporta

Simulr

Demonstraia faptului c maina Turing este att de puternic nct

ivalent cu orice alt model propus de calcul s-a fcut prin simulare.

maina Turing este att de puternic nct se poate constru

g care s simuleze orice alt maina Turing posibil. Att

arele ct i maina universal Turing pot calcula orice ntruct ele

gramabile.

ntru a nelege cum este posibil aa ceva, trebuie realizate dou

a

a rete regulile de tranziie a

pria ei band n acest scop.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 13

Figura 1.3. Maina Turing universal

(model abstract de calcul al unui produs dintre un termen i o sum)

Dezvoltarea dispozitivelor de calcul a fost influenat de cel de-al doilea

rzboi mondial prin ncercrile de calcul a traiectoriilor rachetelor

Collosus i Eniac i respectiv de decodare a codului Enigma folosit de

Germania pentru protecia mesaje

U

lor. Primul calculator digital de

U

e sunt cuplate unitile funcionale, ci este

stocat n memorie, fiind descris folosind un limbaj numit cod-main. n

cod-main, operaiile de executat sunt codificate sub forma unor

numer printr-un

ir de ile

succes, ENIAC (Electronic Numeric Integrator and Computer)

nlocuiete releele electromagnetice cu tuburile electronice. A fost

construit n 1946 de John Mauchly i Presper Eckert de la

Universitatea Pensylvania i coninea 18000 de tuburi electronice i

1500 de relee. Cntrea 20 de tone, avea 20 de regitri, care reinea

fiecare cte un numr zecimal de 10 cifre, era programat prin

intermediul a 6000 de comutatoare i era posibil efectuarea a pn la

500 de adunri sau scderi i 300 de nmuliri pe secund. A fost folosit

de armata american pn n 1952.

n anii '40, matematicianul John von Neumann analizeaz starea de

fapt a calculatoarelor i scrie n 1945 un raport intitulat First Draft of a

Report on the EDVAC (Prima ciorn a unui raport despre EDVAC

Electronic Discrete Variable Automatic Computer), n care sugereaz

o arhitectura revoluionar. n aceast arhitectur, programul nu mai este

reprezentat de felul n car

e numite instruciuni. Programul de executat este descris

instruciuni, care se execut consecutiv. Pe lng unit

funcionale care fac operaii aritmetice, calculatorul mai are o unitate de

control, care citete secvenial instruciunile programului i care trimite

semnale ntre unitile funcionale pentru a executa aceste instruciuni.

Rezultatele intermediare sunt stocate n memorie. Aceast arhitectur se

numete von Neumann.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

14 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

Figura 1.4. Schema simplificat a arhitecturii von Neumann

Marea majoritate a calculatoarelor din ziua de azi sunt bazate pe aceast

arhitectur; noiunea de limbaj-main, i cea nrudit, de limbaj de

programare, folosite pentru descrierea programelor, sunt c

oncepte foarte

ai rapide i

mai ieftine dect cele precedente. A aprut noiunea de familie de

calculatoare: maini care au acelai limbaj de asamblare dar au puteri

(performane) i capaciti diferite. S-a introdus noiunea de

multitasking; aceasta implic existena n memorie a mai multor

programe n acelai timp: cnd unul dintre ele ateapt terminarea unei

operaii de intrare / ieire, un altul poate efectua calcule.

A patra generaie de calculatoare (ncepnd cu 1980) poart

amprenta circuitelor integrate pe scar larg VLSI. Aceast

tehnologie a permis a permis plasarea pe un singur cip a sute de

naturale pentru toi cei care manipuleaz calculatoarele. Von Neumann

propune calculatorul s fie vzut ca sistem de procesare a informaiei

(bazat pe procesor CPU), adic un mecanism care direcioneaz dar

i realizeaz procesarea informaiei.

Apariia tranzistorului, nlocuitorul tuburilor electronice a generat

nceputul celei de-a doua generaii de calculatoare electronice, a

minicalculatoarelor (1955-1965). PDP-1, realizat de firma Digital

Equipment Corporation este un reprezentant al acestor calculatoare. Fa

de cel mai rapid calculator din lume la acea dat, IBM 7090, un

calculator cu tranzistori, PDP-1 era de 2 ori mai rapid si de 9 ori mai

ieftin.

A treia generaie (1965-1980) a debutat prin inventarea de ctre

Robert Noyce a circuitului integrat de siliciu care permitea montarea

pe o singur pastil de siliciu numit cip, de civa centimetri ptrai, a

zeci, apoi mii de tranzistoare. Descoperirea cipului a permis

constructorilor de calculatoare s creeze maini mai mici, m

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 15

milioane de componente electronice elementare. Datorit preului sczut

al calculatoarelor s-a crea

persoan; a nceput perioada calcu

t posibilitatea achiziionrii acestora de fiecare

latoarelor personale (PC).

Procesoarele anilor 80 erau construite din 10 sau mai multe plci

nt capabile s fac

uman investit n respectivul program aflat n execuie.

Marvin Minski, afirma despre programele de Inteligen

Principiu e problemele ce se doresc a fi rezolvate,

sistem etc., sunt scrise ntr-un limbaj (i ntr-o

limb i

carac ractic, de la problema de

rezolv

loc o e

parcu

electronice, fiecare de dimensiuni 18 (inch) i coninnd 50 sau mai

multe componente electronice integrate. La nivelul anilor 2000

procesoarele sunt integrate pe o singur pastil de siliciu de dimensiune

sub 1 (inch). n cazul microprocesoarelor, gradul de integrare al

tranzistorilor pe cip crete cu cca. 55% pe an. Tehnologia de integrare a

microprocesoarelor a evoluat de la 10 microni (1971) la 0.18 microni

(2001), la 0.13 microni (2003) versiunea Northwood a procesorului

Intel Pentium 4 i 0.09 microni (2004) versiunea Prescott a aceluiai

procesor. Frecvena ceasului crete i ea cu cca. 50% pe an.

1.2. STRUCTURA UNUI SISTEM DE CALCUL.

PRINCIPII DE BAZ

Principiul nti P1: Toate calculatoarele (att cel mai mare resurse

foarte mari, ct i cel mai mic, att cel mai rapid frecven ridicat, ct i

cel mai lent, att cel mai scump ct i cel mai ieftin) su

exact aceleai lucruri dac au suficient timp i suficient memorie.

Inteligena aparent a unui sistem de calcul provine din cantitatea

de inteligen

Artificial din anii

80 c: aceste programe care par inteligente iau decizii la fel de proaste

ca i omul numai c mult mai repede [Min82].

l al doilea P2: Toat

ele de operare, compilatoarele,

uzual engleza). Dar toate sunt rezolvate prin electroni

teristici ale acestora (deplasare, vitez, etc). P

at la tensiunea care antreneaz (direcioneaz) fluxul de electroni au

serie de transformri sistematice (dezvoltate i mbuntite p

rsul a mai bine de 50 de ani).

Viitorul va aduce probabil calculatoare cuantice, bazate pe procesoare

moleculare organice, conform calculabilitii ADN, etc.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

16 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

Nivele de transformare: de la Problem de nivel nalt la Circuit

tronic

Etapele succesive prin care se ajunge de la problema de rezolvat

scris ntr-un mod abstract) pn la tensiunea care antreneaz fluxul de

troni sunt urmtoarele:

1. Problem (High level)

2. Algoritm

elec

(de

elec

4.

5.

7.

1. Pro

2. Alg t de operaii

une

pro ice procedur de calcul

bi

:

U Claritatea operaiile algoritmului i succesiunea executrii lor

trebuie s fie descrise clar, precis, fr ambiguiti, astfel nct s

nilor algoritmului

U

goritm.

U i

e

L

algoritmilor care v

reducer a

calcul de ti i al sistemelor dedicate.

3. Limbaj de programare

Arhitectura Setului de Instruciuni (ISA)

Determinarea optim a microarhitecturii

6. Proiectarea la nivel de circuit logic (combinaional / secvenial)

Implementarea circuitelor folosind tehnologia CMOS

blemele sunt definite n limbaj natural. Dezavantaj ambiguitatea.

oritmul reprezint o succesiune finit i ordona

univoc determinate, efectuate mecanic, care aplicate datelor iniiale ale

i probleme dintr-o clas dat, asigur obinerea soluiei acelei

bleme. Cu alte cuvinte un algoritm este or

ne definit care primete o anumit valoare sau o mulime de valori ca

date de intrare i produce o anumit valoare sau mulime de valori ca

date de ieire. Comportarea unui algoritm poate fi diferit n funcie de

datele de intrare. Proprietile algoritmilor sunt

permit o executare mecanic, automat a aciu

U Generalitatea un algoritm permite, nu rezolvarea unei singure

probleme particulare, ci a unei ntregi clase de probleme.

Finitudinea executarea algoritmului trebuie s cuprind un numr

finit de operaii, chiar dac numrul lor este foarte mare. Aceast

proprietate difereniaz metoda de calcul de al

Ef dintre algoritmii care rezolv ciena o anumit problem,

prezint interes numai algoritmii performani pentru care numrul

raiilor care se execut este cel m op ai mic.

a momentul actual sunt realizate cercetri serioase asupra

izeaz nu numai o mbuntire a performanei ci i o

e puterii consumate, vital mai ales la nivelul dispozitivelor de

p handheld

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 17

3.

a)

m

artificial.

Pascal dezvoltat pentru nvarea studenilor s programeze

(foarte apropiat de pseudocod).

b) de nivel sczut (low dependente de maina pe care se proceseaz).

Exist cte un astfel de limbaj specific fiecrei familii de procesoare.

Limbajul de asamblare.

4. Dup cum se poate observa i din figura urmtoare (fig. 1.5),

Arhitectura Setului de Instruciuni (ISA) reprezint interfaa dintre

software (programele de aplicaie / sistem de operare) i hardware-ul

care l execut. ISA specific modul de organizare a memoriei (zon de

date statice i dinamice, de cod, de stiv, zon rezervat nucleului

sistemului de operare), setul de regitri, setul de instruciuni, formatul

instruciunii, tipurile de date utilizate i modurile de adresare

(mecanismul prin care calculatorul / procesorul localizeaz operanzii).

Limbajele de programare sunt de dou tipuri:

de nivel nalt (independente de maina pe care se proceseaz

icroarhitectura hardware)

C destinat manipulrii structurilor hardware ale calculatoarelor

(regitrii, memorie, porturi)

Fortran rezolvarea calculelor tiinifice

Cobol rezolvarea problemelor de procesare a datelor specifice

afacerilor (aplicaii economice)

Prolog folosit n aplicaii care necesit proiectarea unui sistem

expert.

LISP utilizat n rezolvarea problemelor de inteligen

Figura 1.5: Interfaa hardware / software

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

18 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

Cele mai cunoscute ISA la nivelul anului 2001 sunt:

IA-32 ISA (introdus de Intel Corporation n 1979 i utilizat n

prezent i de AMD)

PowerPC (folosite de IBM i Motorola)

Tr

ISA-ul

(uzua compilatorului. Este

denumit

program

aparin

transformare

ieire). Se disting dou

zis:

ana

prog

e:

. Translatarea

Alpha (introdus de Compaq Computer Corporation)

PA-RISC (utilizat de Hewlett-Packard)

SPARC (utilizat de SUN Microsystems)

anslatarea unui program de nivel nalt (fie acesta C, Fortran) n

aferent calculatorului care va executa respectivul program

IA-32) se realizeaz prin intermediul l

faz a unui compilator o succesiune de operaiuni prin care un

de la intrare sufer anumite modificri. Prin trecere [Gol97]

nd unui compilator se nelege o citire a programului dintr-un fiier,

a lui conform unor faze i scrierea rezultatului n alt fiier (de

faze majore ale procesului de compilare propriu-

liza - n care se identific prile constituente fundamentale ale

ramului i se construiete o reprezentare intern a programului

inal, numit co orig d intermediar (analiza lexical produce un

ir de atomi lexicali -> analiza sintactic genereaz -> arborele

sintactic analiz semantic construiete o reprezentare a

programului surs n cod intermediar).

sinteza - genereaz cod main eventual optimizat. Se disting dou

etap

optimizare cod intermediar (scheduling) pentru o anumit

main;

generare de cod main (generare cod ntr-o gam variat de

formate: limbaj main absolut, limbaj main relocabil sau

limbaj de asamblare urmat de alocare de resurse)

din limbaj de asamblare n cod main se realizeaz cu ajutorul

unui asamblor.

Pentru fiecare limbaj de programare i pentru fiecare arhitectur target

trebuie s existe un compilator corespondent. Ex: gcc n sistemul de operare

Linux poate transforma un cod surs C n cod obiect fie pentru procesor

Intel, fie MIPS, fie pentru arhitectura virtual SimpleScalar, n funcie de

bibliotecile i instrumentele software folosite asamblor, link-editor,

interpretor.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 19

5. Microarhitectura organizarea detaliat a unei implementri de ISA.

IA-32 a fost implementat de-a lungul anilor de cteva

microprocesoare diferite, fiecare avnd o microarhitectur unic:

de la Intel 8086 n 1979 pn la Pentium III n 1999.

Alpha ISA este implementat n 4 microprocesoare diferite fiecare

cu microarhitectura proprie 21064, 21164, 21264 i 21364.

Fiecare implementare reprezint o oportunitate pentru proiectanii de

calculatoare de a face diferite compromisuri ntre costul microprocesoarelor

i performana acestora. Optimul se obine pe baz de simulare pe

benchmark-uri standardizate. ISA descrie funcionalitatea de baz iar

unit

setu

mic

Pen

de reaz asupra datelor flotante

pip

imp

aferent ISA impune ce tipuri de uniti funcionale de execuie / staii

de re specifice s fie implementate la nivel microarhitectural.

(regi

uri),

logic

perfo

care

7. Im l

im le

(tranz

stratu

Co

calcul ap

microarhitectura care o implementeaz reprezint modelul particular obinut

n funcie de compromisul cost/performan (numr staii de rezervare i

i funcionale de execuie per fiecare tip de instruciune, numr de

ri de regitri generali, valoarea factorului superscalar al

roarhitecturii, numrul de faze pipeline de procesare Pentium III 14,

tium IV 20, etc).

De exemplu, tipul de date float va afecta numrul de faze pipeline

procesare a unitilor de execuie care ope

(de regul n faze, cu n>1), tipului de date int corespunzndu-i o faz

eline. De asemenea, setul de regitrii logici generali sunt

lementai fizic la nivelul microarhitecturii. Setul de instruciuni

zervare

6. Proiectarea la nivel de circuit logic implementarea n limbaje de

de ri sc ere hardware a fiecrui element component al microarhitecturii

tri, sumatoare, decodificatoare, multiplexoare, predictoare, cache-

urmat de modelare comportamental i simulare la nivel de poart

pentru a face n final un compromis ntre cost / complexitate i

rman. Rezultatul acestei etape l reprezint layout-ul procesorului

va fi implementat hardware n etapa 7.

p ementarea tehnologic la nivel de circuit layout-ul obinut se

p menteaz la nivel de tranzistor prin jonciuni p-n respectiv n-p

istoare CMOS), polarizate n pastila de siliciu pe mai multe

ri.

nform celei mai generale clasificri, componentele unui sistem de

arin uneia dintre urmtoarele categorii:

hardware-ul, care reprezint componenta fizic a unui sistem de

calcul, n care circuitele electronice asigur prelucrarea automat a

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

20 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

informaiei precum i din echipamentele care realizeaz

comunicarea ntre om i calculator. Trebuie s asigure cele 4 funcii

conform teoriei lui von Neumann (de memorare/ de comand i

control / de prelucrare / de intrare-ieire).

software-ul, care reprezint ansamblul de programe care fac

posibil realizarea funciei sistemului de calcul de prelucrare a

protecie etc. Iniial se

afl pe hard-disk iar la pornirea calculatorului se ncarc n

memoria principal. Exemple: DOS, Windows, Linux.

b) progr de programare,

compilatoar atori la

datelor i care constituie suportul logic de funcionare al sistemului

de calcul. Se disting dou mari componente:

a) software de baz (sistemul de operare) care asigur legtura

ntre componentele fizice i logice ale calculatorului, avnd funcii

de gestionare a memoriei, a fiierelor, de

amele de aplicaie (limbaje i medii

e, utilitare) sunt scrise de ctre program

cererea utilizatorilor i codific ntr-un limbaj de programare

algoritmul de rezolvare al problemei respective.

firmware-ul, care este componenta de programe ncrcate n

l

metoda microprogramrii.

memoria fix ROM (Read Only Memory) de ctre productoru

sistemului de calcul; aceast component se afl la limita dintre

hardware i software, reprezentnd partea de software integrat n

hardware, prin

Figura 1.5. Structura unui sistem de calcul

dispozitive periferice a cror rat de transfer (octei /secund) este att de

nct, din motive de timing, face imposibil modul de lucru prin

*) DMA

ridicat ntreruperi. Ele

ceseaz direct memoria fr intervenia procesorului. Exemple de dispozitive DMA sunt ac

discurile magnetice i interfeele video.

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 21

Un t it)

cuia

C, SP, RA)

ni

cesorului circuit electronic ce conine un cristal de

cuar. Acesta genereaz impulsuri la intervale regulate stabilindu-se

unui element cu dou stri s ia una

dintre ele. O succesiunea de bii din memoria intern poate

corespunde unei in u unei date reprezentnd valori numerice,

m

us ecteaz CPU cu memoria i dispozitivele

at dintr-o mulime de fire paralele prin care sunt

te, semnale de comand i control (Read / Write,

ita ea central de calcul / procesare (CPU - central processing un

Realizeaz aducerea din memorie, decodificarea i exe

instruciunilor.

Dispune de o memorie proprie, foarte mic i foarte rapid (Regitri

32, 64 de uz general, P

Execut:

o Operaii aritmetice (add/sub/mul/div)

o Operaii logice (and/or/xor/not)

o Teste de comparaie / salturi condiionate

o Repetat anumite secvene de instruciu

Comand citirea / scrierea din / n memorie, porturi I/O

Comand trecerea n stare nedeterminat (tristate) a busului de date

ntre procesor i memorie n cazul DMA.

Este caracterizat de vitez mare de procesare

Ceasul pro

astfel tactul de lucru al procesorului. f=100 MHz ntr-o secund

(1s) sunt generate 100 de milioane de impulsuri de tact.

Memoria intern realizeaz stocarea programelor i datelor necesare

acestora.

RAM (memorie cu acces aleator) - are caracter dinamic volatil

ROM (memorie cu caracter permanent folosit doar n citire)

Poate fi static sau dinamic caz n care un condensator va

reprezenta celula iniial de memorare, necesitnd rencrcarea sa

periodic (regenerare).

Unitatea de msur elementar a memoriei este bitul (Binary Digit).

Definiia bitului: probabilitatea

str ciuni,

text, diverse coduri (imagini, sunet, text).

Este organizat n diviziuni (locaii sau cuvinte) de o mrime egal

cu cea a numrului de bii ce poate fi procesat simultan de procesor.

O locaie de memorie este caracterizat de adres i de coninut.

Un cuvnt de adres pe m bii poate indexa un spaiu de 2 locaii de

memorie.

(magistral) intercon B

periferice. Este form

transmise adrese, da

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

22 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

INTe

(al

co

una d

nteracioneaz "accidental" cu

domeniul software este complet greit, ntre hardware i software

existnd n realitate o simbioz i o interdependen puternic, nc

neexplorate corespunztor. Procesoarele se proiecteaz odat cu

intre ele este foarte strns:

t standardizate) sunt compilate

pentru arhitectura respectiv iar,

U

tra ac din utilizator un simplu robot ci i

plica

d

pro

resu

rupt Acknowledge), stri ale memoriei sau ale perifericelor (Cereri de

ntrerupere semnalul INT, cereri de transfer DMA, Ready dac este activ

semnific faptul c Memoria / Dispozitivele de Intrare-iEeire sunt pregtite

pentru transferul de date cu CPU). Magistrala reprezint practic un set de

reguli i mijloace de a realiza transferul ntr-un sistem de calcul. Constituie

o cale de a transporta informaii ntre dou dispozitive / echipamente numite

surs i destinaie. Din punct de vedere al dialogului pe magistral

ordonrii transferului de informaii) modulele implicate se pot afla ntr-

in urmtoarele stri:

Master

Slave

Dispozitivele periferice intermediaz comunicaia calculatorului cu

mediul nconjurtor. Se disting dou clase:

a) Dispozitive de Intrare / Ieire tastatur, mouse, scanner, microfon

(intrare) i monitor, imprimant, plotter, difuzor (ieire).

b) Memorii externe cu caracter nevolatil: hard-disk, floppy disk, CD-

ROM, CD-RW. Sunt mai lente dect memoria intern ns sunt mai

ieftine per bit memorat.

n loc de concluzie:

Cele dou "emisfere", hardware i software, n care i desfoar

activitatea cercettorii din tiina calculatoarelor sunt doar aparent

disjuncte. Ideea c arhitectura procesoarelor i

compilatoarele care le folosesc iar relaia d

U benchmark-urile (programe de tes

compilatorul trebuie s genereze cod care s exploateze

caracteristicile arhitecturale, altfel codul generat va fi ineficient.

Preocuprile programatorilor nu trebuie s vizeze doar interfaa care

ge sau diversele artificii care f a

im iile pe care aplicaia creat o are asupra microarhitecturii. Scopul

aplicaiei trebuie s fie utilizarea cu justee att a resurselor software avute

ispoziie ct i a algoritmilor / conceptelor de programare cunoscute la

(motenire, polimorfism, apeluri de funcii prin pointer chiar i acolo unde

nu este cazul). n caz contrar, "rul" (a se citi n primul dificultatea

cesrii rapide datorit ramificaiilor de program, cod obiect masiv,

rse hardware suplimentare) se rsfrnge asupra performanelor

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Introducere n sistemele de procesare a informaiei 23

arh

de fi mai eficiente dac nu ar analiza numai codul obiect al

enchmark-urilor avute la dispoziie dezbrcat de orice semantic ci ar privi

.3 E

1.

2.

procesor (asamblare).

3. de

st pe scurt diferena dintre ISA i microarhitectur.

te ISA sunt implementate n mod normal de o singur

microarhitectur. Invers, cte microarhitecturi pot exista pentru o

singur ISA ?

4. Enumerai nivelele de transformare i dai cte un exemplu la fiecare

nivel.

5. Care sunt principalele provocri (tendine) n proiectarea sistemelor de

calcul i ce compromisuri se fac ?

6. S considerm urmtoarea cutie neagr - black box care preia dou

numere i realizeaz suma lor (vezi figura (a)). Considerm o alt aset

capabil s nmuleasc dou numere (vezi figura (b)). Cele dou asete

astfel de casete

artai cum vor fi interconectate pentru a calcula urmtoarele expresii:

olosind doar o singur caset de adunare i

dou de nmulire)

itecturii. n ce-i privete pe proiectanii de arhitecturi, schemele propuse

acetia ar putea

b

"mai sus" spre sursa de nivel nalt a acestora.

1 . EXERCIII I PROBLEM

Numii i explicai noiunea de algoritm i trei caracteristici ale acestuia.

Pentru fiecare din caracteristici dai un exemplu de procedur care nu o

ndeplinete (3 contraexemple).

vantajele i dezavantajele programrii ntr-un limbaj de Specificai a

nivel nalt fa de programarea la nivel apropiat de

Numii cel puin trei noiuni specificate de ISA (arhitectura setului

ruciuni). Descriei in

C

c

c

pot fi interconectate pentru a calcula p x (m + n) (vezi figura (c)).

Presupunnd c dispunem de un numr nelimitat de

a) a x + b

b) Media aritmetic a patru numere w, x, y, i z.

c) a

3

+ 3a

2

b + 3ab

2

+b

3

(f

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

24 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

7. i a pus bazele miniaturizrii, deschiznd

Log06]

8. ine sunt constructorii i

execute ? Ce performane

i volum avea ? [Log06]

9. Prin ce se caracterizeaz arhitectura revoluionar propus de John von

Neumann ?

10. Selectai rspunsul corect pentru urmtorul enun: Ce este memoria

RAM din punct de vedere al programatorului ? [Zah04]

a) un dispozitiv de stocare n mas

b) o zon de pstrare pentru manipularea / prelucrarea informaiilor

curente.

c) o parte mecanic

11. Selectai continuarea corect pentru urmtorul enun: Un algoritm

[Zah04]

a) este o niruire de comenzi

b) este un lan de instruciuni

c) este o descriere sintetic a unei probleme

d) rezolv problema ntr-un numr finit de pai

e) toate variantele de mai sus sunt corecte.

Ce a revoluionat tehnologia

calea spre apariia calculatoarelor moderne ? [

Care a fost primul calculator digital de succ

unde a fost el utilizat ? Ce operaii putea el s

es, c

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

2. REPREZENTAREA INFORMAIILOR.

CONVERSII DE VALORI NTRE SISTEME DE

NUMERAIE. ARITMETIC BINAR. OPERAII

LOGICE

2.1. REPREZENTAREA INFORMAIILOR N

SISTEMELE DE CALCUL

n acest capitol se urmrete identificarea tipurilor de informaii

reprezentate ntr-un calculator i definirea modurilor de codificare a acestora

n vederea memorrii, prelucrrii i transmiterii. Se vor efectua conversii de

date ntre sistemele de numeraie binar, zecimal i hexazecimal. Se vor

reprezenta numere pozitive i negative n semn i mrime, complement fa

de 1 i complement fa de 2; se vor comenta avantajele i dezavantajele

celor 3 variante de reprezentare. Se vor efectua operaii aritmetico-logice cu

valori numerice reprezentate n cod complementar. Se vor reprezenta

numere n virgul flotant; se vor analiza limitrile acestei forme de

reprezentare i se va face o comparaie cu reprezentarea n virgul fix.

Informaia Definiie. Cuantificare. Convenii de memorare n

calculator. Clasificare.

Definirea informaiei

noiune primar - greu de definit, reprezint un atribut al materiei

mesaj obiectiv care aduce o clarificare privind starea unui

proces care are mai multe stri i elimin nedeterminarea n

legtur cu realizarea unui eveniment.

Cantitatea de informaie - entropia informaional (E)

Claude E. Shannon [Sha48] a introdus noiunea de bit (binary digit)

ca fiind unitatea de msur a informaiei. Shannon afirm c

exist o corelaie ntre informaia produs prin apariia unui

eveniment n cadrul unui experiment i logaritmul inversului

probabilitii de apariie a acestui eveniment. Plecnd de la

aceast definiie, Shannon a introdus conceptual de entropie

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

26 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

informaional (E), element de maxim importan n teoria

informaiei i a tiinei comunicaiilor.

E reprezint o msur a gradului de incertitudine (nedeterminare)

dintr-un sistem. Este dependent de numrul maxim de stri posibile

al respectivului sistem. Gradul de organizare a sistemului este direct

proporional cu cantitatea de informaie nmagazinat i invers

proporional cu entropia informaional a sistemului.

Exemple: aruncarea unei monede, aruncarea unui zar

x

1

x

2

x

n

p

1

p

2

p

n

E = p

i

log

2

p

i

Observaie: Entropia devine maxim (dezordine maxim) pentru o

distribuie echiprobabil. Astfel dac n n

n

p

i 2

log max E , , 1 i ,

1

= = = =

valoare ce reprezint numrul minim de bii necesar codificrii entropiei.

Analog, entropia devine minim (ordine maxim) cnd

. 0 0 log ca conventie prin d consideran 0, min E , , 1 , 0 si 1

2

= = = = = = n i k i p p

i k

1 byte) lii octeilor sunt

kilo/m

1Po (peta octet) = 2

50

(1099511627776)o 10

15

o

Co

De exemplu, pentru 2 stri echiprobabile entropia este:

E = - 2*0.5*log

2

0.5 = 1 unitatea de informaie (1 bit). O niruire de 8

bii formeaz un octet ( . Multip

ega/giga/tera/peta octeii:

1ko (kilo octet) = 2

10

(1.024)o 10

3

o

1Mo (mega octet) = 2

20

(1.048.576)o 10

6

o

1Go (giga octet) = 2

30

(1.073.741.824)o 10

9

o

1To (tera octet) = 2

40

(1099511627776)o 10

12

o

nvenii de memorare a informaiei n calculator

Memoria intern a unui calculator este alctuit dintr-o succesiune de

locaii; fiecare locaie are un numr fix de bii, numr stabilit de ctre

proiectantul de arhitectur n momentul n care se decide modul de

organizare a memoriei. Astfel, n mod uzual numrul de bii ai unei locaii

este un multiplu de 8. Locaia este unitatea elementar de adresare a unei

memorii; la majoritatea procesoarelor (cu excepia microcontrolerelor)

informaia din memorie nu se poate adresa la nivel de bit. Indexarea

locaiilor de memorie se face, pe baz de adres. La procesoarele Intel,

MIPS unitatea minim de adresare (locaia de memorie) are 8 bii. n acelai

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Reprezentarea informaiilor. Conversii de valori ntre sisteme de numeraie. Aritmetic

binar. Operaii logice 27

timp

ai

semnificativ n poziia stng. Importana acestei convenii se remarc n

cazul operaiilor logice de deplasare i rotire spre dreapta sau spre stnga.

ns memoria se poate adresa la nivel de semi-cuvnt (halfword 16

bii), cuvnt (word 32 bii) sau dublu-cuvnt (double 64 bii).

Ca n cazul oricrui sistem de numeraie poziional (8,10,16) i n

cazul sistemului binar bitul cel mai puin semnificativ al unui octet (bitul

D

0

) se afl n poziia cea mai din dreapta a datei, iar bitul cel m

c o dat este reprezentat pe un nu Da mr mai mare de octei atunci se

pune problema modului de amplasare a octeilor la adrese consecutive de

memorie (aa ordine a octeilor). Procesoarele pot numerota octeii

din interiorul unui cuvnt de 32 de bii astfel nct octetul cu numrul cel

ai mic este fie cel mai din stnga fie cel mai din dreapta. Exist dou

conve ii

- tiv a numrului se pune la

adrese mai mici (se pune n faa).

Byte #

numit

m

n de reprezentare:

big endian partea mai semnifica

0 1 2 3

eaz

la adrese mai mici (se pune n fa).

Byte #

- little endian partea mai puin semnificativ a datei se amplas

3 2 1 0

De exemplu n convenia little endian o valoare hexazecimal de

forma 11223344h se memoreaz la adresa fizic 400h n felul urmtor:

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

28 Introducere n tiina i ingineria calculatoarelor. Interfaa Hardware - Software

De exemplu, procesoarele Alpha, Intel i MIPS folosesc convenia

little-endian, n timp ce n cazul procesoarelor MacIntosh, HP Bobcat sau

SPARC ordinea folosit este big-endian.

Cl f

tete c una din funciile de baz ale calculatorului este de

prelucrar r. Pentru a putea fi prelucrate, informaiile trebuie

reprezentate (codificate) ntr-un anumit format, pe baza unor reguli bine

definite i lipsi d rezentare a informaiilor

depinde de tipul o prioritare urmrite.

Inform

- program

-

semn numere naturale

semn numere ntregi

arte ntreag i parte fracionar (practic

a numerelor fracionare)

o multimedia

in care

asi icare

Se reamin

e a informaiilo

te e ambiguiti. Modul de rep

inf rmaiilor i de obiectivele

aiile prelucrabile pe un calculator sunt de mai multe tipuri:

(executabil) secven de coduri de instruciuni

date:

o numerice:

ntregi

fr

cu

reale numere cu p

sunt numere din mulimea Q

o alfanumerice text

o logice adevrat/fals

audio

video

imagini statice

secven de cadre (film)

o semnale mrimi fizice de proces, detectate prin senzori sau

transmise prin elemente de acionare

Interschimbarea noiunilor dat respectiv informaie este larg

rspndit n lumea larg, nefcndu-se distincie de cele mai multe ori ntre

ele, fiind tratate ca i sinonime. n realitate ns [Bel04], exist diferene

ntre cele dou noiuni: informaia are un coninut semantic (obinut n

urma unui proces de interpretare), pe cnd data este forma fizic de

reprezentare a unei informaii. Potrivit cercettorului Russell Ackoff

[Ack89] coninutul minii umane poate fi clasificat n 5 categorii (fiecare

categorie bazndu-se pe cele de dinaintea sa): date, informaii, cunoatere,

nelegere i nelepciune. Se pune ntrebarea ce decurge din aceste

observaii: Calculatorul prelucreaz date sau informaii? Dac se consider

n mod simplist c un program specific o secven de transformri pr

U

s

i

n

g

j

u

s

t

f

o

r

s

t

u

d

y

i

n

g

a

n

d

n

o

n

-

c

o

m

e

r

c

i

a

l

p

u

r

p

o

s

e

s

Reprezentarea informaiilor. Conversii de valori ntre sisteme de numeraie. Aritmetic

binar. Operaii logice 29

trec d

ate fi o valoare de

tempe

cifrei 1 ( xist ns i cazuri, mai ales n

dome torul identific

i per ii, care nu mai sunt simple date.

forme

de re z Alegerea unei anumite forme de codificare se

face n funcie de anumite obiective urmrite, cum ar fi:

reprezentarea coerent, a informaiilor n vederea stocrii,

simplificarea operaiilor de prelucrare, stocare i transmitere

oluri i un set de reguli pentru reprezentarea

oluri (numere

derate (Ex: bina

i neponderate (Ex: codul Gray). Un sistem ponder

i i t o p enta onderile sunt

va nsiderndu-se baza

eraie ponderat se

defin te n felul urmtor:

x

n

*b +...x

2

*b +x

1

*b +x

0

(3)

Codurile neponderate a fiecr cimale o tetrad binar,

cifrele binare neavnd ns semnificaia unor ponderi. Codul Gray are

atele iniiale n scopul generrii unui rezultat, atunci se poate spune c

un calculator prelucreaz date. Prin interpretarea datelor un utilizator le

transform ns n informaie. De exemplu data 49 po