Documente Academic

Documente Profesional

Documente Cultură

Interfața Serială SPI

Încărcat de

mosubadeaTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Interfața Serială SPI

Încărcat de

mosubadeaDrepturi de autor:

Formate disponibile

Interfaa serial SPI

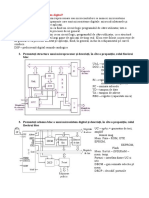

Interfa a seriala SPI (Serial Peripheral Interface) este o interfaa sincron standard de mare vitez, ce opereaz n mod full duplex. Numele ei a fost dat de Motorola. Ea e folosit ca sistem de magistral pentru sincron serial transmitere de date, unde circuite digitale pot s fie interconectate pe principiul master-slave. Aici, modul master/slave nseamn, c dispozitivul (circuitul) digital master iniiaza cuvntul de date. Mai multe dispozitive (circuite) digitale slave sunt permise cu slave select individual, adic cu selectare individual.

Interfaa

SPI-ul are patru semnale logice specifice.

SCLK - Ceas serial (output din master) MOSI/SIMO - Master Output, Salve Input (output din master) MISO/SOMI - Master Input, Slave Output (output din slave) SS - Slave Select (active low; output din master)

Operare

Interfaa SPI poate opera cu un singur dispozitiv master i unul sau mai multe dispozitive slave. Dac un singur dispozitiv slave este utilizat, pinul pentru SS poate fi setat pentru logic "low"/"jos" dac dispozitivul permite. Unele slave-uri necesit "falling edge" (nalt/highjoas/low tranziie) al slave-selectului pentru a iniia o aciune la fel ca Maxim MAX1242 ADC, care ncepe conversia la tranziia respectiv. Cu multiple slave-uri, un semnal SS independent este necesar de la master pentru fiecare dispozitiv (circuit) digital slave. Majoritatea dispozitivelor slave au trei stri logice, aa c semnalul MISO devine "deconectat" (ieire n gol) atunci cnd dispozitivul nu este selectat. Dispozitivele fra trei stri logice nu pot mpri (nu pot participa la) magistrala SPI cu alte dispozitive; doar acele slave-uri pot comunica cu master-ul i doar dac au activat chip-selectul.

Transmisia de date

Pentru a ncepe comunicarea, master-ul mai nti configureaz ceasul, folosind o frecven mai mic sau egal cu maximul frecvenei suportata de slave. Aceste frecvene sunt de obicei n intervalul 1-70 MHz. Atunci master-ul seteaza slave select-ul jos pentru chip-ul dorit. Dac este necesar o perioada de ateptare (ca la conversia analog-digital) atunci master-ul ateapt cel puin acea perioad de timp nainte de a ncepe ciclurile de ceas. n timpul fiecrui ciclu de ceas SPI, apare o transmisie full duplex: master-ul trimite un bit pe linia MOSI; slave-ul il citeste de pe aceeasi linie

slave-ul trimite un bit pe linia MISO; master-ul il citeste de pe aceeasi linie Nu toate transmisiile necesita toate aceste patru operatii pentru a putea fi intelese dar ele se petrec. In mod normal, transmisiile implica doi registrii schimbati de o lungime a cuvantului, cum ar fi opt biti, unul in master si unul in slave; ei sunt conectati intr-un inel. Informatia este de obicei intai schimbata cu cel mai semnificativ bit, in timp ce schimband cel mai putin semnificativ bit in acelasi registru. Dupa ce acel registru a fost transmis, master-ul si slave-ul si-au schimbat valorile din resgistrii. Atunci fiecare dispozitiv ia acea valoare si face ceva cu ea, cum ar fi scrierea in memorie. Daca mai sunt date de schimbat, registrii de schimb sunt incarcati cu noi date si procesul se repeta. Transmisiile pot include oricate cicluri de ceas. Cand nu mai sunt date de transmis, master-ul opreste comutarae ceasului. In mod normal, el atunci deselecteaza slave-ul. Adesea transmisiile sunt de cuvinte a opt biti, si master-ul poate initia multiple transmisii daca are nevoie. Cu toate astea, alte marimi ale cuvantului sunt obisnuite, cum ar fi cuvinte de 16 biti pentru controller-ul de touchscreen sau codecuri audio ca TSC2101 de la Texas Instruments; sau cuvinte de 12 biti pentru diverse convertoare digitale-analog sau convertoare analog-digitale. Fiecare slave de pe magistrala care nu a fost activat folosind slave select-ul nu trebuie sa ia in considerare semnalul de ceas si semnalul MOSI si sa nu transmita MISO. Master-ul trebuie sa selecteze doar un slave la un moment dat.

Polaritatea si faza ceasului

In plus fata de setarea frecventei ceasului, master-ul trebuie sa configureze polaritatea si faza ceasului respectand datele. Aceste doua optiuni a fost numite CPOL si CPHA in "Freescale's SPI Block Guide", iar cei mai multi producatori le-au adoptat.

Diagrama de timp este afisata in dreapta. Timpul este descris mai jos si se aplica atat dispozitivelor master cat si celor slave. La CPOL=0 valoarea ceasului este zero Pentru CPHA=0 data este capturata pe tranzitia jossus si este propagata pe tranzitia susjos a ceasului. Pentru CPHA=1, data e capturata pe tranzitia susjos si propagata pe tranzitia jossus. La CPOL=1 valoarea ceasului este unu Pentru CPHA=0 daca e capturata pe tranzitia susjos a ceasului si propagata pe tranzitia jossus. Pentru CPHA=1 data e capturata pe tranzitia jossus si propagata pe tranzitia susjos.

Cu valoarea CPHA=0 data trebuie sa fie stabila o jumatate de ciclu inainte de primul ciclu de ceas. Pentru toate modurile CPOL si CPHA, valoarea initiala a ceasului trebuie sa fie stabila inainte ca chipul sa selecteze linia activa.

S-ar putea să vă placă și

- Interfața Serială SPIDocument3 paginiInterfața Serială SPITacu AlexandruÎncă nu există evaluări

- Notite Curs 07 15 Noiembrie 2021Document34 paginiNotite Curs 07 15 Noiembrie 2021Rusu VictorÎncă nu există evaluări

- Descriere SPIDocument7 paginiDescriere SPIcoca_cÎncă nu există evaluări

- Proiectare InterfataDocument15 paginiProiectare InterfataDenisa MariaÎncă nu există evaluări

- Magistrala SPIDocument10 paginiMagistrala SPIone_blanche6175Încă nu există evaluări

- Curs SPIDocument36 paginiCurs SPIalinupÎncă nu există evaluări

- Interfete de Comunicatie SerialaDocument13 paginiInterfete de Comunicatie SerialaSzemida SitaÎncă nu există evaluări

- Cheatsheet Colocviu CN2 UltimDocument2 paginiCheatsheet Colocviu CN2 UltimVlad PopescuÎncă nu există evaluări

- ExamenDocument214 paginiExamenCristi Ro279Încă nu există evaluări

- Magistrala I2CDocument9 paginiMagistrala I2CHamat AfinÎncă nu există evaluări

- Curs ICDocument7 paginiCurs ICVanya BadanÎncă nu există evaluări

- C07 SpiDocument12 paginiC07 SpiAlee ZuZyÎncă nu există evaluări

- Interfaţa SPIDocument1 paginăInterfaţa SPIStefy NicolaeÎncă nu există evaluări

- Multiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaDocument2 paginiMultiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaCirnaROÎncă nu există evaluări

- Proiectare Cu MicroprocesoareDocument29 paginiProiectare Cu MicroprocesoareDana BalanescuÎncă nu există evaluări

- Cobra ManualDocument10 paginiCobra ManualAlina StanciuÎncă nu există evaluări

- Protocoale de Comunicare PDFDocument9 paginiProtocoale de Comunicare PDFGheorghe MorosanÎncă nu există evaluări

- Sisteme Cu Microprocesoare ExempleDocument91 paginiSisteme Cu Microprocesoare ExempleBuzoianu StefanÎncă nu există evaluări

- Magistrala I2CDocument20 paginiMagistrala I2CDaniel PanescuÎncă nu există evaluări

- Laborator 3 CIDDocument6 paginiLaborator 3 CIDMihai BihalacheÎncă nu există evaluări

- MICROC Curs 7Document25 paginiMICROC Curs 7Cristi Ro279Încă nu există evaluări

- Microcontrolerul 80C51Document28 paginiMicrocontrolerul 80C51Lacatus ValentinÎncă nu există evaluări

- Lucrarea 6Document4 paginiLucrarea 6Dicol OliviuÎncă nu există evaluări

- Proiect Comunicatii de DateDocument9 paginiProiect Comunicatii de DateTanase AlexandruÎncă nu există evaluări

- Coprocesorul Matematic (Arhitectura CalculatoarelorDocument19 paginiCoprocesorul Matematic (Arhitectura CalculatoarelorCatalin CataÎncă nu există evaluări

- Curs 7 MAP2014Document28 paginiCurs 7 MAP2014Dark1337Încă nu există evaluări

- Arhitectura Calculatoarelor C - 5Document9 paginiArhitectura Calculatoarelor C - 5Popa DaniÎncă nu există evaluări

- ElectronicaDocument9 paginiElectronicaLucianno NmÎncă nu există evaluări

- Sisteme Cu MicroprocesoareDocument4 paginiSisteme Cu MicroprocesoareDiana NichiforÎncă nu există evaluări

- Microsistem Cu Microprocesor Z80Document14 paginiMicrosistem Cu Microprocesor Z80neo_22Încă nu există evaluări

- Aplicatii PLCDocument92 paginiAplicatii PLCIulian RacovițăÎncă nu există evaluări

- Cheatsheet CN2Document2 paginiCheatsheet CN2Vlad PopescuÎncă nu există evaluări

- Curs TAPDocument85 paginiCurs TAPMarian SorynÎncă nu există evaluări

- Cursuri FinalDocument160 paginiCursuri FinalMadalina-Valentina TaftaÎncă nu există evaluări

- SMPDocument222 paginiSMPPetreCaracaleanuÎncă nu există evaluări

- Arhitectura Calculatorului DidacticDocument13 paginiArhitectura Calculatorului DidacticMădălina HapciuÎncă nu există evaluări

- TimerDocument15 paginiTimerGabriel BraşoveanuÎncă nu există evaluări

- Referat ICA - Microcontrolerul AT89C52Document10 paginiReferat ICA - Microcontrolerul AT89C52tasseluÎncă nu există evaluări

- Asi Msi 10Document35 paginiAsi Msi 10Razvan IonutÎncă nu există evaluări

- Capitolul11 - SPIDocument8 paginiCapitolul11 - SPIOaNa MironÎncă nu există evaluări

- UPUS ExamenDocument17 paginiUPUS ExamenAlexandru PiscaÎncă nu există evaluări

- Teorie ExamenDocument26 paginiTeorie ExamenRazvy RăzvanuÎncă nu există evaluări

- Proiect CidDocument8 paginiProiect CidDumitrascu RodicaÎncă nu există evaluări

- ASC Curs CompletDocument368 paginiASC Curs CompletkyoaÎncă nu există evaluări

- SEP - TMS320C10 - Cap13Document21 paginiSEP - TMS320C10 - Cap13Mops LightÎncă nu există evaluări

- Porturile Unui CalculatorDocument16 paginiPorturile Unui Calculatorseitan_calinÎncă nu există evaluări

- 1) Consideratii Asupra Unui Sistem DSP, Esantionarea Si CuntificareaDocument2 pagini1) Consideratii Asupra Unui Sistem DSP, Esantionarea Si CuntificareaCirnaROÎncă nu există evaluări

- Microcontrolere PIC de La A La ZDocument165 paginiMicrocontrolere PIC de La A La ZMihai BrindusoiuÎncă nu există evaluări

- Rezolvare:: Probleme de 1pDocument63 paginiRezolvare:: Probleme de 1pChipeșu CiprianÎncă nu există evaluări

- 1) Consideratii Asupra Unui Sistem DSP. Conversia Digital AnalogicaDocument3 pagini1) Consideratii Asupra Unui Sistem DSP. Conversia Digital AnalogicaCirnaROÎncă nu există evaluări

- Caracteristici RISC, UltraSPARC II Si MagistraleDocument9 paginiCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoÎncă nu există evaluări

- Proiectarea Microsistemelor DigitaleDocument34 paginiProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- Subiecte Teorie SAMDocument9 paginiSubiecte Teorie SAMMihaela EnacheÎncă nu există evaluări

- Microcontrollere Curs 2016 Corneliu BurileanuDocument91 paginiMicrocontrollere Curs 2016 Corneliu BurileanuFeta MirayÎncă nu există evaluări

- Input Output Rom MoodleDocument15 paginiInput Output Rom MoodleMatei CatalinÎncă nu există evaluări

- Ion Marin Sadoveanu-Taurul Marii 1.0 10Document104 paginiIon Marin Sadoveanu-Taurul Marii 1.0 10AndreeaÎncă nu există evaluări

- D Hawkins - Nivelurile-ConstiinteiDocument18 paginiD Hawkins - Nivelurile-ConstiinteiVictoria-Marinela Berza100% (1)

- Stephen Hawking - Scurta Istorie A TimpuluiDocument127 paginiStephen Hawking - Scurta Istorie A Timpuluireaperq100% (1)

- Stephen Hawking - Scurta Istorie A TimpuluiDocument127 paginiStephen Hawking - Scurta Istorie A Timpuluireaperq100% (1)

- Stephen Hawking - Scurta Istorie A TimpuluiDocument127 paginiStephen Hawking - Scurta Istorie A Timpuluireaperq100% (1)

- Arta Compromisului - Ileana VulpescuDocument158 paginiArta Compromisului - Ileana Vulpescugiurca_eugen100% (22)

- Mihail Sadoveanu - Creanga de Aur 05 @Document105 paginiMihail Sadoveanu - Creanga de Aur 05 @criflooÎncă nu există evaluări

- Floarea Nicola-Sadoveanu Vocatia Sacrului 07Document63 paginiFloarea Nicola-Sadoveanu Vocatia Sacrului 07mosubadeaÎncă nu există evaluări

- Rezumat BaltagulDocument3 paginiRezumat BaltagulFloRy FlrÎncă nu există evaluări

- Rezumat BaltagulDocument3 paginiRezumat BaltagulFloRy FlrÎncă nu există evaluări

- Scala Acceptarii de Sine (1) BergerDocument4 paginiScala Acceptarii de Sine (1) BergermosubadeaÎncă nu există evaluări

- Sadoveanu Mihail Moara Cu NorocDocument4 paginiSadoveanu Mihail Moara Cu NorocElisa StanÎncă nu există evaluări

- Mihail Sadoveanu - Prezentare GeneralaDocument2 paginiMihail Sadoveanu - Prezentare GeneralaMihaela Barbulescu100% (3)

- Jules Verne - Copiii Capitanului GrantDocument384 paginiJules Verne - Copiii Capitanului GrantMagistralisÎncă nu există evaluări

- Seth Godin - Toti Suntem Ciudati (v1.0)Document82 paginiSeth Godin - Toti Suntem Ciudati (v1.0)mosubadea100% (1)

- Steven Hawking - Visul Lui Einstein Si Alte EseuriDocument178 paginiSteven Hawking - Visul Lui Einstein Si Alte Eseuribcfdf100% (7)

- Swarthout, Glendon - Binecuvantati Animalele Si CopiiiDocument88 paginiSwarthout, Glendon - Binecuvantati Animalele Si CopiiimosubadeaÎncă nu există evaluări

- Stephen Hawking Leonard Mlodinow Marele Plan v1 0Document162 paginiStephen Hawking Leonard Mlodinow Marele Plan v1 0Iacob BogdanÎncă nu există evaluări

- Augusto Cury Parinti Straluciti Profesori Fascinanti 1 PDFDocument75 paginiAugusto Cury Parinti Straluciti Profesori Fascinanti 1 PDFEv Evolet100% (6)

- Stephen W. Hawking - Scurta Istorie A Timpului PDFDocument226 paginiStephen W. Hawking - Scurta Istorie A Timpului PDFkira4321100% (3)

- Stephen Hawking - Scurta Istorie A TimpuluiDocument127 paginiStephen Hawking - Scurta Istorie A Timpuluireaperq100% (1)

- Stephen HawkingDocument2 paginiStephen HawkingmosubadeaÎncă nu există evaluări

- Stephen Hawking - Scurta Istorie A TimpuluiDocument127 paginiStephen Hawking - Scurta Istorie A Timpuluireaperq100% (1)

- Scala Acceptarii de Sine (1) BergerDocument4 paginiScala Acceptarii de Sine (1) BergermosubadeaÎncă nu există evaluări

- GHID Pomi FructiferiDocument16 paginiGHID Pomi Fructiferiviosmenu100% (1)

- Strugurii NegriDocument1 paginăStrugurii NegrimosubadeaÎncă nu există evaluări

- Baltagul de Mihail SadoveanuDocument5 paginiBaltagul de Mihail SadoveanuPatrick Johnston100% (1)

- Alan Pease - Limbajul VorbiriiDocument91 paginiAlan Pease - Limbajul Vorbiriiantipsihotica83% (6)

- Nicolae Cepoiu Pomicultura AplicataDocument211 paginiNicolae Cepoiu Pomicultura Aplicatatibisor_28100% (1)

- PARADocument1 paginăPARAmosubadeaÎncă nu există evaluări