Documente Academic

Documente Profesional

Documente Cultură

Sumator 4 Biti

Încărcat de

Marius MihaiTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Sumator 4 Biti

Încărcat de

Marius MihaiDrepturi de autor:

Formate disponibile

UNIVERSITATEA OVIDIUS CONSTANA

FACULTATEA DE FIZIC, CHIMIE, ELECTRONIC I TEHNOLOGIA PETROLULUI SECIA ELECTRONIC APLICAT

PROIECT CIRCUITE INTEGRATE DIGITALE SUMATOR 4 BII

STUDENT: SCOREA RADU AN: III

1. Consideraii teoretice

Principalul bloc care intr in alctuirea calculatoarelor numerice i sistemelor cu microprocesoare o constituie unitatea de calcul aritmetic i logic(ALU), cu care se efectueaz diferitele operaii aritmetice i logice n calculator. Operaia fundamental efectuat de calculatoare i sistemele cu microprocesoare este adunarea. Operaia de scdere se reduce la adunarea primului termen (al desczutului) cu complementul (n binar) al celui de-al doilea termen (al scztorului). nmulirea se face prin adunri succesive, iar mprirea prin scderi succesive. Astfel, blocul care efectuueaz adunarea n sistemele numerice de calcul, sumatorul, reprezint unul din blocurile cele mai importante ale ALU. Semisumatorul este un circuit care efectueaz adunarea (n binar) S prin intermediul unei pori XOR(SAU-EXCLUSIV), precum i transportul T- prin folosirea unei pori AND(fig.1.). Regula transportului (la un rang superior) pentru adunare este urmtoarea: dac unul din numerele adunate conine un 1, numrtorul produce suma S=1 i nu d nimic la transport; dac ambele numere (de un bit fiecare) conin 1 sumatorul produce echivalentul binar al lui 2, format din suma 0 i transportul 1. Tabelul de adevr al circuitului este tabelul 1.

a

S ( a b) T

b

T a b

Fig.1. Semisumatorul-schema logic Tabel 1. a 0 0 1 1 b 0 1 0 1 S 0 1 1 0 T 0 0 0 1

Prin combinarea a dou semisumatoare se obine sumatorul propriu-zis care asigur adunarea a dou numere n binar innd seama i de transportul anterior. Astfel, la efectuarea adunrii n binar a numerelor : ai+1aiai-1..+ bi+1bibi-1 Si+1SiSi-1. la poziia i trebuie s fie efectuat operaia: ai + bi + Ti-1=TiSi (2.) n care Ti-1 este transportul provenit din adunarea de la poziia i-1, iar Ti este transportul generat la rangul i ctre rangul superior. n fig2.a. i b. este prezentat schema logic i simbolul sumatorului de 1 bit,avnd la ieire urmatoarele ecuaii logice: (1.)

Si=(ai + bi) + Ti-1

(3.)

Ti=aibi- Ti-1( ai + bi)

( 4. )

Ti-1 a b Si

a b Ti-1

Ti

Si +

Ti

a.Simbol b.Schema logic

Fig.2. Sumatorul de 1 bit

Un sumator multibit rezult prin aranjarea n paralel a unui numr de sumatoare complete de un bit (vezi fig.3.). Tot aici sunt configurate i cele trei registre care permit adunarea n binar, cu exemplificarea adunrii numerelor 21+7 exprimate n binar:

1 0 1

0 1 0 0 1 1 1 1 0

1 1 0

Se observ c rezult 11100, adic echivalentul n binar al numrului 28.

Registrul A

1

Registrul B

0 0

1 1

0 1

1 1

21 7

+ T

Registrul S

+ 0

+ 1

+ 1 1 0

+ 1 0 28

0 1

Fig.3.Schema unui sumator multibit

2. Mod de funcionare

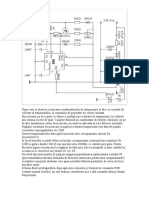

Sumatorul de 4 bii este format din 4 sumatoare de un bit legate n paralel. Astfel, primul sumator de 1 bit are intrrile A1 i B1, al doilea are intrrile A2 i B2, al treilea are intrrile A3 i B3 iar al patrulea are intrrile A4 i B4. Ieirile sunt urmtoarele: S1, S2, S3,S4 i T. Adunarea se face ntre 2 numere de 3 bii astfel: A=A1A2A3A4 i B=B1B2B3B4, rezultatul adunrii fiind un numr de 5 bii: S=TS1S2S3S4. n figura urmtoare avem schema logic a sumatorului de 4 bii realizat n Tina for Windows, iar n tabelul 2 avem cteva rezultate ale adunrii ntre numere de 4 bii.

A1 0 0 0 0 0 0 0 0 ...

A2 0 0 0 0 0 0 0 0 ...

A3 0 0 0 0 0 0 0 0 ...

A4 0 0 0 0 0 0 0 0 ...

B1 0 0 0 0 0 0 0 0 ...

B2 0 0 0 0 1 1 1 1 ...

B3 0 0 1 1 0 0 1 1 ...

B4 0 1 0 1 0 1 0 1 ...

T 0 0 0 0 0 0 0 0 ...

S1 0 0 0 0 0 0 0 0 ...

S2 0 0 0 0 1 1 1 1 ...

S3 0 0 1 1 0 0 1 1 ...

S4 0 1 0 1 0 1 0 1 ...

3. Simularea sumatorului de 4 bii

S-a realizat schema unui sumator de 4 bii in programul Tina for Windows folosind 4 sumatoare de 1 bit (fiecare sumator de 1 bit fiind compus din 2 semisumatoare). Schema se regaseste mai jos.

S-au aplicat switch-uri High-Low corespunztoare fiecrei intrri (A1, A2, A3,A4, B1, B2, B3,B4) pentru a introduce bitul necesar, atunci cnd este setat pe High, intrarea ia valoarea 1, dac este setat pe Low intrarea ia valoarea 0. Ieirile sunt determinate de 5 Voltage Pin: T, S1, S2,S3 i S4. Dup ce se introduc numerele pentru adunare (cu ajutorul switch-urilor), se selecteaza Digital Timing Analysis din meniul Analysis i apoi se d click pe OK. Exemplu: valoarea primului numr: A1A2A3A4=1011 valoarea celui de-al doilea numr: B1B2B3B4=1111

Rezultatul analizei este urmtorul:

i se citete astfel: TS1S2S3S4, n cazul adunrii din exemplu, rezultatul este 10011.

4. Bibliografie

1. Caiet de lucrari practice - Circuite Integrate Digitale, Viorel Ionescu, Universitatea Ovidius, Constanta, 2008.

S-ar putea să vă placă și

- Algebra BooleanaDocument3 paginiAlgebra BooleanaAlexei Soloviov67% (3)

- C10 Numaratoare AsincroneDocument9 paginiC10 Numaratoare AsincroneIonut NedeleaÎncă nu există evaluări

- CE 2 Refererat1Document7 paginiCE 2 Refererat1Carmen Mihaela100% (1)

- Tema 6 CodificatoareDocument5 paginiTema 6 CodificatoarePopescu CristinaÎncă nu există evaluări

- OscilatorDocument10 paginiOscilatorkareshi55Încă nu există evaluări

- Porti LogiceDocument4 paginiPorti LogiceAlexei Soloviov100% (1)

- Scia AlbastruDocument203 paginiScia AlbastruFlorina MarcuÎncă nu există evaluări

- Curs Electronica DigitalaDocument34 paginiCurs Electronica DigitalaIonut Valentin100% (1)

- PseudocodDocument8 paginiPseudocodionutmfÎncă nu există evaluări

- Grila ED Baza 2k19-1Document20 paginiGrila ED Baza 2k19-1Alecz Alex0% (1)

- Registri de DeplasareDocument17 paginiRegistri de DeplasareBogdanAndreiÎncă nu există evaluări

- Multiplexoare DemultiplexoareDocument4 paginiMultiplexoare DemultiplexoareSilvia PicicurovÎncă nu există evaluări

- Circuite ElectroniceDocument7 paginiCircuite ElectroniceMonica Cocut100% (1)

- KARNAUGH-Probleme RezolvateDocument28 paginiKARNAUGH-Probleme RezolvateAlexandra ZapucÎncă nu există evaluări

- Modelarea Unui Sistem de Ordin II RLCDocument6 paginiModelarea Unui Sistem de Ordin II RLCGrindean OvidiuÎncă nu există evaluări

- Transformata ZDocument23 paginiTransformata ZLeulinaripatÎncă nu există evaluări

- Sda PDFDocument157 paginiSda PDFDeaconu AdrianÎncă nu există evaluări

- 8-Operatii Si Porti LogiceDocument3 pagini8-Operatii Si Porti LogicealintgÎncă nu există evaluări

- MicroprocesorulDocument33 paginiMicroprocesorulRaul LazarÎncă nu există evaluări

- Grila Model MM 2k17Document20 paginiGrila Model MM 2k17viorel stanÎncă nu există evaluări

- 4 - Cap4 - Metode de Rezolvare A Circuitelor ElectriceDocument22 pagini4 - Cap4 - Metode de Rezolvare A Circuitelor ElectricePeTru Mocan100% (11)

- Semnale PeriodiceDocument16 paginiSemnale PeriodiceAlexandra PopescuÎncă nu există evaluări

- Curs9. Reprezentarea InformatiilorDocument45 paginiCurs9. Reprezentarea InformatiilorVasilisa OlgaÎncă nu există evaluări

- Codificatoare - DecodificatoareDocument7 paginiCodificatoare - DecodificatoareMarcu Andreea50% (2)

- PIDDocument9 paginiPIDpredescudarieÎncă nu există evaluări

- Registre de MemorieDocument6 paginiRegistre de MemorieAndrei BaciuÎncă nu există evaluări

- Grila Model MM 2k16Document15 paginiGrila Model MM 2k16Denisa100% (1)

- Proiect DCE Amplificator AFDocument21 paginiProiect DCE Amplificator AFMihaela AntonÎncă nu există evaluări

- Magistrala I2CDocument9 paginiMagistrala I2CHamat AfinÎncă nu există evaluări

- NumaratoareDocument24 paginiNumaratoareadrian sofeiÎncă nu există evaluări

- Elemente Pasive de CircuitDocument61 paginiElemente Pasive de CircuitElena NitaÎncă nu există evaluări

- Grila RezolvataDocument14 paginiGrila RezolvataIlie Iulian100% (2)

- Generator de Semnal TriunghiularDocument3 paginiGenerator de Semnal Triunghiulartheosoft32Încă nu există evaluări

- Intrebari Si Raspunsuri Sisteme de OperareDocument4 paginiIntrebari Si Raspunsuri Sisteme de OperareRăzvan CaprăÎncă nu există evaluări

- AC NumaratoareDocument9 paginiAC NumaratoareRaluca ComanescuÎncă nu există evaluări

- Circuite Integrate AnalogiceDocument94 paginiCircuite Integrate AnalogiceClaudiuM86Încă nu există evaluări

- Probleme PMD ExamenDocument25 paginiProbleme PMD ExamenVasileGrosuÎncă nu există evaluări

- Grile MM 2014 RezolvateDocument16 paginiGrile MM 2014 RezolvateIlie IulianÎncă nu există evaluări

- Proiect Cid Numarator AsincronDocument13 paginiProiect Cid Numarator AsincronStanca RaduÎncă nu există evaluări

- Laborator 3. Functia de Transfer Schema Bloc Raspunsul SistemelorDocument8 paginiLaborator 3. Functia de Transfer Schema Bloc Raspunsul SistemelorDariusScorobeteÎncă nu există evaluări

- Proiect MicrocontrollereDocument18 paginiProiect MicrocontrollereAlex MaziluÎncă nu există evaluări

- PMD ExamenDocument31 paginiPMD ExamenDenisa OniceanuÎncă nu există evaluări

- Cap7 Automate Programabile PLC SiemensDocument30 paginiCap7 Automate Programabile PLC SiemensNicola AndreiÎncă nu există evaluări

- Matlab - ProblemeDocument13 paginiMatlab - Problememiss_ade_17100% (3)

- Proiect - CN CeasDocument34 paginiProiect - CN CeasAna Maria100% (2)

- CID BibliografieDocument54 paginiCID Bibliografiefatigue_deea4322Încă nu există evaluări

- Are Electron Ice 1cu DeseneDocument32 paginiAre Electron Ice 1cu DeseneMunteanu AncaÎncă nu există evaluări

- Circuite Numerice - LaboratorDocument6 paginiCircuite Numerice - LaboratortataraseanuÎncă nu există evaluări

- Sumator ElimentarDocument7 paginiSumator ElimentarGuriuc CristinaÎncă nu există evaluări

- Reprezentarea Numerelor Si Operatii Aritmetice in Sisteme de CalculDocument14 paginiReprezentarea Numerelor Si Operatii Aritmetice in Sisteme de CalculDaniel PîrvanÎncă nu există evaluări

- Curs 1Document20 paginiCurs 1Mihai-Felician ZimaÎncă nu există evaluări

- Lab 4 La CIDDocument4 paginiLab 4 La CIDAur ItarÎncă nu există evaluări

- Lab 4 RCDocument4 paginiLab 4 RCDen's VlogsÎncă nu există evaluări

- SumatorDocument9 paginiSumatorDorin VÎncă nu există evaluări

- Aplicații RezolvateDocument12 paginiAplicații Rezolvategabriel eugen staminÎncă nu există evaluări

- A02 - Reprezentarea Informatiei in CalculatorDocument11 paginiA02 - Reprezentarea Informatiei in CalculatorpetrachelupuÎncă nu există evaluări

- Lab1 2Document15 paginiLab1 2mituss1Încă nu există evaluări

- Cap3 PLDocument18 paginiCap3 PLEmil KasaÎncă nu există evaluări

- Cursuri ConstantinescuDocument139 paginiCursuri ConstantinescuStefanescu MirceaÎncă nu există evaluări

- Prezentare Orasul Viena Presentation of Vienna CityDocument16 paginiPrezentare Orasul Viena Presentation of Vienna CityMarius MihaiÎncă nu există evaluări

- Setari Orange Internet Wap UnlimitedDocument2 paginiSetari Orange Internet Wap UnlimitedMarius MihaiÎncă nu există evaluări

- TemporizatorDocument2 paginiTemporizatorMarius MihaiÎncă nu există evaluări

- Prezentare Orasul Viena, Presentation of Vienna CityDocument16 paginiPrezentare Orasul Viena, Presentation of Vienna CityMarius MihaiÎncă nu există evaluări

- Cerinte MariusDocument1 paginăCerinte MariusMarius MihaiÎncă nu există evaluări

- Prezentare Orasul Viena, Presentation of Vienna CityDocument16 paginiPrezentare Orasul Viena, Presentation of Vienna CityMarius MihaiÎncă nu există evaluări

- Proiect CID Mihai MariusDocument7 paginiProiect CID Mihai MariusMarius MihaiÎncă nu există evaluări