Documente Academic

Documente Profesional

Documente Cultură

Mux Dmux Cmos

Încărcat de

Tdr DragosDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Mux Dmux Cmos

Încărcat de

Tdr DragosDrepturi de autor:

Formate disponibile

STRUCTURI COMBINAIONALE CU

MULTIPLEXOARE I DEMULTIPLEXOARE

1. Scopul lucrrii

Studiul structurilor numerice fundamentale realizate cu circuite de

multiplexare/demultiplexare n tehnologie CMOS i nsuirea metodelor de

analiz i sintez a acestor structuri.

2. Apara! "!c!#ar!

- panou logic

- surs de alimentare reglabil

- oltmetru electronic !sau tip M"#O-$%&

- cordoane de legtur

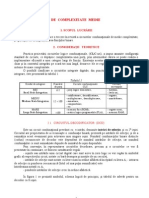

$. Co"#i%!ra&ii !or!ic!

'unc(iile binare pot fi implementate cu a)utorul unor structuri de

multiplexare/demultiplexare!decodificare&* fr a mai fi necesar minimizarea lor.

D!co%i'icaorul !care se noteaz prescurtat +C+& este un circuit integrat

pe scar medie* care identific un cod de intrare prin actiarea unei singure linii de

ieire. +ac circuitul are n ariabile binare de intrare* atunci numrul liniilor de

ieire este

,

n

. 'igura $.- arat structura circuitului pentru n . ,.

/

0

/

- ,

/ /

$

"

1

" 1

0 0

0 -

- 0

- -

0 - , $

0 - - -

- 0 - -

- - 0 -

- - - 0

0 - , $

,

-

,

0

"

1

+C+

/

0

/

- ,

/ /

$

'ig. $.- Structura, tabelul de adevr i reprezentarea decodificatorului pentru n=2

D!(ulipl!)orul !+M23& este un circuit construit pe structura

decodificatorului* care permite transmiterea datelor de pe o singur cale de intrare

pe una din cele

,

n

ci de ieire. Selec(ia liniilor de ieire se face prin aplicarea

unui cod binar pe n linii de intrare* care dein acum intrri de selec(ie. Structura

demultiplexorului pentru n . , este dat n figura $.,.

Mulipl!)orul !M23& realizeaz func(ia iners demultiplexorului* adic

permite transmiterea datelor de la una din cele

,

n

ci de intrare la o singur cale

de ieire. Selec(ia unei anumite intrri de date se face prin aplicarea unui cod binar

pe n linii de intrare* linii care sunt intrrile de selec(ie. Structura multiplexorului

pentru n . , este dat n figura $.$.

-

"

1

4

56"175

prin conectarea la 0 permite

accesul datelor de pe intrare

!

&

.

/

0

4

.

/

-

4

.

/

$

4

.

/

,

4

0 - , $

,

-

,

0

"

1

+M23

4

56"175

'ig. $., Structura i reprezentarea demultiplexorului pentru n=2

"

1

0 - , $

,

-

,

0

"

1

M23

5

4

-

4

$

4

,

4

0

8

8

4

0

4

$

4

,

4

-

5

8 8

'ig. $.$ Structura i reprezentarea multiplexorului pentru n=2

"ceste structuri combina(ionale MS4 implementeaz to(i termenii produs

fundamentali ai unei func(ii cu numr de ariabile mai mic sau egal cu numrul de

intrri de selec(ie n. +in acest moti* implementarea func(iilor binare nu necesit

opera(ii de minimizare* ci numai alegerea corect a conexiunilor. +ac numrul de

ariabile ale func(iei este mai mic sau egal cu numrul de intrri de selec(ie n* atunci

implementarea se face direct* iar n caz contrar mai sunt necesare o serie de

transformri algebrice pentru a gsi o alt structur adi(ional format de obicei din

por(i* care s completeze lipsa intrrilor de selec(ie de la M23 sau +M23.

E)!(plu* S se implementeze cu demultiplexor i apoi cu multiplexor

urmtoarea func(ie binar9

f P P P P P = + + + +

0 - , : ;

.

/entru implementarea cu +M23 ne intereseaz termenii P

i

* deci scriem

func(ia sub forma f P P P P P =

0 - , : ;

"

1

4

,

-

,

0

+M23

,

,

C

0 - , $ < % : ;

5

f

"

1 ,

-

,

0

,

,

C

0 - , $ < % : ;

5 M23

8

f

-

'ig. $.< Implementarea funciei cu demultiplexor i cu multiplexor

+. Mo%ul %! lucru

,

DAC, PANOUL LO-IC NU ESTE PRE.,/UT CU SURS, DE

ALIMENTARE DE LA REEA* atunci se alimenteaz cu o tensiune de cel mult

=-%# de la o surs de tensiune reglabil. ATEN IE LA RESPECTAREA

POLARIT , II I LA .ALOAREA INI IAL , A TENSIUNII0 .aloar!a li(i

a1#olu de catalog este de =->#. +epirea alorii limit absolute a distruge cu o

mare probabilitate circuitele integrate?

Circuitele integrate pe scar medie !MS4& au de)a o complexitate mai mare i

utilizarea lor la implementarea unor scheme electrice nu se mai poate face fr

consultarea foii de catalog.

/anoul logic con(ine trei circuite integrate cu func(ii de

multiplexor/demultiplexor realizate n tehnologie CMOS9 circuitul MMC +231 !dac

este de fabrica(ie rom@neasc* sau pur i simplu +231* precedat de alte caractere* dac

este fabricat de alt firm& A care este un multiplexor/demultiplexor cu > ci de date

!deci cu $ intrri de selec(ie&* circuitul MMC +245 A care este un

multiplexor/demultiplexor cu -: ci de date i circuitul MMC +265 A care con(ine

dou multiplexoare/demultiplexoare cu c@te > ci de date. 5ste posibil ca unele panouri

logice s nu con(in circuitul integrat MMC +265. Bn aceast situa(ie monta)ul

experimental care implic folosirea acestui circuit integrat nu se mai face.

'oile de catalog furnizeaz informa(ia complet pentru utilizarea corect a

acestor circuite integrate. Chiar dac circuitele sunt fabricate de alt productor* ele

trebuie s respecte standardul familiei logice CMOS #!ria +222. 'oile de catalog care

con(in numai informa(iile strict necesare pentru utilizarea celor $ circuite integrate sunt

prezentate n paginile urmtoare. Bn cazul structurilor combina(ionale* aceste informa(ii

strict necesare se refer la configura(ia pinilor i la tabelele de ader.

Obserm de la nceput c structurile din foile de catalog difer de cele

prezentate n paragraful $. 'unc(iile de multiplexare/demultiplexare au fost prezentate

ca func(ii logice implementate cu structuri CC7* iar acum aem de-a face cu structuri

analogice de multiplexare/demultiplexare. "sta nseamn c datele care trec prin aceste

circuite integrate pot fi i semnale analogice !semnale sinusoidale* semnale audio etc.&

i nu conteaz nici sensul de transmisie al semnalelor* deci circuitele pot fi conectate fie

ca multiplexoare* fie ca demultiplexoare. /inul 56"175 din descrierea teoretic de

mai sus se numete aici 46D414C !deci ac(iunea lui este contrar& i este acti pe -

logic* a@nd rolul de a bloca accesul datelor la ieire. 5l trebuie conectat la mas !0

logic&* dup cum rezult din tabelele de ader. O alt deosebire important const n

notarea ariabilelor aplicate pe intrrile de selec(ie. 7a sinteza structurilor

combina(ionale cu por(i logice* sau la prezentarea teoretic de mai sus* s-a notat cu "

ariabila mai semnificati* iar cea mai pu(in semnificati cu 1* C sau +* func(ie de

numrul total de ariabile. Conen(ia adoptat la circuitele CC7 s-a pstrat i aici9 C

sau + este intrarea de selec(ie mai semnificati* iar " este intrarea de selec(ie cea mai

pu(in semnificati. Bn fond este orba de o simpl conen(ie de care trebuie ns s

(inem seam pentru folosirea corect a circuitelor. 4at de ce este obligatorie

consultarea foii de catalog atunci c@nd proiectm dierse structuri folosind circuite

integrate numerice?

$

<

%

:

;

>

+.1. Se consider func(ia binar definit de tabelul de ader din figura <.-. Se

implementeaz folosind circuitul integrat MMC +231 ca demultiplexor cu > ci de

ieire i se erific func(ionarea circuitului ob(inut folosind tabelul de ader. Bn acest

scop se folosete configura(ia pinilor dat n foaia de catalog a circuitului integrat.

/oarta E4-62 cu < intrri poate fi nlocuit de structura cu $ por(i E4-62 cu c@te $

intrri dat n figur.

C 1 " f

0 0 0

0 0 -

0 - 0

0 - -

- 0 0

- 0 -

- - 0

- - -

-

-

0

-

-

0

0

0

"

1 MMC <0%-

C

0 - , $ < % : ;

f

C

1

"

46D

46/O2C

'ig. <.- Implementarea unei funcii binare cu circuitul MMC 4!"

+.2. 2n )uriu format din < persoane decide asupra reuitei unui concurent prin

ma)oritate de oturi. Se implementeaz func(ia f folosind circuitul integrat MMC +245

ca multiplexor cu -: ci de intrare. Se erific func(ionarea circuitului folosind tabelul

de ader din figura <.,.

+ C 1 " f

0 0 0 0

0 0 0 -

0 0 - 0

0 0 - -

0 - 0 0

0 - 0 -

0 - - 0

0 - - -

- 0 0 0

- 0 0 -

- 0 - 0

- 0 - -

- - 0 0

- - 0 -

- - - 0

- - - -

0

-

0

0

0

-

-

0

0

0

0

0

0

0

-

-

"

1

MMC <0:;

C C

1

"

+ +

f

8

4

0

4

-

4

,

4

$

4

<

4

%

4

:

4

;

4

>

4

F

4

-0

4

--

4

-,

4

-$

4

-<

4

-%

-

0

46D

'ig. <., Implementarea funciei de vot ma#oritar cu circuitul MMC 4$%

+.$. Se repet punctul <., folosind circuitul integrat MMC +231 ca

demultiplexor i se erific func(ionarea circuitului ob(inut folosind tabelul de ader

dat n figura <.,. Metoda de sintez a schemei logice i ecua(iile rezultate sunt

prezentate la punctul %.-* iar implementarea func(iei cu acest circuit este dat n figura

<.$. +atorit faptului c func(ia are < ariabile de intrare* iar circuitul folosit are numai

$ intrri de selec(ie* cea de-a patra ariabil nu se aplic pe intrrile de selec(ie* ci ntr-o

logic combina(ional separat* implementat aici cu $ por(i E4-62. "plicarea

ariabilelor pe aceste intrri este arbitrar* exist@nd mai multe solu(ii posibile. Circuitul

integrat MMC <0%- este folosit i aici ca demultiplexor cu 0 logic pe intrare. S se

implementeze func(ia f* folosind circuitul MMC <0%- ca demultiplexor cu - logic pe

intrarea de date. S se implementeze aceeai func(ie* folosind acelai circuit ca

multiplexor cu > ci de intrare* conform metodei descrise n problema %.,.

F

"

1 MMC <0%-

0 - , $ < % : ;

C

1

C

+

f

"

46D

46/O2C

'ig. <.$ Implementarea funciei de vot ma#oritar cu circuitul MMC 4!" i pori

+.+. 2na dintre aplica(iile func(iilor de multiplexare/demultiplexare este i

conersia din format serie n format paralel* sau iners* a datelor. "ceast proprietate

poate fi urmrit folosind circuitul din figura <.<. Mai mult dec@t at@t* circuitul

demonstreaz c por(ile de transmisie din interiorul acestor structuri permit

transmiterea semnalelor analogice* iar transmiterea acestor semnale este bidirec(ional

!nu conteaz care este intrarea sau ieirea din circuit* ele pot fi oric@nd interschimbate

ntre ele&. Se introduce pe intrarea 46/O2C un semnal sinusoidal fr component

continu* de amplitudine mai mic de %#. "cest semnal este regsit* practic fr

atenuare* la ieirea O2C/46 a circuitului* pentru orice combina(ie a ariabilelor de

intrare "* 1 i C. /entru o anumit combina(ie binar a acestor intrri* semnalul

introdus se a regsi i la una dintre ieirile/intrrile corespunztoare ale

+M23/M23-ului* numerotate de la 0 la ;. Se aplic semnalul i pe intrarea O2C/46 a

circuitului* fiind regsit la ieirea 46/O2C. Semnalul sinusoidal !sau de orice alt

form& este generat cu a)utorul unui generator de semnal* iar izualizarea lui la intrarea

i la ieirea din circuit se face cu a)utorul unui osciloscop cu , canale. Circuitul integrat

MMC +265 este alimentat cu tensiunea de %#* deci excursia semnalului analogic de

intrare trebuie s fie cuprins ntre A%*%# i =%*%#* depirea acestor limite a@nd ca

efect deschiderea diodelor din re(eaua de protec(ie a intrrii i posibilitatea distrugerii

lor prin supracurent !maxim -0m"&.

-/, x MMC <0F;

" 1

0

-

,

$

<

%

:

;

C

1 C "

+M23

46/O2C

" 1

0

-

,

$

<

%

:

;

C

M23 O2C/46

-/, x MMC <0F;

46D

'ig. <.< &recerea unui 'emnal analo(ic printr)un *M+, i un M+, analo(ic

3. Pro1l!(! r!7ol8a!

-0

3.1. S se fac sinteza func(iei reprezentat prin tabelul de ader din figura

<., cu a)utorul unui demultiplexor cu > ci de ieire.

Rezolvare:

'unc(ia poate fi scris n forma canonic dis)uncti sub forma9

f P P P P P = + + + +

; -- -$ -< -%

. Obserm ns c numrul de ariabile ale func(iei este

mai mare dec@t numrul intrrilor de selec(ie a demultiplexorului. +in acest moti om

face o serie de transformri algebrice care s pun n eiden( mintermenii unei func(ii

de $ ariabile* mintermeni care sunt disponibili la ieirile demultiplexorului. Cea de-a

patra ariabil a fi introdus ntr-o logic combina(ional suplimentar* realizat de

obicei cu por(i logice.

f P P P P P *C-. *C-. *C-. *C-. *C-. = + + + + = + + + + =

; -- -$ -< -%

( ) ( ) = + + + + = + + + + = . *C- *C- *C- *C- .*C- . P P P P . P

$ % : ; ;

G G G G G

( ) = + + + = + = . P P P P . P P P P . P P P P

$ % : ; $ % : ; $ % : ;

G G G G G G G G G G G G

5xpresia algebric ob(inut permite implementarea func(iei f* conform schemei

din figura <.$. 5ste eident c oricare alte $ ariabile puteau fi aplicate pe intrrile de

selec(ie ale demultiplexorului* cu condi(ia refacerii calculelor de mai sus.

3.2. S se proiecteze un conertor de cod din cod binar n cod HraI pentru

numere reprezentate pe $ bi(i* folosind9

a& un decodificator cu $ intrri de selec(ie.

b& multiplexoare cu c@te , intrri de selec(ie.

c& un numr minim de circuite.

Rezolvare:

+ou reprezentri succesie n cod HraI difer printr-un singur bit. Cabelul din

figura %.- indic coresponden(a cod binar - cod HraI* iar schema logic din figura %.-

prezint solu(ia de la punctul a. /entru sinteza schemelor logice n probleme* propunem

ca ariabila " s fie aplicat pe intrarea de selec(ie cea mai semnificati.

" 1 C

0 0 0

0 0 -

0 - 0

0 - -

- 0 0

- 0 -

- - 0

- - -

" 1 C

0 0 0

0 0 -

0 - -

0 - 0

- - 0

- - -

- 0 -

- 0 0

H H H

"

1 ,

-

,

0

+C+

,

,

C

0 - , $ < % : ;

1 C

H H

"

H

'ig. %.- Convertor de cod binar ) /ra0 cu decodificator i pori

b& Se pot folosi multiplexoare cu c@te , intrri de selec(ie prin transformrile9

( ) ( ) . .-C .-C .-C .-C .- .- C .- .- C P P

/

= + + + = + + + = +

, $

G G

( ) ( ) - .-C .-C .-C .-C .- .- C .- .- C P P

/

= + + + = + + + = +

- ,

G G

( ) ( ) C .-C .-C .-C .-C P P C P P C

/

= + + + = + + +

0 , - $

G G G G

--

0 - , $

,

-

,

0

"

1

M23

5

8

-

0

"

H

0 - , $

,

-

,

0

"

1

M23

5

8

-

0

H

0 - , $

,

-

,

0

"

1

M23

5

8

-

H

1 C

C

'ig. %., Convertor de cod binar ) /ra0 cu multiplexoare

Schema logic din figura %., prezint o solu(ie a problemei. Sunt posibile i alte

solu(ii* func(ie de alegerea ariabilelor care se aplic pe intrrile de selec(ie.

c& 4mplementarea cea mai simpl este cu por(i logice. /rin minimizare cu

a)utorul diagramei #eitch-Jarnaugh rezult urmtoarele rela(ii9

. .

/

=

* - .- .- . -

/

= + = * C -C -C - C

/

= + = .

+eci implementarea cea mai simpl este cu dou por(i logice S"2-53C72S4#.

4. Pro1l!(! propu#!

4.1. S se implementeze un sumator complet de - bit folosind multiplexoare cu

< ci de intrare. S se implementeze acelai circuit folosind un decodificator cu , intrri

de selec(ie i s se compare cele dou solu(ii.

4.2. O structur numeric combina(ional are : intrri i o ieire. +ou din cele

: intrri sunt intrri de selec(ie care stabilesc modul de func(ionare al circuitului* iar

celelalte < sunt intrri de date. Cabelul din figura :.- explic func(ionarea circuitului. S

se reprezinte schema logic a circuitului folosind9

a& un multiplexor cu , intrri de selec(ie i un numr minim de por(i logice.

b& un demultiplexor cu , intrri de selec(ie i un numr minim de por(i logice

E4-62.

'

0

'

-

0 -

0 0

- 0

- -

ac(iune

K . - dac

K . - dac

K . - dac

K . - dac

" " " "

$ , - 0

este multiplu de ,

" " " "

$ , - 0

este multiplu de <

" " " "

$ , - 0

. -$

"

$

. -

" " " "

$ , - 0

'

0

'

-

C7C

K

'ig. :.- &abelul care de'crie funcionarea circuitului

4.$. S se proiecteze un demultiplexor cu $, ci de ieire* folosind numai

demultiplexoare cu > ci de ieire.

4.+. S se realizeze o extindere a capacit(ii de multiplexare de la > la -: ci*

folosind multiplexoare cu > ci de intrare i un numr minim de por(i E4-62.

-,

S-ar putea să vă placă și

- Structuri de Comutatie Multi-TreaptaDocument28 paginiStructuri de Comutatie Multi-TreaptaIulian DitaÎncă nu există evaluări

- Circuite Logice de Complexitate MedieDocument10 paginiCircuite Logice de Complexitate MediebalanoiualexandraÎncă nu există evaluări

- L01 TCI Filtre Secventiale LiniareDocument6 paginiL01 TCI Filtre Secventiale LiniareIonescu ViorelÎncă nu există evaluări

- Mux DmuxDocument10 paginiMux DmuxTdr DragosÎncă nu există evaluări

- 04 Circuite Logice CombinationaleDocument42 pagini04 Circuite Logice CombinationaleDragoș ToaderÎncă nu există evaluări

- Completare Curs Circuite LogiceDocument8 paginiCompletare Curs Circuite LogiceAlin SârbuÎncă nu există evaluări

- Circuite Logice Programabile Complexe (CPLD)Document14 paginiCircuite Logice Programabile Complexe (CPLD)RangerTalonÎncă nu există evaluări

- Electronica Si Automatizari Xi Utilizarea Circuitelor InteDocument49 paginiElectronica Si Automatizari Xi Utilizarea Circuitelor InteIordan Dan FfnÎncă nu există evaluări

- Code Convertor From Exces 3 in 8421 BCDDocument39 paginiCode Convertor From Exces 3 in 8421 BCDnokia53105800100% (1)

- Logica CombinationalaDocument100 paginiLogica CombinationalawrkahlcÎncă nu există evaluări

- Discipline Fundamentale IDDocument47 paginiDiscipline Fundamentale IDcocoronco1212Încă nu există evaluări

- Dinca Mihai SorinDocument7 paginiDinca Mihai SorinPopina AndreiÎncă nu există evaluări

- Laborator Port SerialDocument11 paginiLaborator Port SerialKen LaszloÎncă nu există evaluări

- Managementul Retelelor SDHDocument52 paginiManagementul Retelelor SDHccalin10Încă nu există evaluări

- Seminarizare Capitol CLCDocument10 paginiSeminarizare Capitol CLCAna Maria PorimeÎncă nu există evaluări

- Sistema de Comutatie AXE-10Document8 paginiSistema de Comutatie AXE-10Dan DanielÎncă nu există evaluări

- Se Da SchemaDocument14 paginiSe Da SchemaRodica Petronela GhițăÎncă nu există evaluări

- 6-Conectarea Pe Magistrala Si La Port ParalelDocument18 pagini6-Conectarea Pe Magistrala Si La Port ParalelsssssssÎncă nu există evaluări

- L1 L2 L3 (Tema) PDFDocument44 paginiL1 L2 L3 (Tema) PDFVlad ZahiuÎncă nu există evaluări

- Modelarea Sistemelor de Ecuații Liniare În Matlab - Dobrete & FilipescuDocument10 paginiModelarea Sistemelor de Ecuații Liniare În Matlab - Dobrete & FilipescuDobrete KatyÎncă nu există evaluări

- Pvlsi Examen PDFDocument49 paginiPvlsi Examen PDFAlexandruÎncă nu există evaluări

- TsarDocument42 paginiTsarRazvan MariusÎncă nu există evaluări

- Asdn 3Document11 paginiAsdn 3EuegniuÎncă nu există evaluări

- 2 Magistrale PDFDocument14 pagini2 Magistrale PDFAndrei VieruÎncă nu există evaluări

- Multiplexoare Și Demultiplexoare: Obreja George-CătălinDocument11 paginiMultiplexoare Și Demultiplexoare: Obreja George-CătălinCatalin ObrejaÎncă nu există evaluări

- RLC MatlabDocument16 paginiRLC MatlabDiana GoldÎncă nu există evaluări

- Orcad Curs1Document20 paginiOrcad Curs1Ionuț MoÎncă nu există evaluări

- CidDocument32 paginiCidSimona CroitoruÎncă nu există evaluări

- SEP - TMS320C10 - Cap13Document21 paginiSEP - TMS320C10 - Cap13Mops LightÎncă nu există evaluări

- Circuite DigitaleDocument13 paginiCircuite DigitaleAnimet TVÎncă nu există evaluări

- Referat Comutatia de CircuiteDocument6 paginiReferat Comutatia de Circuitepasat_deliaÎncă nu există evaluări

- Laborator 3: CuprinsDocument5 paginiLaborator 3: CuprinsAlexArdeleanuÎncă nu există evaluări

- Circuite IntegrateDocument22 paginiCircuite Integrateseitan_calinÎncă nu există evaluări

- Circuite Digitale Nicu PROIECTULDocument13 paginiCircuite Digitale Nicu PROIECTULAnimet TVÎncă nu există evaluări

- 2.6 Circuite Combina Ţionale: 2.6.1 Decodificatoare/demultiplexoare DecodificatorulDocument11 pagini2.6 Circuite Combina Ţionale: 2.6.1 Decodificatoare/demultiplexoare DecodificatorulRaduStefanÎncă nu există evaluări

- Algoritmi Simetrici de Criptare. Algoritmul AESDocument13 paginiAlgoritmi Simetrici de Criptare. Algoritmul AESRadulian Defta50% (2)

- Minimizarea Portilor SI NUDocument15 paginiMinimizarea Portilor SI NUgi_henry_20064237Încă nu există evaluări

- Curs 10 APDDocument28 paginiCurs 10 APDRaluca StefanÎncă nu există evaluări

- PACE SubiecteDocument5 paginiPACE SubiecteIonut CarstovÎncă nu există evaluări

- (ASC) Subiecte + RezolvariDocument23 pagini(ASC) Subiecte + RezolvariTudor BesteaÎncă nu există evaluări

- Cap7 Automate Programabile PLC SiemensDocument30 paginiCap7 Automate Programabile PLC SiemensNicola AndreiÎncă nu există evaluări

- Proiect - CN CeasDocument34 paginiProiect - CN CeasAna Maria100% (2)

- Modelare pSPICEDocument7 paginiModelare pSPICEIonuț MoÎncă nu există evaluări

- Proiectarea Sistemelor de Conducere Cu AutomateDocument12 paginiProiectarea Sistemelor de Conducere Cu Automateandreeaoana45Încă nu există evaluări

- M03 - Multiplexarea PDHDocument44 paginiM03 - Multiplexarea PDHmaryus66100% (2)

- Manual Service (Reparatii) Dacia Papuc Diesel F8Q: Scheme ElectriceDocument153 paginiManual Service (Reparatii) Dacia Papuc Diesel F8Q: Scheme Electricebogdanxp200085% (20)

- Automate FiniteDocument10 paginiAutomate FiniteAlexandru IonutÎncă nu există evaluări

- PORTICLCDocument6 paginiPORTICLCAlexandru IonutÎncă nu există evaluări

- Poarta CMOS - 4000Document10 paginiPoarta CMOS - 4000Tdr DragosÎncă nu există evaluări

- SECVLAB1Document4 paginiSECVLAB1Alexandru IonutÎncă nu există evaluări

- Comblab 1Document5 paginiComblab 1Tdr DragosÎncă nu există evaluări

- Poarta TTL StandardDocument9 paginiPoarta TTL StandardTdr DragosÎncă nu există evaluări

- Bi StabileDocument9 paginiBi StabileTdr DragosÎncă nu există evaluări

- Automate FiniteDocument10 paginiAutomate FiniteAlexandru IonutÎncă nu există evaluări

- Fitzuici ElectroDocument3 paginiFitzuici ElectroTdr DragosÎncă nu există evaluări

- IntrebariDocument2 paginiIntrebariTdr DragosÎncă nu există evaluări

- Roboti Mobili PROIECTDocument16 paginiRoboti Mobili PROIECTTdr Dragos100% (2)