0% au considerat acest document util (0 voturi)

202 vizualizări7 paginiCircuite PLL CIA

Încărcat de

Andrei MlcDrepturi de autor

© © All Rights Reserved

Respectăm cu strictețe drepturile privind conținutul. Dacă suspectați că acesta este conținutul dumneavoastră, reclamați-l aici.

Formate disponibile

Descărcați ca DOCX, PDF, TXT sau citiți online pe Scribd

0% au considerat acest document util (0 voturi)

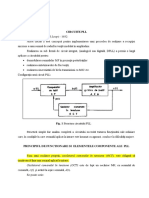

202 vizualizări7 paginiCircuite PLL CIA

Încărcat de

Andrei MlcDrepturi de autor

© © All Rights Reserved

Respectăm cu strictețe drepturile privind conținutul. Dacă suspectați că acesta este conținutul dumneavoastră, reclamați-l aici.

Formate disponibile

Descărcați ca DOCX, PDF, TXT sau citiți online pe Scribd