Documente Academic

Documente Profesional

Documente Cultură

03 Structuri Logice Cmos

Încărcat de

AndreeaTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

03 Structuri Logice Cmos

Încărcat de

AndreeaDrepturi de autor:

Formate disponibile

Sisteme cu circuite integrate digitale

Structuri logice CMOS

Prof. dr. ing. Sorin Hintea

Departamentul Bazele Electronicii

Cuprins

Structuri logice CMOS

Tehnologia CMOS

Inversorul CMOS. Mod de funcţionare şi caracterisitici

Puterea disipată

Marginea de zgomot şi fan-out-ul

Porţi logice CMOS

Poarta de transmisie, inversorul cu 3 ieşiri, multiplexorul

Bistabilul D

Familii de circuite logice CMOS

Sisteme cu circuite integrate digitale – Structuri logice CMOS 2

Tehnologia CMOS

Cea mai răspandită tehnologie de producţie a circuitelor integrate digitale VLSI

Tehnologia CMOS foloseşte perechi de tranzistoare cu canal n (nMOS) şi cu canal p

(pMOS) dispuse în randuri şi coloane

Tranzistorul nMOS este construit în substratul de tip p iar pentru dispozitivul pMOS

este creată o regiune n-well cu scopul de a acţiona ca “bulk” pentru regiunile difuzate

p+

Dimensiunile tranzistorului sunt date de dimensiunile canalului şi au devenit tot mai

mici cu fiecare decadă, permiţând implementarea unui număr tot mai mare de

tranzistoare pe un singur chip (miliarde)

Scopul studierii circuitelor CMOS: de a cunoaşte cum sunt construite şi care este

comportamentul lor, care le sunt caracteristicile şi performanţele.

met

met

poly poly

met

met

met

met

oxid oxid

Iso p+ n+ n+ Iso p+ p+ n+ Iso

n-well

substrat p-

Sisteme cu circuite integrate digitale – Structuri logice CMOS 3

Inversorul CMOS – principiul de implementare

Principiul de implementare a circuitelor CMOS

Inversorul este cel mai simplu circuit fundamental

Este realizat cu o pereche de tranzistoare: unul NMOS iar celalalt PMOS

Tranzistoarele lucrează ca douǎ comutatoare care se deschid alternativ

Un comutator comandat cu ‘0’ închide un scurtcircuit la V DD – comutator pMOS

Un comutator comandat cu ‘1’ închide un scurtcircuit la GND – comutator nMOS

VDD

‘1’

‘0’ ‘0’

‘1’

Sisteme cu circuite integrate digitale – Structuri logice CMOS 4

Logica de comutaţie

In SCID, tranzistorul MOS este echivalent cu un comutator comandat

Pentru a implementa aceste comutatoare vom folosi tranzistoare complementare

VG = GND ‘0’ conducţie

pMOS

VG = VDD ‘1’ blocat

VG = GND ‘0’ blocat

nMOS

VG = VDD ‘1’ conducţie

Sisteme cu circuite integrate digitale – Structuri logice CMOS 5

Inversorul CMOS – principiul de implementare

Inversorul – realizat din două dispozitive complementare: nMOS şi pMOS

VDD VDD VDD

Mp

a M p Mn f=a

a a 1 0 0 1 0 on off 1

Mn

1 off on 0

La fiecare tranziţie, tranzistoarele trec prin trei stări:

blocat |VGS| < |VTh| n.a. ID = 0

liniar |VGS| > |VTh| |VDS| < VOD I D VGS VTh VDS

saturat |VGS| > |VTh| |VDS| > VOD ID VGS Vth 2

2

Sisteme cu circuite integrate digitale – Structuri logice CMOS 6

Inversorul CMOS – principiul de implementare

Inversorul CMOS:

structura de bază a circuitelor CMOS

realizat din două dispozitive complementare: unul nMOS şi celalalt pMOS

Funcţionarea se bazeaza pe principiul existenţei a două căi: pull-up ( de încărcare) şi pull-down (de

descărcare).

Când tranzistorul cu canal n este în starea ON celălalt trebuie să fie în starea OFF şi invers.

Dacă intrarea este ‘0’, tranzistorul nMOS este OFF (blocat) iar cel pMOS este ON (conducţie liniară)

Dacă intrarea este ‘1’, dispozitivul nMOS este ON (conducţie liniara) iar cel pMOS este OFF (regiunea de

blocare)

La o tranziţie, tranzistoarele trec prin trei stări: VDD

VGS Vth ; I D 0

blocare:

saturaţie: VDS VGS Vth ; I D VGS Vth 2 Vin Vout

2

conducţie liniară: V

VDS VGS Vth ; I D VGS Vth DS VDS

2

Sisteme cu circuite integrate digitale – Structuri logice CMOS 7

Inversorul CMOS – principiul de functionare

Dacă intrarea este ‘0’, tranzistorul nMOS este OFF (blocat) iar cel pMOS este ON (conducţie

liniară) 6

VOUT VDD R DSp I OFF 5V 10 10 V 5V 10mV

4

Când intrarea este ‘1’, dispozitivul nMOS este ON (conducţie liniară) iar cel pMOS este OFF

(regiunea de blocare)

VOUT R DSp I OFF 10 4 10 6 V 10mV

Inversorul lucrează aşa cum este descris în tabelul de adevăr: când intrarea este ‘0’ ieşirea este

‘1’ iar dacă intrarea este ‘1’ răspunsul circuitului este ‘0’

Nivelurile logice la ieşire sunt foarte aproape de cazul ideal ( 4.990 V and 0.010 V)

Concluzie: în stările stabile nu circulă curenţi VDD VDD VDD

dinspre potentialul pozitiv al sursei spre masă

rDSp

cu excepţia unor curenţi de scurgere de valoare mică. Vout Vout

Vin Vout ‘1’ ‘0’

Vor exista însă valori mai mari de curent prin

rDSn

dispozitiv atunci când există tranziţii ale semnalului

la intrare.

Sisteme cu circuite integrate digitale – Structuri logice CMOS 8

Inversorul CMOS – descrierea funcţionarii

Vin variază de la LOW (‘0’) la HIGH (‘1’)

1 2 3 4 5 Vout

1 2 3 4 5

VDD

VDD VDD VDD VDD VDD

rDSp rDSp

IDp IDp

Vout Vout

Vout Vout Vout

‘1’ ‘0’

IDn IDn rDSn rDSn

Vthn VDD-|Vthp| VDD Vin

ID

1 2 3 4 5

VSGp=VDD VSGp > |Vthp| VSGp > |Vthp| VSGp > |Vthp|

VSGp=0

VSDp=0 VSDp ≈ GND < Vodp VSDp > Vodp VSDp ≈ VDD > Vodp Imax

VGSn = VDD

VGSn = 0 VGSn > Vthn VGSn > Vthn VGSn > Vthn

VDSn=0

VDSn ≈ VDD > Vodn VDSn > Vodn VDSn ≈ GND < Vodn

Mp – lin Mp – lin Mp – sat Mp – sat Mp – b

Mn – b Mn – sat Mn – sat Mn – lin Mn – lin

Vthn VDD-|Vthp| VDD Vin

Sisteme cu circuite integrate digitale – Structuri logice CMOS 9

Inversorul CMOS – niveluri logice

VDD VDD

IoHmax HIGH VOHmin → nivelul minim al tensiunii de

ieşire pentru starea HIGH

VoHmin ViHmin VOLmax → nivelul maxim al tensiunii de

VDD VDD

ieşire pentru starea LOW

LOW

IoLmax IOHmax → curentul de ieşire maxim

generat în starea HIGH

VoLmax ViLmax

IOLmax → curentul de ieşire maxim

Vout generat în starea LOW

‘1’ VDD

HIGH VOHmax VIHmin → nivelul minim al tensiunii de

intrare recunoscut ca HIGH

VILmax → nivelul maxim al tensiunii de

intrare recunoscut ca LOW

‘0’ VOLmax

LOW

VILmax VIHmin VDD Vin

‘0’ ‘1’

LOW HIGH

Sisteme cu circuite integrate digitale – Structuri logice CMOS 10

Inversorul CMOS – marginea de zgomot

VDD VDD iesire VDD intrare

IoHmax HIGH VOHmin

VDD - 0.1V

‘1’ - HIGH mH=VOHmin-VIHmin ‘1’ - HIGH

VIHmin

0.7∙VDD

VoHmin ViHmin

nedefinit

VDD VDD

LOW VILmax

0.3∙VDD

IoLmax

mL=VILmax-VOLmax ‘0’ - LOW

VOLmax ‘0’ - LOW

GND + 0.1V

VoLmax ViLmax GND

Vout

‘1’ VDD Marginea de zgomot → nivelul maxim de

HIGH VOHmax

zgomot acceptat la intrare astfel încât semnalul de

ieşire să nu fie afectat

mH = VOHmin – VIHmin

‘0’ VOLmax

LOW

VILmax VIHmin VDD Vin mL = VOLmax - VILmax

‘0’ ‘1’

LOW HIGH

Sisteme cu circuite integrate digitale – Structuri logice CMOS 11

Inversorul CMOS – fanout

Fiecare inversor nou conectat la ieşirea unui inversor creşte capacitatea de sarcină

cresc constantele de timp de încărcare şi descărcare, precum şi timpii de tranziţie

datorită timpilor lungi, se pot pierde niveluri logice

Fanout → parametru care specifică sarcina maximă ce poate fi comandată de o poartă logică,

fără a se pierde niveluri logice (tranziţii incomplete)

reprezintă numărul maxim de intrări care se conectează la o singură ieşire

exemplu: CMOS seria HC: Imax,in = ±1 μA , IOLmax = IOHmax = 20 μA => FO = 10

în tehnologiile CMOS VLSI, uzual se ia FO ≤ 3 – 4, pentru a nu mări sarcinile capacitive

VDD

Vout

Vin

CL

fanout

Sisteme cu circuite integrate digitale – Structuri logice CMOS 12

Inversorul CMOS – consumul de putere

Consumul de putere determină consumul de energie de la sursa de alimentare şi provoacă

încălzirea cipului în timpul funcţionării

Cunoaşterea acestui parametru este importantă pentru a calcula capacitatea sursei de

alimentare, durata de viaţă a bateriei, dimensionarea liniilor de alimentare, modul de incapsulare

şi modalitatea de răcire a capsulei

Consumul de putere are trei componente:

Pdyn – puterea dinamică disipată în urma încărcării şi descărcării capacităţii de sarcină

Pdp – puterea dinamică disipată datorită conducţiei simultane a tranzistoarelor nMOS şi

pMOS

Pstat – puterea statică disipată datorită curentului care circulă între liniile de alimentare în

regim static de funcționare (în stările stabile).

Ptot Pdyn Pdp Pstat

Sisteme cu circuite integrate digitale – Structuri logice CMOS 13

CMOS inverter – static power consumption

Puterea statică disipată

Pe durata stărilor stabile (modelele 1 şi 5) unul dintre tranzistoare este blocat şi prin

urmare nu există cale de curent închisă între VDD şi GND

ideal, inversorul nu consumă putere

In cazul real, există un curent de scurgere prin joncţiunile drenă -substrat şi sursă –

substrat care sunt polarizate invers, precum şi un curent de sub-prag care circula prin

tranzistoare

VDD 1 5

VDD VDD

VDD

rDSp

Vin Vout Vout Vout

‘1’ ‘0’

curent de fuga

rDSn

curent de subprag

Systems with Digital Integrated Circuits – CMOS Logic Structures 14

Inversorul CMOS – consumul de putere

Puterea statică disipată

Pe durata stărilor stabile (modelele 1 şi 5) unul dintre tranzistoare este blocat şi nu

se închide nici o cale de curent între VDD si GND

ideal, inversorul nu consumă putere statică

In realitate apare un curent de fugă prin joncțiunile drenă-substrat și sursă-substrat

polarizate invers, precum şi un curent de conducţie în subprag

Pstat I stat VDD ( I fuga I subprag) VDD

VDD

Vin

VDD

Vout

VDD

met

met

met

met

met

met

poly poly

oxid oxid

p+ n+ n+ p+ p+ n+

Vin Vout

curent de fuga

n- well

curent de subprag substrat p-

Sisteme cu circuite integrate digitale – Structuri logice CMOS 15

Inversorul CMOS – consumul de putere

Puterea statica– doua componente

Curentul de subprag – între drenă şi sursă

Curentul de fugă – între poartă / drenă/ sursă şi substrat

Pstat I stat VDD ( I fuga I subprag ) VDD

În procesele de dimensiune peste 180 nm, curentul de fugă era în general nesemnificativ cu

excepţia aplicaţiilor de putere foarte mică

În procesele de 90 şi 65 nm, curenţii de fugă de subprag ating valori de la 1 nA pană la 10 nA

pe tranzistor

În procesele de 45 nm, grosimea izolatorului scade până la punctul în care curentul de fugă prin

poartă devine comparabil cu valoarea curentului de subprag

Consumul de putere statică devine important când se multiplică cu milioane sau miliarde de

tranzistoare pe chip

Curentul de fugă static a devenit o ţintă de proiectare importantă în tehnologiile nanometrice:

aproape o treime din puterea totală consumată este componenta statică.

Sisteme cu circuite integrate digitale – Structuri logice CMOS 16

Inversorul CMOS – consumul de putere

Exemplul 1. Calculati puterea statică consumată de un tranzistor NMOS. Dimensiunile tranzistorului sunt W N / LN

=0.1µ /0.05µ = 2/1. Curentul de scurgere de subprag este de 10nA/μm pentru fiecare transistor. Curentul de scurgere

din grilă este de 5nA/ μm. Tensiunea de alimentare este 1.2V.

Curentul de scurgere de subprag consumat de un tranzistor

Curentul de fuga din grilă consumat de un tranzistor

Puterea statică consumată de tranzistorul NMOS este:

Sisteme cu circuite integrate digitale – Structuri logice CMOS 17

Inversorul CMOS – consumul de putere

Puterea dinamică disipată în urma încărcării şi descărcării capacităţii de sarcină

2

Pdyn f C L VDD

Vin

VDD

f – frecvenţa de comutaţie a inversorului

CL – capacitatea de sarcină

VDD - tensiunea de alimentare t

Vout

VDD

VDD VDD

t

rDSp ICL

Vout = HIGH Vout = LOW

‘1’ ‘0’ Imax

CL rDSn CL

Sisteme cu circuite integrate digitale – Structuri logice CMOS 18

Inversorul CMOS – consumul de putere

Exemplul 1. Calculaţi puterea disipată dinamică datorată incărcării / descărcării unui condensator pentru un inversor CMOS in

tehnologie de 0.25 µm, care are o capacitate parazită de sarcină de 6 fF, tensiune de alimentare de 2.5 V si frecvenţa maximă permisă

de timpul de propagare mediu al inversorului egal cu 80 ps.

Frecvenţa maximă permisă este

Puterea disipată dinamică

Sisteme cu circuite integrate digitale – Structuri logice CMOS 19

Inversorul CMOS – consumul de putere

Puterea dinamică disipată datorită conducţiei simultane a tranzistoarelor

Pe durata comutaţiei, când unul dintre tranzistoare

(modelele 2 şi 4) sau ambele (modelul 3) sunt în saturaţie,

se închide o cale de curent între VDD si GND Vout

VDD

3 t

Pdp I Dmed VDD VDD 2Vth r

12 T

1 2 3 4 5 VDD Vin

VDD VDD VDD VDD VDD ID

rDSp rDSp

IDp IDp IDmax

Vout Vout

Vout Vout Vout

‘1’ ‘0’

IDn IDn rDSn rDSn

VILmax VIHmin VDD Vin

Sisteme cu circuite integrate digitale – Structuri logice CMOS 20

Inversorul CMOS – consumul de putere

Exemplul 1. Calculati puterea dinamică datorată curentilor de scurt-circuit pentru un inversor CMOS in tehnologie de 0.25 um, care

are o capacitate parazită de sarcină de 6 fF, tensiune de alimentare de 2.5 V si frecvenţa maximă permisă de timpul de propagare

mediu al inversorului egal cu 80 ps.

Această valoare este mult mai mică decat cea datorată incărcării condensatoarelor parazite, motiv pentru care se neglijează in calcule.

Exemplul 2. Recalculati puterea dinamică datorată curentilor de scurt-circuit pentru un inversor CMOS in tehnologie de 0.25 um,

care are o capacitate parazită de sarcină de 6 fF, tensiunea de alimentare de 2.5 V si frecvenţa maximă permisă de timpul de

propagare mediu al inversorului egal cu 80 ps.

Sisteme cu circuite integrate digitale – Structuri logice CMOS 21

Porţi logice CMOS – principiu de implementare

VDD

scurtcircuit la VDD – reţea “pull-up” pMOS

reţeaua “pull-up” implementează funcţia în logica i0

complementară i1 pMOS

...

in

“pull-ul”

scurtcircuit la GND – reţea “pull-down” pMOS

f

reţeaua “pull-down” implementează funcţia în logica

directă nMOS

...

“pull-down”

“pull-up” şi “pull-down” sunt complementare

variabilele funcţiei sunt conectate la ambele reţele

pull-up – n tranzistoare

pull-down – n tranzistoare

ieşirea porţii se ia de la nodul comun al celor două reţele

porţile logice CMOS realizate astfel implementează funcţia logică negată

Sisteme cu circuite integrate digitale – Structuri logice CMOS 22

Porţi logice CMOS – principiu de implementare

Porţi logice CMOS → tranzistoarele nMOS şi pMOS sunt dispuse complementar

Tranzistorul MOS poate fi privit ca un comutator comandat

conexiune serie → funcţie ŞI → semnalul ajunge de la intrare la ieşire dacă

ambele comutatoare sunt închise

conexiune paralel → funcţie SAU → semnalul ajunge de la intrare la ieşire

dacă cel puţin unul dintre comutatoare este închis

a

a b

b

In Out In Out

Sisteme cu circuite integrate digitale – Structuri logice CMOS 23

Porţi logice CMOS – poarta ŞI-NU cu 2 intrări

VDD

Mp1 Mp2

a b f = ab

a 0 0 1 f

f 0 1 1

b 1 0 1 a Mn1

1 1 0

b Mn2

f = ‘1’ → legătură la VDD, se realizează dacă a = ‘0’ SAU b = ‘0’

2 tranzistoare pMOS în paralel

f = ‘0’ → legătură la GND, se realizează dacă a = ‘1’ ŞI b = ‘1’

2 tranzistoare nMOS în serie

Sisteme cu circuite integrate digitale – Structuri logice CMOS 24

Porti logice CMOS – poarta ŞI-NU cu 2 intrări

VDD VDD

Tranzistorul MOS – model comutator Mp1 Mp2 Mp1 Mp2

ideal

f=1 f=1

pMOS, VG = LOW → conducţie

a=0 Mn1 a=0 Mn1

pMOS, VG = HIGH → blocat

b=0 Mn2 b=1 Mn2

nMOS, VG = LOW → blocat

nMOS, VG = HIGH → conducţie

VDD VDD

Mp1 Mp2 Mp1 Mp2

a b Mp1 Mp2 Mn1 Mn2 f = ab

0 0 on on off off 1 f=1 f=0

0 1 on off off on 1 a=1 Mn1 Mn1

a=1

1 0 off on on off 1

1 1 off off on on 0 b=0 Mn2 b=1 Mn2

Sisteme cu circuite integrate digitale – Structuri logice CMOS 25

Porti logice CMOS – poarta SAU-NU cu 2 intrări

VDD

a Mp1

a b f = a+b

a 0 0 1 b Mp2

f 0 1 0

b 1 0 0 f

1 1 0

Mn1 Mn2

f = ‘1’ → legătură la VDD, se realizează dacă a = ‘1’ ŞI b = ‘1’

2 tranzistoare pMOS serie

f = ‘0’ → legătură la GND, se realizează dacă a = ‘1’ SAU b = ‘1’

2 tranzistoare nMOS paralel

Sisteme cu circuite integrate digitale – Structuri logice CMOS 26

Porti logice CMOS – poarta SAU-NU cu 2 intrări

VDD VDD

Tranzistorul MOS – model comutator

a=0 Mp1

ideal a=0 Mp1

pMOS, VG = LOW → conducţie b=0 Mp2 b=1 Mp2

f=1 f=0

pMOS, VG = HIGH → blocat

nMOS, VG = LOW → blocat Mn1 Mn2

Mn1 Mn2

nMOS, VG = HIGH → conducţie

VDD VDD

a b Mp1 Mp2 Mn1 Mn2 f = a+b a=1 Mp1 b=1 Mp1

0 0 on on off off 1

0 1 on off off on 0 b=0 Mp2 a=1 Mp2

1 0 off on on off 0 f=0 f=0

1 1 off off on on 0 Mn1 Mn2 Mn1 Mn2

Sisteme cu circuite integrate digitale – Structuri logice CMOS 27

Porti logice CMOS – dimensionare

Exemplu de proiectare – porţi fundamentale cu 2 intrări

Inversor NAND2 NOR2

VDD VDD

Mp1 Mp2

VDD a Mp1

Mp

f b Mp2

Vin Vout

a Mn1 f

Mn

b Mn2

Mn1 Mn2

Sisteme cu circuite integrate digitale – Structuri logice CMOS 28

Porti logice CMOS – porti cu 3 intrari

Exemplu de proiectare – porţi fundamentale cu 3 intrări

Inversor VDD NAND3 VDD

NOR3

Mp1 Mp2 Mp3

a Mp1

VDD

b Mp2

f

Mp

a Mn1

Vin Vout c Mp3

f

Mn b Mn2

c Mn3

Mn1 Mn2 Mn3

Sisteme cu circuite integrate digitale – Structuri logice CMOS 29

Porti logice CMOS – exemple

Exemplul 1: f = ab + c

VDD

SI SAU

pull-down → 2 tranzistoare pull-down → 1 tranzistor a b

nMOS serie nMOS paralel cu grupul ab

pull-up → 2 tranzistoare serie c

pMOS paralel pull-up → 1 tranzistor

f

pMOS serie cu grupul ab

paralel a

c

Dimensionare b

pull-up → două tranzistoare serie pe oricare cale

→ se dublează geometria faţă de inversor (4W/L)

pull-down → două tranzistoare serie pe calea ab

→ se dublează geometria faţă de inversor (2W/L);

tranzistorul de pe calea c ca la inversor (W/L)

Sisteme cu circuite integrate digitale – Structuri logice CMOS 30

Porti logice CMOS – exemple

Exemplul 2: f = a∙(b + c)

VDD

SI SAU

pull-down → 1 tranzistor pull-down → 2 tranzistoare b

nMOS serie cu grupul (b+c) nMOS paralel a

paralel pull-up → 2 tranzistoare c

pull-up → 1 tranzistor pMOS pMOS serie

f

paralel cu grupul (b+c) serie

a

Dimensionare b c

pull-up → două tranzistoare serie pe calea (b+c) →

se dublează geometria faţă de inversor (4W/L);

tranzistorul de pe calea a ca la inversor (2W/L)

pull-down → două tranzistoare serie pe oricare cale

→ se dublează geometria faţă de inversor (2W/L)

Sisteme cu circuite integrate digitale – Structuri logice CMOS 31

Porti logice CMOS – exemple

Implementarea funcţiei în logică directă necesită conectarea unui inversor la ieşirea

funcţiei negate

AND2 OR2

VDD VDD

f = ab b

a f = a+b

Sisteme cu circuite integrate digitale – Structuri logice CMOS 32

Porti logice CMOS – exemple

Exemplul 3 - porţile SI-SAU şi SAU-SI cu 4 intrări

SI-SAU f1 = ab + cd

SAU-SI f2 = (a+b) ∙ (c+d)

VDD

VDD

a c

a b

b d

a b f2

f1 a b

a c

c d

b d

Sisteme cu circuite integrate digitale – Structuri logice CMOS 33

Porti logice CMOS – exemple

Exemplul

4 – Implementaţi funcţiile logice în tehnologie CMOS

1.

Sisteme cu circuite integrate digitale – Structuri logice CMOS 34

Porti de transmisie

Poarta de transmisie → circuit care permite sau inhibă transmiterea unui semnal între

două puncte de circuit, funcţie de un semnal de comandă

este realizată cu două MOS complementare

tranzistoarele sunt comandate cu semnale de control în antifază (A)

A

A

X Y X Y

A = 1: tranzistoarele conduc, Y = X

A = 0: tranzistoarele sunt blocate, Y = Z (impedanţă înaltă)

Sisteme cu circuite integrate digitale – Structuri logice CMOS 35

Logica de comutatie

Niveluri logice: ‘1’ → HIGH → VDD Nivel logic la ieşire înseamnă scurtcircuit

la alimentare

‘0’ → LOW → GND Cum evităm scurtcircuitul între VDD şi

GND?

‘1’ ‘0’ HZ

VDD VDD VDD VDD

VOUT VOUT VOUT VOUT

Sisteme cu circuite integrate digitale – Structuri logice CMOS 36

Aplicatii cu porti de transmisie

Buffer CMOS → conectarea în cascadă a unui inversor şi a unei porţi de transmisie

VDD

A

X Y X Y

Buffer CMOS → doua buffere comandate în antifază Y AX 0 AX1

X0

X0 Y

Y X1

A

X1

Sisteme cu circuite integrate digitale – Structuri logice CMOS 37

Aplicatii cu porti de transmisie

Bistabilul D → bloc logic fundamental în SCID

celula componentă a registrelor

celula de memorare

Structura → două MUX 2:1 într-o conexiune master-slave

ck = 0: Master urmăreşte D (QM = D), Slave menţine starea anterioară

tranziţie ck 0→1: Master menţine starea, Slave preia starea intermediară QM de la

master

D X0 X0 D Q

Y Y Q

QM

X1 X1

A A ck Q

Q

ck

Sisteme cu circuite integrate digitale – Structuri logice CMOS 38

Obiectivele proiectarii circuitelor logice CMOS

Poarta ideală: rapidă şi cu consum mic

Proiectarea SCID trebuie să urmărească o viteză de lucru cât mai mare, putere

consumată cât mai mică şi aria circuitului de asemenea cât mai mică

Power-delay product (PDP) → se defineşte ca o masură a calităţii circuitelor logice

care lucrează în comutaţie, şi reprezintă produsul dintre timpul de întârziere şi puterea

consumată

PDP este constant pentru o tehnologice şi topologie dată :

pentru scăderea timpului de propagare, tranzistoarele sunt redimensionate prin

mărirea lăţimii canalului

creşte suprafaţa tranzistorului, ceea ce duce la creşterea curentului şi a puterii

consumate

produsul celor două mărimi (PDP) rămâne constant

Sisteme cu circuite integrate digitale – Structuri logice CMOS 39

Familii de circuite logice CMOS

CMOS 4000 – prima familie CMOS

structură simplă a porţilor fundamentale

putere consumată redusă

viteză de lucru redusă

interfaţare dificilă cu circuitele TTL

CMOS HC (High Speed CMOS) şi HCT (TTL Compatible)

viteză ridicată, compatibilitate TTL: 74LLLnnn (74 – cod Texas Instruments din gama

comercială, 54 – gama militară, nnn – funcţia circuitului, LLL - familia)

CMOS VHC (Very High Speed), VHCT (TTL Compatible)

frecvenţă de lucru dublă faţă de generaţiile anterioare

CMOS FCT (Fast CMOS, TTL Compatible)

CMOS FCT-T (with TTL VOH)

cel puţin la fel de rapide ca şi TTL, consum redus şi compatibile TTL (VOH<5V, compatibil

cu nivelul HIGH TTL)

Sisteme cu circuite integrate digitale – Structuri logice CMOS 40

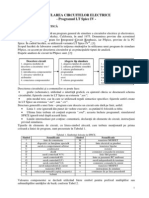

Familii de circuite logice CMOS

Familia de circuite CMOS

Parametru UM HC HCT VHC VHCT

Timp de propagare tipic ns 9 10 5,2 5,5

Curent de alimentare μA 2,5 2,5 5 5

Putere statică disipată μW 12,5 12,5 25 25

Putere dinamică disipată mW/MHz 0,55 0,38 0,48 0,43

Curent rezidual de intrare μA ±1 ±1 ±1 ±1

Capacitate maximă de intrare pF 10 10 10 10

Tensiune de intrare la nivelul LOW VIL max V 1,35 0,8 1,35 0,8

Tensiune de intrare la nivelul HIGH VIL min V 3,85 2,0 3,85 2,0

Curent de ieşire la nivelul LOW mA 0,02 0,02 0,05 0,05

Curent de ieşire la nivelul HIGH mA -0,02 -0,02 -0,05 -0,05

Tensiune de ieşire la nivelul LOW V 0,1 0,1 0,1 0,1

Tensiune de ieşire la nivelul HIGH V 4,4 4,4 4,4 4,4

Sisteme cu circuite integrate digitale – Structuri logice CMOS 41

Probleme propuse

Probleme propuse

1. Determinaţi rezistenţa in conducţie unei porţi de transmisie realizată cu două tranzitoare conectate in paralel: unul cu canal n si

altul cu canal p. Ambele au dimensiuni minime : LN=1µ si WN =1µ, iar LP=1µ si WP =1µ.

2. Calculati puterea statică consumată de un tranzistor NMOS. Dimensiunile tranzistorului sunt W N / LN =0.1µ /0.05µ = 2/1.

Curentul de scurgere de subprag este de 10nA/μm pentru fiecare transistor. Curentul de scurgere din grilă este de 5nA/ μm.

Tensiunea de alimentare este 1.2V.

Curentul de scurgere de subprag consumat de un tranzistor

Curentul de scurgere din grilă consumat de un tranzistor

Puterea statică consumată de un tranzistor este:

Sisteme cu circuite integrate digitale – Structuri logice CMOS 42

Probleme propuse

Probleme

propuse

3. Calculaţi puterea statică consumată de o memorie de 1GB avand celulele realizate cu tranzistoare NMOS. Dimensiunile

tranzistoarelor sunt WN / LN =0.1µ /0.05µ = 2/1. Curentul de scurgere de subprag este de 10nA/μm pentru fiecare transistor.

Curentul de scurgere din grilă este de 5nA/ μm. Tensiunea de alimentare este 1.2V.

Curentul de scurgere de subprag consumat de un miliard de tranzistoare

Curentul de scurgere din grilă consumat de un miliard de tranzistoare

Puterea statică consumată este:

Sisteme cu circuite integrate digitale – Structuri logice CMOS 43

Probleme propuse

Probleme propuse

4. Calculaţi puterea disipată dinamică datorată incărcării / descărcării unui condensator pentru un inversor CMOS in tehnologie de

0.25 µm, care are o capacitate parazită de sarcină de 6 fF, tensiune de alimentare de 2.5 V si frecvenţa maximă permisă de timpul de

propagare mediu al inversorului egal cu 80 ps.

Frecvenţa maximă permisă este

Puterea disipată dinamică

5.Calculaţi puterea dinamică datorată incărcării / descărcării capacitătii de sarcină a celulelor de memorie (un miliard de celule).

Frecvenţa de lucru este de 1GHz. Capacitatea parazită de sarcină a unei celule este de 6 fF iar tensiunea de alimentare 1.2V. Factorul

de activitate al celulelor este 0.02.

Se observă că puterea statică este de circa 16% din cea dinamică, ceea ce reprezintă un procent important.

Sisteme cu circuite integrate digitale – Structuri logice CMOS 44

Probleme propuse

Probleme propuse

6. Calculati puterea dinamică datorată curentilor de scurt-circuit pentru un inversor CMOS in tehnologie de 0.25 um, care are o

capacitate parazită de sarcină de 1.6 fF, tensiune de alimentare de 5 V si frecvenţa maximă egală cu 1 GHz.

Această valoare este mult mai mică decat cea datorată incărcării condensatoarelor parazite, motiv pentru care se neglijează in

calcule.

7. Recalculati puterea dinamică datorată curentilor de scurt-circuit pentru un inversor CMOS in tehnologie de 0.25 um, care are o

capacitate parazită de sarcină de 1.6 fF, tensiunea de alimentare de 5 V si frecvenţa maximă egală cu 1 GHz.

Sisteme cu circuite integrate digitale – Structuri logice CMOS 45

Probleme propuse

Parametrii tranzistoarelor MOS cu canal lung ( L=W= 1µm) si tensiune de alimentare VDD=5V

Parametru NMOS PMOS

Tensiune prag VTHN = 800 mV VTHP = 900 mV

Grosime oxid Tox=200 A Tox=200 A

Conductibilitate canal KN=120µA/V2 KP=40µA/V2

Capacitate oxid pe Cox=1.75fF/µm2 Cox=1.75fF/µm2

unitate

Curent conductie liniara

Curent stare OFF

Parametrii tranzistoarelor MOS cu canal scurt ( L=W=50nm) si tensiune de alimentare VDD=1V

Parametru NMOS PMOS

Tensiune prag VTHN = 280 mV VTHP = 280 mV

Grosime oxid Tox=14 A Tox=14 A

Capacitate oxid pe Cox=25fF/µm2 Cox=25fF/µm2

unitate

Curent conductie IDSon = 600 µA/µm IDSon =300 µA/µm

liniara

Curent stare OFF IDSoff =7.1 nA/µm IDSoff =10 nA/µm

Sisteme cu circuite integrate digitale – Structuri logice CMOS 46

S-ar putea să vă placă și

- UndeDocument69 paginiUndeAndreea ChiriluşÎncă nu există evaluări

- Subiecte Examen Dispozitive ElectroniceDocument1 paginăSubiecte Examen Dispozitive ElectroniceDoru PascaÎncă nu există evaluări

- Algoritmi de ClasificareDocument6 paginiAlgoritmi de Clasificareion1848Încă nu există evaluări

- Analiza Circuitelor ElectroniceDocument128 paginiAnaliza Circuitelor ElectroniceMarius Viorel100% (1)

- Curs 07 Sisteme TV ColorDocument11 paginiCurs 07 Sisteme TV ColorAlex AlexaÎncă nu există evaluări

- Proiect DidacticDocument9 paginiProiect DidacticLuciaCroitoriÎncă nu există evaluări

- ModuloDocument28 paginiModuloCezar GabrielÎncă nu există evaluări

- Modulaţia PSKDocument5 paginiModulaţia PSKVlad CastraveteÎncă nu există evaluări

- Lucrare 3 Laborator ASCN IIDocument5 paginiLucrare 3 Laborator ASCN IIperyplatipuÎncă nu există evaluări

- Bellman FordDocument515 paginiBellman FordOana Stefania GusuÎncă nu există evaluări

- SNR Cap 7 PDFDocument79 paginiSNR Cap 7 PDFRadu ConstantinescuÎncă nu există evaluări

- Circuite Pentru Conversia DatelorDocument5 paginiCircuite Pentru Conversia DatelorAriadna OnisimÎncă nu există evaluări

- CIA Culegere de ProblemeDocument70 paginiCIA Culegere de ProblemeLaura UrsicaÎncă nu există evaluări

- Electronica Musat CarmenDocument42 paginiElectronica Musat CarmencernatandÎncă nu există evaluări

- Proiect IDocument26 paginiProiect IDorin LunguÎncă nu există evaluări

- Curs Reglarea in CascadaDocument20 paginiCurs Reglarea in Cascadaarnesss100% (1)

- m1 Bazele Electronicii Analogice Cl10aDocument3 paginim1 Bazele Electronicii Analogice Cl10asevastian marius ion100% (1)

- Lab - 4 - Tranzistorul Cu Efect de Camp TEC-J - 2020Document5 paginiLab - 4 - Tranzistorul Cu Efect de Camp TEC-J - 2020Olesea Nicolai100% (1)

- Subiecte EME Examen PDFDocument87 paginiSubiecte EME Examen PDFSorin Constantin Oportov100% (1)

- Fisa de Lucru Recapitulativa Dispozitive HardwareDocument3 paginiFisa de Lucru Recapitulativa Dispozitive HardwareCristina CiutaÎncă nu există evaluări

- Fisa de LucruDocument2 paginiFisa de LucruIoana-CezaraBucataruÎncă nu există evaluări

- C04-Adresarea Memoriei 2016Document16 paginiC04-Adresarea Memoriei 2016Paul TodericÎncă nu există evaluări

- Circuitul RLC SerieDocument1 paginăCircuitul RLC SerieATP_101Încă nu există evaluări

- Filtre AnalogiceDocument49 paginiFiltre AnalogiceAmirAghdamÎncă nu există evaluări

- Comunicatii Cu Modulatie LiniaraDocument26 paginiComunicatii Cu Modulatie Liniaramatrionel100% (1)

- 03 Realizarea FIR IIR FD v2 PDFDocument12 pagini03 Realizarea FIR IIR FD v2 PDFVictor CufliucÎncă nu există evaluări

- Noţiuni Introductive in PspiceDocument54 paginiNoţiuni Introductive in PspiceRaduÎncă nu există evaluări

- Reactia in Amplificatoare. Particularitatile Reactiei Pozitive (Întrebarea 10)Document5 paginiReactia in Amplificatoare. Particularitatile Reactiei Pozitive (Întrebarea 10)Inna MunteanÎncă nu există evaluări

- Microcontrolerul 80C51Document28 paginiMicrocontrolerul 80C51Lacatus ValentinÎncă nu există evaluări

- Auxiliar CurricularDocument63 paginiAuxiliar CurricularDaniela ChelbeaÎncă nu există evaluări

- Circuite Logice FundamentaleDocument13 paginiCircuite Logice FundamentaleCătălin BumbÎncă nu există evaluări

- CID 05 Familii de Circuite LogiceDocument27 paginiCID 05 Familii de Circuite LogiceYanBÎncă nu există evaluări

- Masurarea Puterii În CCDocument13 paginiMasurarea Puterii În CCAndon AlinÎncă nu există evaluări

- ListaFacultati - Ro Subiecte Admitere Academia Tehnica Militara Bucuresti Matematica Fizica 2008Document4 paginiListaFacultati - Ro Subiecte Admitere Academia Tehnica Militara Bucuresti Matematica Fizica 2008ListaFacultati.ro100% (1)

- Divizoare PutereDocument19 paginiDivizoare PutereRamona ScripcaruÎncă nu există evaluări

- C06 - Semnale Neperiodice PDFDocument20 paginiC06 - Semnale Neperiodice PDFCoSty CSyÎncă nu există evaluări

- Probleme PDFDocument115 paginiProbleme PDFDragos AlexandruÎncă nu există evaluări

- Aplicatii PDFDocument59 paginiAplicatii PDFJesse MeyerÎncă nu există evaluări

- Componente Pasive Si ActiveDocument11 paginiComponente Pasive Si Activeinsane turtlesÎncă nu există evaluări

- Curs 7 13Document70 paginiCurs 7 13Băcă SergiuÎncă nu există evaluări

- Memorii SemiconductoareDocument39 paginiMemorii Semiconductoarezalood100% (1)

- Curs TSTMDocument17 paginiCurs TSTMCiprianSilvestruÎncă nu există evaluări

- Rezolvari Teme de Curs PDFDocument16 paginiRezolvari Teme de Curs PDFPetruta RoxanaÎncă nu există evaluări

- Simularea Circuitelor Electrice - LTSpice Facultatea UPTDocument4 paginiSimularea Circuitelor Electrice - LTSpice Facultatea UPTDaniel-Costel DamianÎncă nu există evaluări

- Lucrarea 1 - Masurarea TemperaturiiDocument12 paginiLucrarea 1 - Masurarea TemperaturiiLorand BecsekÎncă nu există evaluări

- Verilog HDL CoursesDocument271 paginiVerilog HDL CoursesToderean AlexandruÎncă nu există evaluări

- Introducere Semnale Si Sisteme UPT ETcTIDocument30 paginiIntroducere Semnale Si Sisteme UPT ETcTISilvan MotorcaÎncă nu există evaluări

- CIA - Oscilator de Semnal Dinti de Ferastrau'Document12 paginiCIA - Oscilator de Semnal Dinti de Ferastrau'Nae AdrianÎncă nu există evaluări

- Realizarea Bistabilelor RS, D, T În Baza Bistabilului de Tip JKDocument4 paginiRealizarea Bistabilelor RS, D, T În Baza Bistabilului de Tip JKAriadna OnisimÎncă nu există evaluări

- Wireless 03ar-62sDocument61 paginiWireless 03ar-62sDumitru MihaiÎncă nu există evaluări

- Probleme Ingineria Reglarii AutomateDocument13 paginiProbleme Ingineria Reglarii AutomateBogdan TanasaÎncă nu există evaluări

- L2 CD QPSK 16QAMnouDocument26 paginiL2 CD QPSK 16QAMnouTatarus Marius MarianÎncă nu există evaluări

- Circuite de Polarizare Probleme Circ Simplu de PolarizareDocument4 paginiCircuite de Polarizare Probleme Circ Simplu de Polarizarewhitecloud2921Încă nu există evaluări

- 5a-Interfete Seriale - Codificarea Datelor PDFDocument14 pagini5a-Interfete Seriale - Codificarea Datelor PDFAndrei CiobanasuÎncă nu există evaluări

- Ex de Stat Raspuns 2012Document99 paginiEx de Stat Raspuns 2012GrecuAndrianÎncă nu există evaluări

- Curs 1 Semnale in TelecomunicatiiDocument52 paginiCurs 1 Semnale in TelecomunicatiiOvidiuCirimpei100% (1)

- Ce Este PUNTEA H - Electronic ŞtefanDocument7 paginiCe Este PUNTEA H - Electronic ŞtefanAlex FierăscuÎncă nu există evaluări

- Aplicatii Ale Procesoarelor de Semnal in ComunicatiiDocument143 paginiAplicatii Ale Procesoarelor de Semnal in ComunicatiiDaniel Anton100% (1)

- DO TeorieDocument10 paginiDO TeorieNedelcu George AurelÎncă nu există evaluări

- 03 Structuri Logice CmosDocument38 pagini03 Structuri Logice CmosAlina JumoleaÎncă nu există evaluări

- Laborator 1Document21 paginiLaborator 1AndreeaÎncă nu există evaluări

- Laborator 2Document18 paginiLaborator 2AndreeaÎncă nu există evaluări

- l3 AscDocument8 paginil3 AscAndreeaÎncă nu există evaluări

- l2 AscDocument8 paginil2 AscAndreeaÎncă nu există evaluări

- l1 AscDocument8 paginil1 AscAndreeaÎncă nu există evaluări

- 03 Structuri Logice CmosDocument46 pagini03 Structuri Logice CmosAndreeaÎncă nu există evaluări

- 02 Tranzistorul MOSDocument34 pagini02 Tranzistorul MOSAndreeaÎncă nu există evaluări

- 02 Tranzistorul MOSDocument34 pagini02 Tranzistorul MOSAndreeaÎncă nu există evaluări

- 01 SCID IntrodDocument21 pagini01 SCID IntrodAndreeaÎncă nu există evaluări

- 01 SCID IntrodDocument21 pagini01 SCID IntrodAndreeaÎncă nu există evaluări